Устройство для приема сигналов с частотно-фазовой модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи . Цель изобретения - повышение достоверности приема. Устройство содержит частотньш детектор 1, линию 2 задержки, интеграторы 3, 8, блок 4 вьзделения несущей, фазовый детектор 5, АЦП 6, 10, генератор (Г) 7 частот, . ключ 9. В устройство введены регистры 11, 12, сумматоры 13, 14 по модулю два, мажоритарные блоки 15, 17, Г 16 синхрослова и элемент И 18. При этом сигнал цикловой синхронизации выдается с выхода элемента И 18 только в случае одновременного выделения синхрослов из двух подканалов приема, что повышает надежность цикловой синхронизации . 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН (gg 4 Н 04 L 27/22

„- °

ollHcAHHE изоБ кткниа, К А ВТОРСНОМЪ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1262744 (21) 4227592/24-09 (22) 13.04.87 (46) 23.10.88. Бюл. Р 39 (72) В.П.Бережной, M.À.Èâåíoâ, И.И.Сватовский и И.А.Хабахпашев (53) 621.394.62(088,8) (56) Авторское свидетельство СССР

9 1262744, кл. H 04 T. 27/22, 1985. (54) УстРойство Дли пРикмА сиг 1Алов

С ЧАСТОТНО-ФАЗОВОЙ МОДУЛЯЦИЕЙ (57) Изобретение относится к радиосвязи. Цель изобретения - повышение достоверности приема. Устройство со„.ЯО„„1432798 А 2 держит частотный детектор 1, линию 2 задержки, интеграторы 3, 8, блок 4 выделения несущей, фазовый детектор

5, АЦП 6, 10, генератор (Г) 7 частот,, ключ 9. В устройство введены регистры 11, 12, сумматоры 13, 14 по модулю два, мажоритарные блоки 15, 17, Г 16 синхрослова и элемент И 18. При этом сигнал цикловой синхронизации выдается с выхода элемента И 18 только в случае одновременного выделения синхрослов из двух подканалов приема, что повышает надежность цикловой синхронизации. 1 ил.

98 (3) 1 14327

Изобретение относится к радиосвя1 зи, может использоваться в высокоскоростных радиосистемах передачи информации и является усовершенствованием известного изобретения по авт. св.

В 1262744

Цель изобретения — повышение достоверности приема.

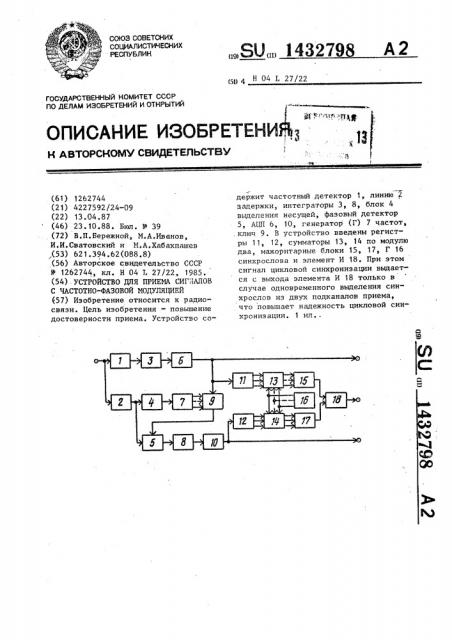

На чертеже представлена структурная электрическая схема предлагаемого устройства, Устройство для приема сигналов с частотно-фазовой модуляцией содержит частотный детектор 1, линию 2 задерж-15 ки, первый интегратор 3, блок 4 выделения несущей, фазовый детектор 5, первый аналого-цифровой преобразователь 6 (АЦП), генератор 7 частот, второй интегратор 8, ключ 9, второй 20

АЦП 10, первый и второй регистры 11, 12, первый и второй сумматоры 13 и

14 по модулю два, первый мажоритарный блок 15, генератор 16 синхрослова, второй мажоритарный блок 17, элемент 25

И 18.

Устройство работает следующим образом.

На его вход поступает частотнофазоманипулированный (ЧФМ) сигнал, ко30 который можно представить в виде ь

8 (t) = A з пГы,t + $ du(t)

- Ч (е) +, 3, (1) где А — амплитуда огибающей сигнала; 35 .4) = 2 fp и Q — круговая частота и начальная фаза несущего колебания; йы () — закон изменения частоты несущего колебания; 40 д Ц (t) — закон изменения фазы сигнала.

С входа устройства ЧФМ-сигнал поступает на вход частотного детектора 1 и линию 2 задержки. На выходе частотного детектора 1 по результатам при-45 ема элемента сигнала за тактовый интервал формируется напряжение, которое является функцией отклонения значения частоты принятого элемента сигнала fс от частоты настройки час- 50 тотного детектора 1 f< 1

Фч4(@

Данное напряжение интегрируется за время такта первым интегратором 3, передаточная функция которого опреде-55 ляется выражением

U„(t) = — †. 1 Цчд(сие.

1 где — постоянная времени первого интегратора 3.

Напряжение с выхода первого интегратора 3 поступает на вход первого

АЦП Ь, который преобразует данное напряжение в код, соответствующий частоте принятого элемента сигнала.

Данный код поступает на выход устройства.

Линия 2 задержки производит задержку ЧФМ-сигнала на время, равное длительности обработки элемента сигнала в частотном подканале. Задержанный на время t> сигнал поступает на вход блока 4 вьделения несущей, в котором производится подстройка внутреннего опорного генератора по частоте принятого элемента сигнала. Опорное колебание поступает на вход генератора 7 частот, который формирует из него сетку опорных колебаний, необходимых для когерентной обработки в фазовом подканале. Данные опорные колебания поступают на сигнальные входы ключа 9, который под воздействием поступающего на его управляющий вход кода пропускает на вход фазового детектора 3 опорное колебание с частотой, равной частоте поступающего на его другой вход элемента сигнала.

На выходе фазового детектора 5 форми-. руется напряжение, являющееся функцией разности фаз принятого и опорного сигналов:

Пфд = Ффд (с (оп ) (4)

Данное напряжение выделяется вторым интегратором 8 и поступает на вход второго АЦП 10, который преобразует его в код, соответствующий фазе принятого элемента сигнала.

Таким образом, с выходов первого

6 и второго 10 АЦП вьдаются последовательности двоичных символов, передаваемые соответственно по частотному и фазовому подканалам. Данные последовательности поступают на выходы устройства, а также на первый и второй регистры f1 и 12, которые произ- водят последовательную запись и параллельное считывание поступающих символов. Символы с и выходов первого и второго регистров 11 и 12 посту" лают на соответствующие входы перво-, го и второго сумматоров 13 и 14 по модулю два, которые выполняют операцию сложения по модулю два п-разрядных чисел, поступающих из частотного

1432798 подканалов приема, что повышает надежность цикловой синхронизации.

Формула и з обре т е н и я

Составитель А.Москевич

Техред А.Кравчук Корректор Л.Патай

Редактор Е.Папп

Заказ 5466/56 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва; Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 и фазового подканалов, и п-разрядного синхрослова, поступающего от генера, тора 16 синхрослова. Результаты сложения с инверсных выходов первого и второго сумматоров 13 и 14 по модулю два поступают на входы первого и второго мажоритарных блоков 15 и 17, которые вьщают на выходах сигналы логической " 1" в случае, если количест-10 во единиц в поступившей последовательности не меньше числа М, значение которого определяется строгостью требований к точности вьщеления синхрослова и в пределе становится равным 15 и (в этом случае мажоритарный элемент можно заменить элементом И) .

Сигналы с выходов первого и второго мажоритарных блоков 15 и 17 поступают на элемент И 18, который выда-20 ет сигналы логической "1" в случае единичных сигналов с выходов первого и второго мажоритарных блоков 15 и 17 (при одновременном вьщелении синхрослов из обоих подканалов) и логичес- 25 кого "0" — в случае, если на выходе хотя бы одного мажоритарного блока 15 или 17 будет нулевой сигнал (при невьщелении синхрослова хотя б» из одного подканала). 30

Таким образом, сигнал цикловой синхронизации выдается с выхода элемента И 18 только в случае одновременного вьщеления синхрослов из двух

Устройство для приема сигналов с частотно-фазовой модуляцией .по авт. св. У 1262744, о т л и ч а ю щ е е— с я тем, что, с целью повышения достоверности приема, введены.два мажоритарных блока, генератор синхрослова, два регистра, два сумматора по модулю два и элемент И, входы которого соединены с выходом первого мажоритарного блока, к входам которого подключены выходы первого сумматора по модулю два, и с выходом второго мажоритарного блока, к входам которого подключены выходы второго сумматора по модулю два, одни входы которого соединены с выходами генератора синхрослова и с одними входами первого сумматора по модулю два, к другим входам которого подключены вьжоды первого регистра, вход которого соединен с выходом первого аналого-цифрового преобразователя, при этом выход второго аналого-цифрового преобразователя подключен к входу второго регистра, выходы которого соединены с другими входами второго сумматора по модулю два, а выход элемента И является выходом цикловой синхронизации устройства.