Регулятор с переменной структурой

Иллюстрации

Показать всеРеферат

Изобретение относится к системам автоматического регулирования технологических параметров, например давления, в условиях ждущего режима и может быть использовано в химической , нефтяной, газовой и других отраслях промышленности. Цель изобретения - повьппение быстродействия и качества регулирования. Регулятор содержит датчик 1, первый 2, второй 3 и третий 4 задатчики, первый 5 и второй 6 алгебраические сумматоры, первый 7, второй 8, третий 9 и четвертый 10 блоки переключения, пороговое устройство 11, пропорциональное звено 12, интегрирующее звено 13, таймер 14, элемент ИЛИ 15, исполнительное устройство 16. 1 ил. (О (Л

СОЮЗ СОВЕТСКИХ

С01.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

1434401 А 1 (51)4 G 05 В 1E/01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 4226013/24-24 (22) 07.04.87 (46) 30.10 88. Бюл. И 40 (72) В.И.дедухна, Н.В.Ипполитов и Н.В.Подорин (53) 62-50(088.8) (56) Эрриат П. Регулирование производственных процессов. М.: -Энергия, 1967, Авторское свидетельство СССР

У 928299, кл. С 05 В 11/01, 1980. (54) РЕГУЛЯТОР C ПЕРЕИЕННОИ СТРУКТУРОЙ (57) Изобретение относится к системам автоматического регулирования технологических параметров, например давления, в условиях ждущего режи- ма и может быть использовано в химической, нефтяной, газовой и других отраслях промышленности. Цель изобретения — повышение быстродействия и качества регулирования. Регулятор содержит датчик 1, первый 2, второй 3 и третий 4 задатчнки, первый 5 и второй 6 алгебраические сумматоры, первый 7, второй 8, третий 9 и четвертый 1О блоки переключения, пороговое устройство (1 пропорциональное звено 12, интегрирующее звено 13, таймер

14, элемент ИЛИ 15, исполнительное устройства 16. 1 ил °

1434401

Изобретение относится к системам автоматического регулирования технологических параметров, например давления в условиях "ждушего" режима и может быть использовано в химической, нефтяной, газовой и других отраслях промьппленности.

Цель изобретения — повьппение быстродействия и качества регулирования.

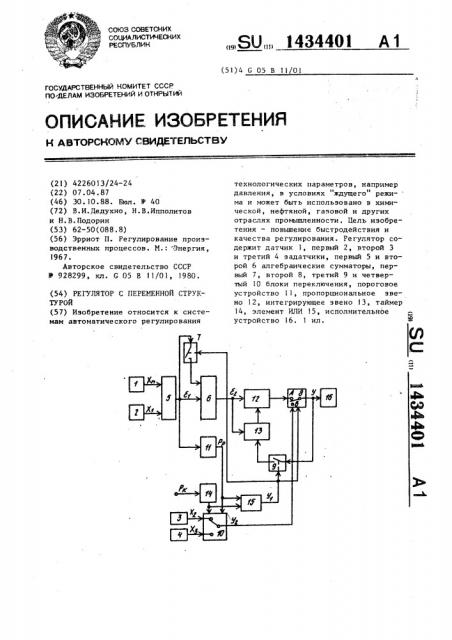

На чертеже представлена принципиальная схема регулятора.

Регулятор с переменной структурой содержит датчик 1, первый 2, второй

3 и третий 4 задатчики, первый 5 и второй 6 алгебраические сумматоры, первый 7, второй 8, третий 9 и четвертый 10 блоки переключения, пороговое устройство 11, пропорциональное звено 12, интегрирующее звено 13, таймер 20

14, элемент ИЛИ 15, исполнительное устройство 16, Регулятор работает следующим образом.

Сигналы от датчика l и первого эа- 25 датчика 2 поступают на входа первого алгебраического сумматора 5, где происходит их алгебраическое сложение:

Х вЂ” Х

1 П

Пороговое устройство 11 настраивается таким образом, чтобы его срабатывание происходило при значении большем, чем 1 при заданном расссги !1 ласовании между Х, и Х, для ждущего режима. Таким образом, рассогласование f для "ждущего" режима, пройдя 1 без изменений второй алгебраический сумматор 6 (первый блок 7 переключения находится в разомкнутом состоянии), поступит на первые информационные входы пропорционального 12 и интегрирующего 13 звеньев, что приведет к установке исполнительного устройства 16 в одно из крайних положений, в зависимости от назначения регулятора и типа исполнительного устройства (второй блок 8 переключения находится в положении А). Если исполнительное устройство 16 находит ся в закрытом состоянил при максимальном уровне сигнала (У = ь1акс ) ° на выходе второго блок". 8 переключения будет сигнал 7 = 7,„, . При воздействии изменяющегося возмущения

55 рассогласование F, на выходе первого алгебраического сумматора 5 возрастает, что приведет к срабатыванию . порогового устройства ll и формированию на его выходе командного сигнала Р, который поступит на первый командный вход четвертого блока 10 переключения и элемента ИЛИ 15.

Таким образом, при срабатывании порогового устройства 11 (наличие сигнала Р ) и отсутствии внешнего командного сигнала на выходе четвертого блока 10 переключения формируется сигнал Yg = Х, на выходе элемента

ИЛИ 15 формируется сигнал Y = 1, который поступит на управляющий вход первого блока 7 переключения и осуществит подключение сигнала E на второй вход второго алгебраического сумматора б, что приведет к отсутствию рассогласования íà его выходе

F - =О, Одновременно произойдет переключение выходного сигнала второго блока 8 переключения в положение Б, т.е, произойдет подк:::ючение входа исполнительчого устрой.ства 16 к выходу четвертого блока 1О переключения, на котором будет сихнал Х .

Таким образом произойдет быстрое перемещение исполнительного устройства

16 в новое положение, которое обеспечит компенсацию поступившего возмущения. При уменьшении рассогласования („ поступит на вход интегрирующего 13 и пропорционального 12 звеьтьев, выходной сигнал пропорциональ ного звена 12 поступит на вход исполнительного устройства 16, а выходной сигнал второго блока 8 переключения не будет поступать на второй информационный вход интегрирующего звена

13. В дальнейшем компенсация поступившего возмущения будет осуществляться пропорциональным 12 и интегрирующим 13 звеньями, При поступлении значительного возмущения в канале внешнего командного сигнала сформируется сигнал P = 1, который через таймер 14 поступает на вторые входы элемента ИЛИ 15 и четвертого блока 10 переключения.

Таким образом,, при чаличии внешнего командного сигнала Р на выходе блока 10 переключения формируется сигнал Y = Х, (при наличии одновременно на входе блока 10 переключения сигнала Рр приоритет имеет внешний командный сигнал Р, и на выходе бло 9 ка 10 переключения формируется сигнал Y y = Х1) . При этом на выходе элемента ИЛИ 15 формируется сигнал У, l, который приведе-. к переключению

1434401

Формула изобретения

Составитель M. Никитина.

Техред М. Ходанич Корректор В. Гирняк

Редактор М.Бандура

Тираж 866 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5552/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 первого 7, второго 8 и третьего 9 блоков переключения, т.е, произойдут те же переключения, что и при появлении сигнала Pp = 1. Отличие состоит в том, что в данной ситуации на выходе четвертого блока 10 переключения будет сигнал Y> = Х . В отличие от

Х,, сигнал Х соответствует большей степени открытия исполнительного устройства 16, обеспечивающей .компенсацию данного возмущения за определенный промежуток времени, устанавливаемый таймером 14, по истечении которого на выходе таймера 14 формируется

Рт = О, что приводит блок 10 переключения в исходное состояние. При этом на выходе элемента ИЛИ 15 формируется сигнал Y, = О, и первый 7, второй

8 и третий 9 блоки переключения переходят в исходное состояние, и включаются в .работу пропорциональное 12 и интегрирующее 13 звенья. При появлении сигнала Pð = 1 на выходе элемента ИЛИ 15 формируется сигнал У

:=1, на выходе блока 10 переключения сигнал Y q Х . Работа устройства в этом случае аналогична описанной.

При поступлении одновременно сигналов Р и Р„ высший приоритет имеет сигнал Рк.

Регулятор с переменной структурой, содержащий датчик и первый задатчик, выход каждого иэ которых соединен соответственно с первым и вторым входами первого алгебраического сумматора, второй задатчик и исполнительное устройство, о т л и ч а ю щ и .й с я тем, что, с целью повышения быстродействия и качества регулирования, в него введены четыре блока переключения, второй алгебраический сумматор, пропорциональное звено, интегрирующее звено, третий эадатчик, пороговое устройство, таймер, вход которого является входом по внешнему возмущению регулятора, элемент ИЛИ, причем выход первого сумматора подключен к информационному входу первого блока переключения, к первому входу второго алгебраического сумматора,,соединенного вторым входом с выходом первого блока переключения, а выходом — с первыми информационными входами пропорционального и интегрирующего звеньев, и через пороговое устройство — к первому командному входу четвертого блока переключения и первому входу элемента ИЛИ, выход которого подключен к управляющим входам первого, второго и третьего блоков переключения, выход таймера соединен

2Б с вторым входом элемента ИЛИ и с вторым командным входом четвертого блока переключения, первый и второй информационные входы которого подключены соответственно к выходам второго и третьего задатчиков, а выходк первому информационному входу второго блока переключения, второй информационный вход которого соединен с выходом пропорционального звена, ЗБ а выход — с входом исполнительного устройства и с информационным входом третьего блока переключения, подсоединенного выходом к второму информационному входу интегрирующего звена, выход которого соединен с вторым информационным входом пропорционального звена.