Цифровой линейный интерполятор

Иллюстрации

Показать всеРеферат

Изобретение относится к автома тике и вычислительной технике и может быть использовано в вьтодных графических устройствах с линейными и матричными органами регистрации, в станках с программным управлением, в которых применяют линейные или матричные исполнительные устройства. Цель изобретения - повышение быстродействия интерполятора. Цифровой линейный интерполятор обеспечивает наа W хождение многоразрядных приращений, которыми аппроксимирован заданный отрезок прямой, за один интерполяционньй такт. Он содержит блок управления 1, регистры 2, 3 координатных приращений, блок 4 постоянной памяти, двоичные умножители 5, 6, триггеры 7, 8, регистры 9 и 10. Значения младших разрядов М-разрядных координатных приращений запоьтнаются в регистрах 2 и 3. M-N старших разрядов координатных приращений поступают на адресные входы блока 4 постоянной памяти, с выходов которого 2 - разрядов многоразрядных приращений записываются в регистры 9 и 10, Младишй 3, разряд 2 -разрядных прираще шй формируется N-разрядным двоичным умножителем 3 и N-разрядным двоичным умножителем 6, на информационные входы которых с выходов регистров 2 и 3 2 поступают значения N младших разрядов координатных приращений Лх и 4у соответственно . Блок 1 управления предназначен для синхронизации работы интерполятора, 1 з,п. ф-лы, 5 ил. ОЭ О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

<511 4 ?? 05 ?? 19!!8 >

i L

Y рог.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 4229268/24-24 (22) 13.04,87 (46) 30.10.88. Бюл. Иг 40 (71) Винницкий политехнический институт (72) А.М,Петух, А.Н;Романюк, В.П.Майданюк, Д.Т,Ободник и И.ПвЛоянич (53) 621.503.55 (088,8) (56) Авторское свидетельство СССР

У. 344415, кл. 0 05 В 19/18, 1972.

Авторское свидетельство СССР

1 395839, кл. 6 06 F 15/20, 1973. (54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР (57) Изобретение относится к автома тике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, в станках с программным управлением, в которых применяют линейные или матричные исполнительные устройства.

Цель изобретения — повышение быстродействия интерполятора. Цифровой линейный интерполятор обеспечивает на„„SU„„1434406 А 1 хождение многоразрядных приращений, которыми аппроксимирован заданный отрезок прямой, за один интерполяционный такт, Он содержит блок управления 1, регистры 2, 3 координатных приращений, блок 4 постоянной памяти, двоичные умножители 5, 6, триггеры

7, 8, регистры 9 и 10. Значения младших разрядов М-разрядных координатных приращений запоминаются в регистрах

2 и Э, М-И старших разрядов координатных приращений поступают на адресные входы блока 4 постоянной памяти, с выходов которого 2 — 1 разрям-ч дов многоразрядных приращений записываются в регистры 9 и 10. Младший щ разряд ? + -разрядных приращейий м рг формируется N-ревряримм двоичимм ум- Я ножителем 5 и И-разрядным двоичным умножителем 6, на информационные входы которых с выходов регистров 2 и 3 ф поступают значения N мпадпих разрядов координатных приращений д х и dy соответственно. Блок 1 управления предназначен для синхронизации работы интерполятора. 1 3.ë. A-лы, 5 ил.

fit>

4ь

1434406

Изобретение относится к автоматике H вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, гтан5 ках с числовым программным управлением, в которых использованы линейные или матричные исполнительные op— ганы,, Цель изобретения — повышение быстродействия.

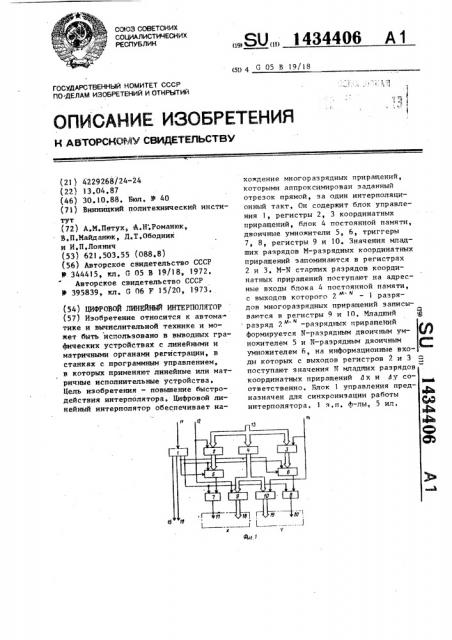

На фиг. 1 представлена структурная схема предлarаемого цифровorо линейного интерполятора; на фиг. 2 — функ- 15 циональная схема реализации блока уп1 равления; на фиг. 3 — временная диаграмма работы интерполятора; на фиг. 4 — распределение управляющих воздействий по отношению к уровням сигнала на выходе элемента И 24: на фиг. 5 — временная диаграмма работы четырехразрядного двоичного умножителя, Цифровой линейный интерполя тор содержит блок 1 управления, первый

2 и второй 3 регистры координатных приращений, блок 4 постоянной памяти, первый 5 и второй 6 двоичные умножители первый 7 и второй 8 триггеры„ первый 9 и второй 1О регистры (регистры многоразрядных приращений),. входы 11-14, выходы 15-20 интерполятора.

Блок 1 управления содержит гене35 ратор 21 импульсов, третий D-триггер

22, четвертый D-триггер 23, первый

24 и второй 25 элементы И„ счетчик

26, формирователь 27 импульса по включению питания, третий элемент ; .И 28.

Блок 1 управления прецназначен для синхронизации работы устройства.

Управляющий вход 11 блока 1 управления является входом "Пуск" интерпо45 лятора. Выход блока 1 управления соединен с выходом 15 интерполятора, По указанному выходу стробируются многоразрядные приращения, поступающие на выходы 17-20 интерполятора.

Значения логической единицы на выходе 15 интерполятора сигнализирует о достоверности выходных данных на выходах 17-20 цифрового интерполятора.

По выходу 16 формируется сигнал "Конец интерполирования, Наличие логиII

55 ческой единицы на выходе 16 интерполятора свидетельствует о воспроизведении в данный момент заданного отCar!ras> логическог о нуля нга выходе устанавливает двоичные умножители в исходное состояние.

Первыи 2 и второй 3 регистры координатных приращений служат для приема и хранения N младших разрядов координатных приращений Лх и ду,определяющих заданный отрезок прямой.

Значения приращений Л х и Л у поступают по входу 13 интерполятора последовательно во времени. Запись

И младших разрядов координатного приращения в регистр 2 координатного приращения производится единичным уровнем на входе 12 интерполятора.

Запись N младших разрядов в регистр

3 координатного приращения производится единичным уровнем на входе 14 интерполятора. Выходы регистра 2 координатных приращений подключены к информационным входам двоичного умножителя 5. Выходы второ"o регистра 3 координатных приращений подключены к информационным входам второго двоичного умножителя 6.

Блок 4 постоянной памяти служит для хранения 2 — 1 разрядов 2

И-И разрядных приращений, формируемьгх эа один интерполяционный такт. Блок 4 постоянной памяти соединен адресными

axon„a!vи с N-И старшими разрядами третьего информационного входа интерполятора, по которому последовательно во времени поступают значения координатных приращений Лх и ду.Пер вый 5 и второй б двоичные умножители служат для формирования значения

l4-N младшего разряда 2 -разрядного приращения, формируемого за один интерполяционный такт Выход двоичного умножителя 5 соединен с информационным входом триггера 7, который служит для фиксации значения младmего разряда 2 + -разрядного приращения, формируемого за один интерполяционный такт по координате х. Bb!ход умножителя 6 соединен с информационным входом триггера 8, который служит для фиксации значения младшеЯ-М го разряда 2 -разрядного приращения, формируемого ".-а один интерполяционный -.àêò по координате у.

Регистры 9 и 10 служат для хранения 2 — 1 разрядов 2 -разрядного

М-> н-й приращения по координатам х и у соответственно, Их значения остаются неизменными до момента поступле".èÿ новых исходных данных.

1434406

Запись значения 2 -1 разрядов, PR И

-разрядных приращений, формируемых за один интерполяционный такт, в регистр 9 производится с выходов бло-. ка 4 постоянной памяти при наличии 5 на его адресных входах М-If старших разрядов координатного приращения ах и поступлении сигнала логической единицы на вход 1? интерполятора. За- )0 и-й пись значений 2 -1 разрядов 2 " "— разрядных приращений, формируемых за один интерполяциояный такт, в регистр

10 производится с. выходов блока 4 постоянной памяти прн наличии на его входах М-N старших разрядов координаmoro приращения Dy и поступлении сигнала логической ециницы на вход 14 интерполятора.

Генератор 2! импульсов служит для выработки последовательности импульсов, тактирующих работу блока 1 управления. Прямой выход генератора 21 импульсов соединен с первым входом первого элемента И 24 и управляющим 25 входом третьего триггера 22, а инверсный выход генератора 21 импульсов соединен с первым входом второго элемента И 25, Прямой выход третьего Р-триггера 22 соединен с вторыми входами первого ?4 и второго 25 элементов И и вторым выходом 16 интерполятора. Указанный выход является выходом "Конец интерполирования отрезка". Сигнал логического нуля на втором выходе 16 интерполятора сигнализирует об окончании интерполирования заданного отрезка прямой и готовности интерполятора принять значения координатных приращений ново- 40

ro отрезка прямой. Выход второго элемента И 25 является первым выходом блока I управления и первым вы ходом 15 интерполятора. По указанному выходу стробируятся выходные мно- 45 горазрядные приращения интерполятора, Значение логической единицы на указанном выходе сигнализирует о достоверности выходных данных на третьем 17, четвертом 18, пятом

19 и шестом 20 выходах линейного интерполятора.Выход первого элемента

И 24 является четвертым выходом бло-. ка 1 управления, Указанный выход подключен к управляющим входам первого

5 и второго 6 двоичных умножителей и управляющим входам первого 7 и второго 8 триггеров, а также к вычитающему входу счетчика 26, Счетчик 26 служит для формирования импульса отрицательной полярности по окончанию воспроизведения заданного отрезка прямой. Вход записи в счетчик соединен с выходом четвертого D-триггера

23, информационным входом третьего

D-триггера 22 и третьим выходом блока 1 управления, До поступления сигнала "Пуск" счетчик 26 находится в режиме записи содержимого информационных разрядов в счетчик, так как с прямого выхода четвертого триггера 23 поступает сигнал логического нуля, который является активным по отношению к сигналу записи в счетчик 26. На информационный вход счетчика 26 монтажным способом поступает значение 2 формирователь 27 импульса по включения питания служит для выработки в момент включения питания импульса отрицательной полярности, устанавливающего третий 22 и четвертый

23 D-триггеры в нулевое состояние.

Выход формирователя 27 импульсов соединен с первым входом третьего элемента И 28 и R-входом третьего

D-триггера ?2. Второй вход третьего элемента И 28 соединен с выходом переноса счетчика 26. Выход третьего элемента И ?8 соединен с В-входом второго триггера 23. Третий D-триггер 22 и четвертый D-триггер 23 служит для присинхрониэации цикла интерполяции к переднему фронту импульсов, формируемого генератором

21 импульсов, Управляющий вход четвертого D-триггера 23 соединен с первым входом 11 интерполятора. Указанный вход является входом "Пуски интерполятора. Информационный вход четвертого D-триггера 23 подключен к сигналу логической единицы, Интерполятор работает следующим образом.

В основе изобретения лежит возможность однозначного определения 2 " перемещений исполнительных органов или светящейся точки на экране (при отображении графической информации) за один интерполяционный такт. М— наибольшая разрядность координатных приращений, N — количество младших разрядов координатных приращений

5х и 5у, поступающих на регистры 2 и 3 координатных приращений.

Для доказательства возможности одц-й нозначного определения 2 переме5 14344 щений исполнительных органов или све тящейся точки рассмотрим работу двоичного умножителя на примере четырехразрядного píîè÷íîãî умножителя, временные диаграммы работы которого для различных значений управляющего кода на его .информационных входах приведены на фиг.5.

На выходе двоичного умножителя формируется последовательность импульсов, пропорциональная весам управляющего кода на его информационных входах. Если последовательность HMТакт управляющий код

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

ОООО

0000

0000

0000

0ОО0Х

0000

0000

000!

0000

0А01

ОООО

0001

0000

0001

0010

AAAl

0001

0000

0001

0AI1

O1ОО

0100

Al AA

А1АА

О) 00

0100

A1Al

0100

01ОП

0lAi

0100

0101

0100

0101

0101

0111

1010

1010

1010

lA10

1000

1010

1010

1010

1010

1011

1010

1011

1010!

011

1010

10I 1

1011

1 011

1110

1110

1110

1100

1llO

1110

11 !О

1101

ll1A

lll0

1110

1l1A м-Ф для данного примера в течение 2

2 - -1 = 3 тактов входной частоты, Причем для управляющих кодов, в которых старшие М-N=2 разряды одинаковы, эти группы также одинаковы. СовершенДля нашего примера И = 4, а И = 2, Как видно из приведенной таблицы, эти группы идентичны при различных значениях управляющего кода в течение м-и

2 — 1 тактов входной частоты, т.е. пульсов, формируемых на выходе двоичного умножителя за 2 тактов входМ ной частоты (И вЂ” разрядность двоичного умножителя), разбить на 2 групп, М то каждая группа представляет последовательность импульсов, формируемых на выходе двоичного умножителя за м-я .

2 тактов входной частоты, так как м мй Af

2 = 2 2, На выходе четырехразрядного двоичного умножителя (фиг,5) при различных значениях управляющего кода на его информационных входах формируются следующие последовательности.! 434 И6 но о-.!åâèäíî, что воспроизвести указанные группы, эа исключением импуль,ч-м сон н 2 -м такте можно при помощи блока постоянной памяти, на адресные

5 входы которого поступают старшие

M-N разрядов управляющего кода, Импульсы в 2 -м такте формируются ,м м

И-разрядным двоичным умножителем,на информационные входы которого поСтупает И младших разрядов управляющего кода. Карта прошивки блока постоянной памя"-: при 1=4, N = 2 имеет следующий вид .

Адрес Содержание 15

00, 000

0I 010

l0 I 01

11 111

В регистр 2 записывается N wrap, — 20 ших разрядов М-разрядного координатного приращения 1х. В регистр 3 записывается N младших разрядов Мразрядного координатного приращения

Ду. М-N старших разрядов координатных приращений поступает на адреснь|е входы блока 4 постоянной памяти. С выходов блока 4 постоянной памяти м-и считывается 2 -l„разрядов многоразрядных приращений, которые записываются в регистры 9 и 10. В регистр 9 м-й записывается 2 -1 разрядов многоразрядных приращений по координате х. В регистр 10 записывается 2 " -1 разрядов многоразрядных приращений по координате у. Указанные вьппе дей35 ствия предшествуют процессу интерполяции и составляют цикл подготовки.

При поступлении сигнала логической единицы на четвертый вход 11 ин- 40 терполятора на выходе 16 блока управления появляется сигнал логической единицы. Наличие сигнала логической единицы на выходе 16 свидетельствует о воспроизведении н данный мо- 45 мент заданного отрезка прямой. На первом выходе блока управления формируется последовательность импульcos поступающая на управляющие входы умножителей 5 и 6 и триггеров 7 и

8. На информационные входы двоичного умножителя 5 поступают значения

N младших разрядов координатного приращения d х. На информационные входы второго двоичного умножителя 6 поступают значения И младших разрядов координатного приращения Dy. При переходе сигнала на управляющих входах двоичных умножителей 5 и 6 из состояния .тогическ:. го куля в состояние логической единицы на выходах двоичных умножителей 5 и 6 появляются значения сигналов, равные значению и- ч

2 -го разряда многоразрядного приращения, формируемого за один интерполяционный такт, которые фиксируются н триггерах 7 и 8. При появлении сигнала логической единицы на выходе

15 интерполятора-многоразрядные приращения поступают на выход интерлок лятора.„Через 2 тактов на выходе ! 6 интерполятора формируется сигнал

"Конец интерполирования", который запрещает формирование последовательностей импульсов на выходе 15 интерполятора и третьем выходе блока 1 управления. На четвертом выходе блока 1 управления появляется сигнал логического нуля, устайавливающий двоичные умножители 5 и 6 в исходное состояние. Процесс интерполирования отрезка закончен. Диаграммы работы интерполятора приведены на фиг.3,4 °

Рассмотрим интерполирование отрезка прямой на числовом примере (описывается канал х, канал у работает аналогично). Пусть Дх = 1011, М=4 и N = 2. На адресные входы блока 4 постоянной памяти поступает код 10.

По укаэанному адресу хранится код

101, При поступлении сигнала логической единицы на вход 12 интерполятора указанный код записывается в регистр

9. Младшие N=2 разряды координатного приращения записываются н регистр 2 координатных приращений, С выходов регистра 2 указанные разряды поступают на информационные входы первого умножителя 5, т.е. на информационные входы умножителей 5 поступает код 11.

Разрядность умножителя 5 для данного случая равна двум. При поступлении сигнала "Пуск" на вход 11 интерполятора на управляющий вход двоичного умножителя 5 начинает поступать последовательность импульсов с третьего выхода блока 1 управления. На ныходе двоичного умножителя 5 за 2 = 2 4

1 такта формируется следующая последовательность 1110. Так как указанная последовательность с выхода триггера 7 поступает на выход 17 интерполятора, м-и который является 2 -м разрядом многоразрядного приращения, то на выходах 17,18 интерполятора sa 2 = 4 такта формируется следующая последовательность;

Я 1434406

101 1 101 1 101 1, 101, 0, 1 !

I== где значения, отмеченные i,, формируются на выходе двоичного умножителя.

Данная последовательность соответству-5 ет последовательности, формируемой двоичным умножителем за 2 = 2 м к

16 тактов входной частоты.

Информационная емкость (бит) блока постоянной памяти рассчитывается по следующей формуле:

g (Я м1 й-м

F. = 2 — 2 ми

2 {2 -11 при организации 2 " х 2 -1 раз- 15 рядных слов.

По включению питания на выходе блока 27 формируется отрицательный импульс, устанавливающий третий 22 и четвертый 23 D-триггеры в нулевое 20 состояние. Счетчик 26 находится в режиме записи содержимого информационных разрядов в счетчик, так как с прямого выхода четвертого D-триггера 23 на установочный вход счетчика поступает сигнал логического нуля, который является активным по отношению к сигналу записи в счетчик 26.

На информационный вход счетчика 26 монтажным способом поступает значение 2 . При поступлении сигнала логической единицы на первый вход II цифрового линейного интерполятора четвертый D-триггер 23 устанавлива тся в состояние логической единицы, разрешая тем самым работу счетчика

2п в счетном режиме, Кроме того. указанный сигнал поступает на третий выход блока 1 управления и разрашает работу первого 5 и второго б дво- ® ичных умножителей. Передним фронтом импульса, поступающего с прямого выхода генератора 21 импульсов, третий

D-триггер 22 устанавливается в состояние логической единицы, поскольку на его информационный вход поступает сигнал логической единицы с выхода четвертого D-триггера 23. Описанные выше действия обеспечивают строгую присинхронизацию цикла интерполяции к переднему фронту импульсов, форми5Î руемого генератором 21 импульсов, после поступления сигнала логической единицы на первый вход II интерполятора, который является входом "Пуск" интерполятора. С каждым импульсом с выхода генератора 21 импульсов при единичном значении третьего D-триггера 22 значение четчика 26 уменьшается на единицу. При переходе счетчика 26 с нулевого состояния в 2, где n — разрядность счетчика, на его выходе переноса P формируется импульс отрицательной полярности, который устанавливает четвертый D-триггер

23 в состояние логического нуля, С появлением переднего фронта импульса с генератора 21 импульсов третий Dтриггер 22 также устанавливается в состояние логического нуля, запрещая прохождение импульсов на выходы первого элемента И 24 и второго элемента И 25. Кроме того, сигнал логического нуля с выхода третьего Dтриггера 22 поступает на второй выход 16 интерполятора, сигнализируя об окончании интерполирования заданного отрезка. Число импульсов, сформированных с выходов первого 24 и второго 25 элементов И за интерполяционный цикл, равно 2 .

Р м У л а и 3 О б р е т е н и

Цифровой линейньгй интерполятор, содержащий первый и второй регистры координатных приращений, первый двоичный умножнтель и второй двоичный умножитель, информационные входы которого подключены к выходам второго регистра координатных приращений, входы которого соединены с И младшими разрядами третьего М-разрядного информационного входа интерполятора и с входами первого регистра координатных приращений, выходы которого подключены к информационным входам первого двоичного умножителя, о т— л и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены блок управления, блок постоянной памяти, первый и второй триггеры, первый н второй регистры, управляющий вход второго регистра соединен с управляющим входом второго регистра координатных приращений и с первым входом интерполятора, второй вход которого подключен к управляющему входу первого регистра координатных приращений и к управляющему входу первого регистра, информационный вход которого соединен с информационным входом второго регистра н выходом блока постоянной памяти, адресные входы которого подключены к .I старшим разрядам третьего информационного входа интерполятора, четвертый вход

1434406

94сг. 2 которого соединен с входом блока управления, первый и второй выходы которого подключены соответственно к первому и второму выходам интерполя5 тора, третий выход которого соединен с выходом первого триггера, информационный вход которого подключен к выходу первого двоичного умножителя, управляющий вход которого соединен с 10 управляющим входом второго двоичного умножителя, с управляющим входом первого и второго триггера и третьим выходом блока управления, четвертый выход которого подключен к установоч- 1 ным входам первого двоичного умножителя и второго двоичного умножителя, выход которого соединен с информационным входом второго триггера, выход которого подключен к четвертому выхо- 20 ду интерполятора, пятый и шестой выходы которого соединены соответственно с выходами первого и второго регистров.

2, Интерполятор по п.1, о т л и — 25 ч а ю шийся тем, что блок управления содержит генератор импульсов, третий и четвертый триггеры, первый, второй и третий элементы И, счетчик импульсов, содержащий информационные gp входы, формирователь импульса по включению питания, выход которого соединен с первым входом третьего элемента И и с установочным Я-входом третьего D-триггера, выход которого подключен соответственно к вторым входам первого и второго элементов

И и второму выходу блока управления,,первый выход которого соединен с выходом второго элемента И, первый вход которого подключен к инверсному выходу генератора импульсов, прямой выход которого соединен с управляющим входом третьего D-триггера и первым входом первого элемента И,выход которого подключен к пятому выходу блока управления и вычитающему входу счетчика, выход переноса которого соединен с вторым входом третьего элемента И, выход которого подключен к установочному R-входу четвертого D-триггера, информационный вход которого соединен с выходом логической единицы, а выход подключен к информационному входу третьего Dтриггера, установочному входу счетчика и четвертому выходу блока управления, вход которого является четвертым входом интерполятора и соединен с управляющим входом четвертого Dтриггера.

1434406

Ае. йв. дня.

1434406

У

Я

Рыбу

0001

00ff

Of0f

Offf

f00f

t0lt

1fN .1110

1111

Фиг. Х

Составитель И. Чвец

Техред М.Ходанич

Корректор N.Ïoêo

Редактор А.Маковская

Подписное

Тираж 866

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5552/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, /