Датчик равномерно распределенных случайных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для испытания аппаратуры в качестве источника входного сигнала. Цель изобретения - упрощение датчика. Датчик содержит первичный источник I -равномерно распределенных случайных чисел, схему 2 сравнения, счетчик 3, генератор 4 импульсов , элемент И 5, счетчик 6, регистры 7-9, группу элементов И 10, элемент ИЛИ 11, блок 12 синхронизации. Поставленная цель достигается за счет введения новых блоков и функциональных связей. 3 ил.

ч

:Ъ СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК с, я = (50 4 G 06 F 7 58!

В т

E,;=,;,, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Ф

<О

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4233061/24-24 (22) 20.04.87 (46) 30.10.88. Бюл. № 40 (71) Харьковский институт инженеров железнодорожного транспорта им. С. M. Кирова (72) А. Т. Кулик, P. А. Ефременко, В. С. Азарин и О. В. Хомицкий (53) 681.3(088.8) (56) Авторское свидетельство СССР № 398940, кл. <з 06 Е 7/58, 1972.

Авторское свидетельство СССР № 1056188, кл. G 06 Г 7/58, 1982.

„„SU„„14 4430 А 1 (54) ДАТЧИК РАВНОМЕРНО РАСПРЕДЕЛЕННЫХ СЛУЧАЙНЫХ ЧИСЕЛ (5?) Изобретение относится к вычислительной технике и может быть использовано для испытания аппаратуры в качестве источника входного сигнала. Цель изобретения — упрощение датчика. Датчик содержит первичный источник 1 -равномерно распределенных случайных чисел, схему 2 сравнения, счетчик 3, генератор 4 импульсов, элемент И 5, счетчик 6, регистры

7 — 9, группу элементов И 10, элемент

ИЛИ 11, блок 12 синхронизации. Поставленная цель достигается за счет введения новых блоков и функциональных связей. 3 ил.

1434430

Изобретение относится к вычислительной технике, в частности к цифровым датчикам случайных чисел, и может быть использовано для испытания аппаратуры в качестве входного сигнала. (!ель изобретения — упрощение датчика.

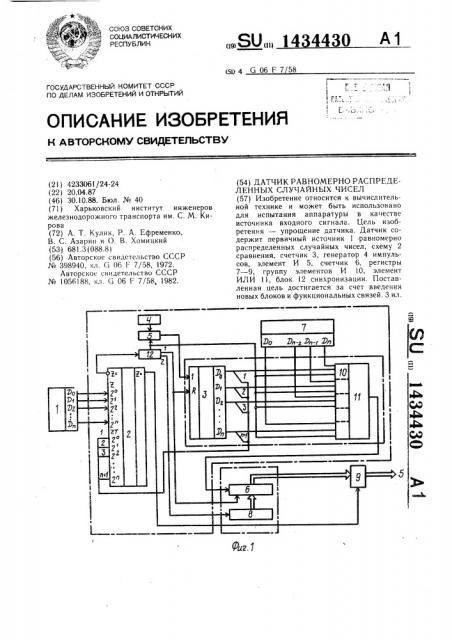

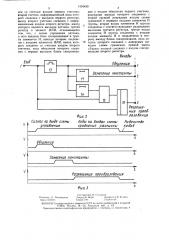

На фиг. 1 представлена схема устройства; на фиг. 2 — схема блока синхронизации; на фиг. 3 — временная диаграмма сигналов, поясняющая работу блока синхронизации.

Датчик содержит первичный источник 1 равномерно распределенных случайных чисел, схему 2 сравнения, счетчик 3, генератор 4 тактовых импульсов, элемент И 5, счетчик 6, регистры 7 — 9, группу элементов И 10, элемент ИЛИ 11 и блок 12 синхронизации.

Блок 12 синхронизации состоит из одновябратора 13, элемента 14 задержки, эл;.мента И 15 я триггера 16.

Датчик работает следующим образом.

С выхода источника 1 на первые входы схемы 2 сравнения поступает код случайного числа Z. На вторые входы схемы 2 сравнения поступает код из счетчика 3.

В исходном состоянии эти коды одинаковы я равны 00...0. В случае равенства кодов на входах схемы 2 сравнения последняя с инверсного выхода выдает низкий потенциал на вход запроса блока 12, который своим вторым выходом запрещает прохождение импульсов с выхода генератора 4 через элемент И 5 на счетный вход счетчика 3. Когда коды на первом я втором входах схемы 2 сравнения не равны, то на инверсном выходе схемы 2 появляется высокий потенциал, по которому блок 12 вырабатывает сигналы, обнуляющие счетчики 3, 6 я открывающий элемент И 5 для прохождения импульсов с выхода генератора 4. Сигнал с второго выхода блока 1 подготавливает элементы И 10 группы к прохождению импульсов с разрядных входов счетчика 3.

При поступлении на входы элементов И

10 группы числа импульсов, равного коду Z, на выходе элемента ИЛИ 11 получают число импульсов KZ.

При равенстве кодов на первых и соответствующих вторых входах схемы 2 сравнения последняя формирует высокий потенциал на прямом выходе и низкий потенциал на выходе, по которым блок 12 на своем втором выходе формирует запрещающий сигнал низкого уровня на втором входе элемента И 5. По этому сигналу. дальнейшее поступление импульсов на счетный вход счетчика 3 с выхода генератора 4 через элемент И 5 прекращается. Высокий потенциал на прямом выходе схемы 2 сравнения разрешает запись сформированного случайного числа Z с выхода счетчика 6 в регистр 9.

Если в дальнейшем на выходе источника 1 появляется код следующей реализации случайного числа Z, то он сразу поступает на первые входы схемы 2 сравнения. На ее вторые входы поступает код предыдущей реализации случайного числа.

Таким образом, на входах схемы 2 сравнения присутствуют разные коды, и цикл повторяется.

Работа датчика обеспечивается функционированием блока 12 синхронизации.

Формирование последовательности управляющих сигналов производится при любой. смене кода Z, выдаваемого источником 1 равномерно распределенных чисел, за исключением кода Х=З .

Допустим, коды, поступающие на входы схемы 2 сравнения, равны. В этом случае, на вход запуска блока 12 с инверсного выхода схемы 2 сравнения поступает низкий потенциал, который устанавливает триггер 16 в состояние «О». С выхода триггера 16 низкий потенциал как сигнал

«Запрет преобразования» поступает на второй вход элемента И 5 и третьи входы элементов И 10 группы.

Формирование управляющих сигналов начинается с поступления на вход блока 12 высокого потенциала с инверсного выхода схемы сравнения. По переднему фронту этого сигнала запускается одновибратор 13, с выхода которого импульс по"тупает на вход элемента 14 задержки я как сигнал «обнуление» на первый выход блока 12. Кроме того, высокий потенциал сигнала как разрешающий, присутствует на втором входе элемента 15 И.

Датчик работает, реализуя состно пение или

Х =A+KZ, 40 где п — разрядность датчика.

Датчик предназначен для выработки случайных чисел, равномерно распределенньгх в интервале от Л до В, прячем, константы Л я К задаются кодами, записанными в регистры 7 и 8.

Источник 1 генерирует случайное число в интервале от 0 до 2 — 1.

Форму га изобрегегга,г

Датчик равномерно распределенных случайных чисел, содержащий первичный источник равномерно распределенных чисел, разрядные выходы которого соединены с

55 первой группой разрядных входов схемы сравнения, генератор тактовых импульсов, выход которого соединен с первым входом элемента И, выход которого сседя1434430

ЙиоРь !

РЫРnpeudnEa ap

Составитель И. Столяров

Редактор Л. Пчолинская Техред И. Верес Корректор В. Бутяга

Заказ 5556/51 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 нен со счетным входом первого счетчика, второй счетчик, информационный вход которого соединен с выходом первого регистра, выход второго счетчика соединен с информационным входом второго регистра, выход которого является выходом датчика, третий регистр и элемент ИЛИ, отличающийся тем, что, с целью упрощения датчика, в него введены блок синхронизации и группа элементов И, выходы которых соединены с входами элементов ИЛИ, выход которого соединен со счетным входом второго счетчика, вход обнуления которого соединен с первым выходом блока синхрониза4 ции и входом обнуления первого счетчика, разрядные выходы которого соединены с второй группой разрядных входов схемы сравнения и первыми входами элементов И группы, вторые входы элементов И группы соединены с соответствующими разрядными выходами третьего регистра, третьи входы элементов И группы соединены с вторым входом элемента И и подключены -к второму выходу блока синхронизации, вход за10 пуска которого соединен с инверсным выходом схемы сравнения, прямой выход

«Равно» которой соединен с входом синхронизации второго регистра.