Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении надежных арифметических устройств. Целью изобретения является повышение отка зоустойчивости устройства. С этой целью в устройство, содержащее блок оперативной памяти, два сумматора, четьфе мультиплексора данных, два сдвигателя, два регистра результата, блок элементов ШШ и элемент И, введены третий су№«тор, пятый и шестой мультиплексоры данных, третий сдвйгатель, третий регистр результата и дешифратор отказов. 1 ил., 1 табл.

СОК! 3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ю

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (61) 1 336022 (21) 4231825/24-24 (22) 20.04.87 (46) 30.10.88. Бюл. Р 40 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) С.Н.Борисенко, И.В.Калкин, В.И.Возыкин и И.Д.Тахтамьпп (53) 681.325(088.8) (56) Авторское свидетельство СССР

1336022, кл. С 06 F 15/00, 1987. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к цифровой

SU > 4Ç4449 A 2 (51)4 G 06 F 15/00, 11/00 вычислительной технике и может быть .использовано при построении надежйых арифметических устройств. Целью изобретения является повышение отказоустойчивости устройства. С этой целью в устройство, содержащее блок оперативной памяти, два сумматора, четыре мультиплексора данных, два сдвигателя, два регистра результата, блок .элементов ИПИ и элемент И, вве" дены третий сумматор, пятый и шестой мультиплексоры данных, третий сдвйгатель, третий регистр результата и дешифратор отказов. 1 ил., 1 табл.

С:

4ь

С4

4ь

4ь

4ь

1434449

Изобретение относится к цифровой вычислительной технике, может быть использовано при построении надежных арифметических устройств и является

D усовершенствованием изобретения по авт. св. ¹ 1336022.

Целью изобретения является повышение отказоустойчивости устройства.

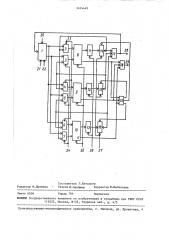

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 опера" тивной памяти, шесть мультиплексоров

2- 7 данных, три сумматора 8-10 три сдвигателя 11-13, три регистра 14-16 15 результата, блок 17 элементов ИЛИ, элемент И 18, дешифратор 19 отказов, причем входы дешифратора 19 соединены с выходами К-сигналов признаков сравнения результатов операций сумма-20 торов 8-10, а выходы дешифратора 19 соединены с входами разрешения выдачи регистров 14-16. Устройство имеет первый и второй входы 20, 21 адресов операндов, вход 22 разрешения приема,25 первый и второй входы 23 и 24 выбора операндов, вход 25 операции устройства, вход 26 управления направлением сдвига, вход 27 управления записью результата, информационный выход 28, . выход 29 признака ошибки.

Устройство работает следующим образом.

В основу всех операций, выполняемых в данном усуройстве, положен ба35 эовый оператор вида ((А „> +(А ))2 = А, где 1А „), c A< 7 — значения операндов, размещенных по адр е- 40 сам А1и А, + — признак выполнения одной из арифмети". ческих либо логических операций;

45 о m — - коэффициент сдвига.

Реализация этого оператора осуществляется за .четыре такта. В первом такте из блока 1 по адресам А „ (вход

20) и А (вход 21) одновременно счи50 тываются оба операнда и через откры" тые управляющими сигналами (входы 22, 23) первые входы мультиплексоров 2-7 поступают на входы сумматоров 8-10.

Во втором такте в сумматорах 8-10 параллельно и синхронно выполняется

55 арифметическая либо логическая операция в соответствии с кодом микрокоманды, поступающим на вход 25. В этом же такте результат операции с выходов сумматоров 8-10 поступает на входы сдвигателей 11-13, в которых в соответствии с поступающим по входу 26 сигналом осуществляется сдвиг информации на величину m и далее осуществляет я ее запись в регистры 1416. В третьем такте по управляющим сигналам (входы 23, 24) открываются вторые входы мультиплексоров 2-7, и результаты выполненной в каждом сумматоре операции с выходов регистров

14-16 поступают на входы сумматоров 8-10.

Начиная с третьего такта, сумматоры 8-10 работают в режиме компаратора, осуществляя попарное сравнение результатов операции, и формируют сигналы признаков сравнения К, которые поступают с вторых вьгходов сумматоров 8-10 на входы дешифратора 19 и элемент И 18> выход EQTopoI o под» ключен к выходу 29 устройства, при этом состояние регистров 14-16 не изменяется. В случае сравнения результатов операции в сум;заторах 8-10 элемент И 18 выдает сигнал разреше ния, в соответствии с которым в четвертом такте производится запись результатов операции из регистров 14

15 либо 16 через блок 17 в блок 1 памяти по управляющему сигналу на входе 22 разрешения приема. Запись результатов операции в блок 1 осуществляется по адресу А, синхронно подаваемому на входы 20, 21.

При сбое или отказе одного из вычислительных узлов устройства в соответствующих сумматорах происходит несравнение результатов операции (см. таблицу), дешифратор 19 идентифицирует номер отказавшего вычислительного узла и исключает его из вычислительного процесса, запрещая выдачу информации из регистра результата отказавшего узла путем подачи на вход разрешения выдачи регистра сиг" нала "Запрет", который переводит его в третье состояние. При этом процесс вычисления не прерывается, и запись правильного результата операции в блок 1 памяти производится через блок

17, так и в предыдущем случае.

При сбое или отказе двух вычислительньгх узлов во всех сумматорах про-. ,исходит несревнение результатов операции, на выходе элемента И 18 фор" мируется сигнал запрета, запись в

14344 блок 1 в четвертом такте не производится, код операции не изменяется, и она повторяется. При .превышении числа допустимых повторений включаются контролирующие тесты для определения отказавшего вычислительного узла, и по управляющим сигналам (входы 23, 24) устройство переводится в режим работы с одним вычислительным узлом.

Формула изобретения

Вычислительное устройство по 15 авт. св. Ð 1336022, о т л и ч а ю— щ е е с я тем, что, с целью повышения отказоустойчивости, оно содержит третий сумматор, пятый и шестой мультиплексоры данных, .третий.сдвигатель, 20 третий регистр результата и дешифратор отказов первый второй и третий входы которого соединены с выходами признака ошибки первого, второго и третьего сумматоров соответственно, 26 первый, второй и третий выходы дешифратора отказов подключены к входам разрешения выдачи первого, второго и третьего регистров результата соответственно, первые информационные 30 входы пятого и шестого мультиплексоров данных соединены соответственно с первым, вторым выходами блока операзливной памяти, первый и второй информационные входы, управляющий вхоц 35 и информационный выход третьего сумматора подключены соответственно к выходам пятого и шестого мультиплек49

4 соров данных, входу операции устрой ства и информационному входу третьего сдвигателя, управляющий вход и выход которого соединены соответст= венно с входом управления направлением сдвига устройства и информационным входом третьего регистра результата, синхровход которого подключен к синхровходу устройства, выход первого регистра результата соединен с первым входом блока элементов ИЛИ и вторыми информационными входами первого и шестого мультиплексоров данных, выход второго регистра результата подключен к второму входу блока элементов ИЛИ и вторым информационным входам второго и третьего мультиплексоров данных, а выход третьего регистра результата соединен с третьим входом блока элементов ИЛИ и вторыми информационными входами четвертого и пятого мультиплексоров данных.

Сумма- Значения сравниваемых Отказавтор результатов ВУ ший ВУ, ?и II ИиТТТ ИТи I

И 1

III 0

1434449

Составитель Г.Виталиев

Редактор M.Öèòêèíà Техред JI.0лийньщ Корректор И.Васильева

Заказ 6636 Тираж 704 Подписное

BHHHIIH Государственного комитета "o изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4