Устройство для регенерации динамической памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для регенерации динамической памяти ЭВМ. Целью изобретения являетгся повышение быстродействия памяти. Устройство содержит генераторы 1, 2 тактовых импульсов, триггеры 3, 4, шинные формирователи 5, 6, блок 7 местного управления, счетчики 8,- 8, дешифратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13. В устройстве текущие коды счетчиков определяют допустимое время хранения информации для каждой строки оперативной памяти 15. При обращении процессора 14 к оперативной памяти 15 в процессе работы происходит обнуление счетчика 8, соответствующего коду ад- g реса выбранной строки, что исключает лишние циклы регенерации. 3 ил. (Л

СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 С 11 С 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4235989/24- 24 (22) 24.04.87 (46) 30,10.88. Бюп. 9 40

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛ АМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (72) E.Â.Áëàæååâè÷, Ю.В.Терпугов и О.В.Летнев (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР

У 1152034, кл. С 11 С 7/00, 1985.

Авторское свидетельство СССР

У 1246136, кл. G 11 С 7/00, 1986 (прототип). (54) УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ДИНАМИЧЕСКОЙ ПАИЯТИ (57) Изобретение относится к вычислительной технике и может быть исполь„„SU„„1484497 А 1 зовано для регенерации динамической памяти 3ВМ. Целью изобретения являет ся повышение быстродействия памяти.

Устройство содержит генераторы 1, 2 тактовых импульсов, триггвры 3, 4, шинные формирователи 5, 6, блок 7 местного управления, счетчики 8, — 8» дешифратор 9, шифратор 10, регистр 11, элемент И 12, элемент ИЛИ 13. В устройстве текущие коды счетчиков определяют допустимое время хранения информации для кажцой строки оперативной памяти 15. При обращении процессора 14 к оперативной памяти 15 в процессе работы происходит обнуление счетчика 8, соответствующего коду ад- ф реса выбранной строки, что исключает

"лишние циклы регенерации. 3 ил.

1434497

Изобретение относится к вычислительной технике и может быть использовано для регенерации динамической па— мяти ЭВМ.

Цель изобретения — повыше ние быстродействия памяти.

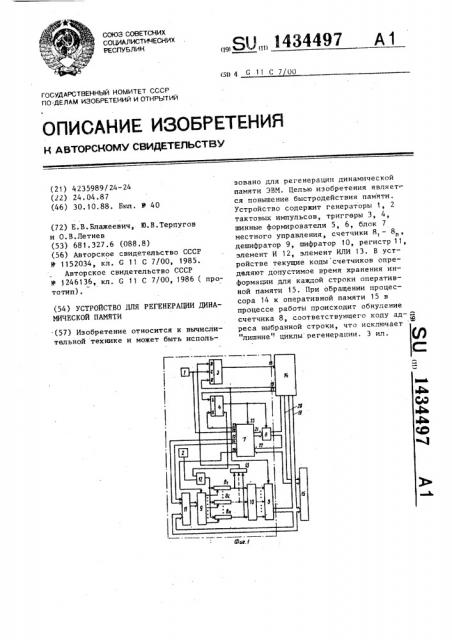

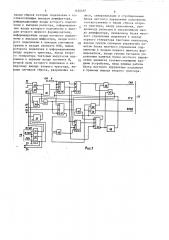

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — функциональная схема блока местного управ- 1р ления; на фиг. 3 — временная диаграмма работы устройства в режиме регенерации информации.

Устройство содержит первый 1 и второй 2 генераторы -.àêòîâûõ импульсов, первый 3 и второй 4 триггеры, второй

5 и первый 6 шинные формирователи, блок 7 местного управления, счетчики

8, дешифратор 9, шифратор 10, регистр

11, элемент И 12, элемент ИЛИ 13. На фиг. 1 также изображены элементы ЭВМ, взаимодействующие с устройством: центральный процессор 14 и оперативная память 15. Кроме того устройство со7 держит выход 16 требования прямого 25

1цоступа к памяти (ПДП) процессора 14, вход 17 предоставления ПДП, выход 18 подтверждения захвата канала (ПЗ), адресные выходы 19, входы — выходы 20 управления памятью, группу выходов 21 30 и группу входов 22 блока 7 местного управления, вход 23 режима работы блока 7 местного управления каналом, выход 24 сигнала синхронизации, выход

25 сигнала разрешения записи, выход

26 сигнала стр обир о ва ния, выход 2 7 сигнала сброса, синхровход 28 блока

7 местного управления.

Блок 7 местного управления- содержит элементы ИЛИ вЂ” НЕ 29-33, элемент

HE 34, одновибратор 35, элементы И

36-39, триггеры 40-44, элементы И-НЕ

45-47, элемент 48, одновибратор 49 и резистор.

Устройство работает следующим образом.

В исходном состоянии триггеры 3 и

4, а также триггеры 40-42, 44 сброшены, триггер 43 взведен. В старшие разряды счетчиков записаны соответственно коды 11...11,11..10,... 00..00 (цепи обнуления и начальной установки не показаны), Импульсы с выхода генератора 2 через элемент И поступают на счетные входы счетчиков 8.

В режиме регенерации сигнал с инверсного выхода триггера 4 разрешает прохождение импульсов с выхода генератора 2 через элемент И 12 на счетные входы счетчиков 8. При переполнении одного иэ счетчиков 8 сигнал с выхода его последнего разряда через элемент ИЛИ 13 поступает на вход установки триггера 3. Одновременно на выходе шифратора 10 устанавливается код счетчика 8 (от 0 до n), соответствующий коду адреса строки тех ячеек оперативной памяти, для которых истекает время хранения информации и требуется регенерация.

По переднему фронту импульса первого генератора 1 устанавливается триггер 3, на его прямом выходе 16 вырабатывается сигнал требования прямого доступа. Центральный процессор

14 приостанавливает выполнение операций, освобождает адресную шину 19 и выдает ответный сигнал на вход 17

"ПДП", устанавливающий триггер 4, который, в свою очередь, сбрасывает триггер 3, вырабатывает сигнал на выходе 18 "ПЗ", а также открывает шинные формирователи 5 и 6.

Сигнал с инверсного выхода триггера 4 запрещает прохождение импульсов генератора 2 через элемент ИЛИ 12 на входы счетчиков 8. Сигнал с прямого выхода триггера 4 поступает в блок 7 местного управления и разрешает устанонку триггера 40, который взводится после завершения текущего цикла обращения к оперативной памяти и снятии сигналов синхронизации активного устройства (СИА), синхронизации пассивного устройства (СИП), поступающих на входы 22, положительным перепадом тактового импульса (ТИ) от генератора 1.

Сигнал регенерации (РГН) с прямого выхода триггера 40 поступает через шинный формирователь 6 в оперативную память 15 и остается активным в течение всего времени регенерации.

Следующими так товыми импул ьс ами последовательно взводится триггер 42, сбрасывается триггер 43 и взводится триггер 44. Сигналы с инверсного выхода триггера 43 и прямого выхода триггера 44, собранные на элементе

ИЛИ 48, формируют сигнал "СИА", а собранные на элементе И 38 формируют сигнал "ВВОД". Сигналы "СИА" и "ВВОД" поступают в оперативную память 15 через шинный формирователь 6 вместе с кодом адреса строки с выхода шинного формирователя 5. Одновременно код адреса строки поступает на информационные входы регистра !1.

143 497

Запись в регистр 11 происходит по переднему фронту сигнала на выходе 24, поступающего из блока 7. B ответ на сигнал "ВВОД" оперативная память 15 формирует сигнал "СИП", поступающий на информационный вход триггера 41, который очередным ТИ устанавливается в единичное состояние, разрешая установку триггера 43 следующим ТИ. При 1О этом снимается сигнал "ВВОД", в ответ на который оперативная память 15 снимает сигнал "СИП".

Триггер 41 сбрасывается очередным

ТИ, а следующим ТИ сбрасывается триг-15 гер 44 и снимается сигнал "СИА". Одновибратор 35 выделяет задний фронт и формирует на выходе 26 блока 7 одиночный импульс, который поступает на управляющий вход дешифратора 9, обну-2О ляя тем самым счетчик 8, соответствующий коду, хранящемуся в регистре 11.

Одновибратор 49 выделяет передний .фронт и формирует импульс отрицательной полярности, обнуляющий триггер 40,25 а через элемент НЕ 34 и триггер 4, Снимаются сигналы "РГН" и "ПЗ", цикл пегенерации закончен. !

Таким -же образом может осуществляться регенерация для любой строки оперативной памяти 15. Если же в про- цессе работы устройства ни один из счетчиков 8 не переполнен, т.е. время хранения информации ни для одной строки оперативной памяти не вышло, то работа устройства происходит следующим образом.

В режиме обращения к оперативной памяти 15 процессор 14 устанавливает на адресной шине код адреса ячейки памяти, а на управляющей шине вырабатывает сигналы управления, поступающие в блок 7 управления с входов

22: канальный сигнал синхронизации -45 пассивного устройства (КСИП), канальный сигнал выбора внешнего устройства (КВУ). младшие разряды кода адреса, являющиеся кодом адреса строки, по сигналу с выхода 24 блока 7 при наличии разрешающего сигнала на его выходе 25 записываются в регистр 11.

Запрещающий запись в регистр 11 сигнал появляется на выходе 25 блока 7 .при обращении процессора 14 не к оперативной памяти 15, а к регистрам внешних устройств. При этом не формируется сигнал на выходе 26 блока 7 управления.

Так как при обращении к оперативной памяти 15 происходит регенерация всех ячеек памяти с заданным адресом строки, то по окончанию цикла обращения к оперативной памяти 15 по сигналу с выхода 26 блока 7 сигналом с выхода дешифратор 9 происходит обнуление счетчика 8, порядковый номер которого совпадает с кодом адреса строки, хранящимся в регистре 11. Запрос на регенерацию ячеек оперативной памяти

15 с данным адресом строки может поступить теперь с выхода данного счетчика 8 только через время Тр при условии, что за это время процессор 14 больше не обратится к ячейкам с этим адресом строки.

Таким образом, текущие коды счетчиков определяют допустимое время хранения информации для каждой строки оперативной памяти 15..При обращении процессора 14 к оперативной памяти 15 в процессе работы происходит обнуление счетчика 8, соответствующего коду адреса выбранной строки, что исключает "лишние" циклы регенерации °

Формула и з о б р е т е н и я

Устройство для регенерации динамической памяти, содержащее первый и второй генераторы тактовых импульсов, первый и второй триггеры, первый и второй шинные формирователи, элемент

ИЛИ, причем выход первого генератора тактовых импульсов подключен к синхровходу первого триггера, выход которого является выходом требования прямого доступа к памяти устройства, прямой выход второго триггера является выходом "Подтверждение захвата" канала устройства и подключен к входу сброса первого триггера и управляющим входам первого и второго шинных ,формирователей, выходы которых являются соответственно выходами управления памятью и адресными выходами ; устройства, вход установки второго триггера является входом предоставления прямого доступа к памяти устройства, о т л и ч а ю щ е е с я тем, что, с. целью повышения быстродействия памяти, оно содержит группу счетчиков, регистр, дешифратор, шифратор, блок местного управления и элемент И, выход которого подключен к счетным входам счетчиков группы, 1434497

+56 R входы. сброса которых подключены к со:ответствующим выходам дешифратора, информационные входы которого подключены к выходам регистра информацион1

5 ные входы которого подключены к выходам второго шинного формирователя, информационные входы которого подключены к выходам шифратора, входы кото ого подключены к выходам счетчиков группы и входам элемента ИЛИ, выход оторого подключен к информационному ходу первого триггера, выход второо генератора тактовых импульсов подлючен к первому входу элемента И, торой вход которого подключен к инерсному выходу второго триггера, выМоды сигналов сброса, разрешения эаписи, синхронизации и стробирования блока местного управления подключены соответственно к входу сброса второго триггера, входу разрешения, синхровходу регистра и управляющему вхо— ду дешифратора, синхровход блока местного управления подключен к выходу первого генератора тактовых импульсов, выходы группы сигналов управления памятью блока местного управления подключены к входам первого шинного формирователя, входы группы сигналов управления памятью блока местного управления являются соответствующими входами устройства, вход режима работы блока местного управления подключен к прямому выходу второго триггера.

1434497

Составителв C,Шустенко

Техред А,КравчУк

Корректор Л.Патай

Редактор И.Касарда

Подписное

Тираж 590

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

3 аказ 5561/54

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проекта ня 4