Способ считывания информации в мноп-элементе памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и может быть использовано при разработке репрограммируемых постоянных запоминагацих устройств. Целью изобретения является увеличение времени хранения информации и количества циклов перепрограммирования МНОП-элемента памяти. Поставленная цель достигается тем, что амплитуда напряжения считывания пропорциональна пороговому напряжению запоминаю- ,щего транзистора злемента памяти в состоянии логического нуля. 1 ил.

СОЮЗ СОВЕТСНИХ

СООИА ЛИСТИЧЕСНИХ

РЕСПУБЛИК

<5;> 4 С 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21 ) 4121604/24-24 (22) 23.09.86 (46) 30. 10.88. Бюп. Ф 40 (72) В.П. Сидоренко, К.М. Королевец, В.Е.Стиканов и Ю.А.Юхименко (53) 681. 327. 66 (088. 8) (56) Электроника, 1981, У 4, с. 73-77.

Электроника, 1981, 9 9, с. 58-62 (прототип). (54) СПОСОБ СЧИТЫВАНИЯ ИНФОРМАЦИИ В

МНОП-ЭЛЕМЕНТЕ ПАМЯТИ (57) Изобретение относится к микро„„SU„„1434499 А 1 электронике и может быть использовано при разработке репрограммируемых постоянных запоминакщих устройств.

Целью изобретения является увеличение времени хранения информации и количества циклов перепрограммирования

МНОП-элемента памяти. Поставленная цель достигается тем, что амплитуда напряжения считывания пропорциональна пороговому напряжению запоминающего транзистора элемента памяти в состоянии логического нуля. 1 ил.

1434499

Изобретение относится к микроэлектронике и может быть использовано при разработке репрограммируемых постоянных запоминающих устройств большой информационной емкости.

Цель изобретения — увеличение времени хранения информации и количества циклов перепрограммирования.

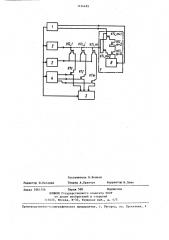

На чертеже приведена конструкция фрагмента накопителя МНОП РЦЗУ, реализующего способ. Устройство содержит формирователь 1 управляющих сигналов, формирователь 2 второго постоянного напряжения на сто-15 ке запоминающих транзисторов, формирователь 3 третьего, постоянного напряжения на истоке, коммутатор 4 столбцов, управляющий ключами Т где j- номера столбцов, формирователь о 5 первого постоянного напряжения на затворе запоминающих транзисторов i ! строки, формирователь 6 напряжения на, истоке опорного транзистора Т;, 44 входящего вместе с транзисторами Т, 25

Т1 „в блок 7 коррекции, который, обеспечивает изменение U

В режиме "Запись" формирователь 1 вырабатывает команды, обеспечивающие подключение к электродам выбранного ! запоминающего транзистора Т накопи1i j теля напряжений режима записи и от ключение от i строки блока 7 переводрм в закрытое состоние транзисторов

Т; +„, Т;

J 1Ф

li

В режиме "Стирание тот же форми,.рователь 1 обеспечивает подключение

К i строке затвора транзистора Т1,ю+4 блока 7, открывая транзистор Т; „,4 (транзистор Т;,закрыт) и закрывая

1 адресные транзисторы Т, ... Т, где

m — количество запоминающих транзисторов в строке. Формирователи 2 и б вырабатывают при этом нулевые потенциалы.

Напряжение стирания, вырабатываемое формирователем 5, воздействует одинаковым образом на затворную систему запоминающих транзисторов Т; и Т; „ ... Т; (по длительности и абсолютной величине напряжения), что при соответствующей длительности импульса стирания переводит транэистоpb1 Т{ ° а ° Т1 Т в состоя ние с одинаковым пороговым напряже55 нием.

В режиме "Считывание" формирователь i вырабатывает команды, обеспечивающие подключение блока 7 к строке, открывая транзисторы Т; ...

Т;, „«, Считывание информации из выбранного запоминающего транзистора определяется подключением его электродов к формирователям 2 и через открытый адресный транзистор Т1 — к формирователям 3. Прн этом U ö, вырабатываемое формирователем 5, ограничивается величиной порогового напряжения

Т; +4 и напряжением смещения формирователя 6 блока 7. Транзистор Т; +, пороговое напряжение которого меньше возможных значений порогового напряжения Т;, 4 исключает воэможность перевода Т 4>m+4 в режим насыщения (ограничивает напряжение на стоке Т„,4).

Величина смещения, вырабатываемого формирователем 6, определяется требованиями по быстродействию считывания.

Таким образом, при включении режима считывания на затвор элемента памяти коммутируется напряжение U „, амплитуда которого перед каждым циклом считывания устанавливается пропорционально порогу включения элементта памяти в состоянии "О"..

Использование предлагаемого способа считывания информации в МНОП-элементе памяти обеспечивает увеличение времени хранения информации в актив— ном режиме и количества циклов перепрограммирования, что значительно повышает качество и надежность как

РПЗУ, так и устройств электроннойтехники на их основе, t

Формула изобретения

Способ считывания информации в

МНОП-элементе памяти, основанный на подаче первого, второго и третьего постоянных напряжений соответственно на затвор, сток и исток запоминающего транзистора элемента памяти, о т— л и .ч а ю шийся тем, что, с целью увеличения времени хранения, амплитуда первого постоянного напряжения пропорциональна изменению порогового напряжения запоминающего транзистора элемента памяти в состоянии логического нуля.

1434499

Составитель Б.Венков

Техред А.Кравчук

Корректор М.Пако

Редактор И. Касарда

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР

IIO e M H o TeHHH H oTKpblTHH

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ.5561/54

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,. 4