Устройство для преобразования сигналов с импульсно-кодовой модуляцией в сигналы с дельта-сигма-модуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи,-Его использование в системах передачи информации позволяет повысить точность преобразования. ycji-poftcTBO содержит сумматор 1, элементы НЕ 2, 3 . и буферньй регистр 4. Благодаря введению элементов ЗАПРЕТ 5-7, элемента И 8, элемента ИЛИ 9, элемента 10 эквивалентности и коммутатора 11 уровня сигнала, в устройстве обеспечивается более точное кодирование сигнала ошибки при том же быстродействии. 1 ил. с (О

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (!9) О!) (5!) 4 Н 03 М 7/36

1 а Л (C

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4229959/24-24 (22) 13;04.87 (46) 30.10.88. Бюл. !,"- 40 (71) Ленинградский электротехнический институт связи им. проф. М.А.БончБруевича (72) Ю.С.Власюк (53) 621.376.56:681.325 (088.8) (56) Авторское свидетельство СССР

В 1206963, кл. Н 03 М 7/36, 1984.

International СопХегепсе on Communications, Toronto, 1978, v. 3, р; 45, 3/2-45, 3/5. fig. 6. (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

СИГНАЛОВ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ В СИГНАПЫ С ДЕЛЬТА-СИГМА-МОДУЛЯЦИЕЙ (57) Изобретение относится к вычислительной технике и технике связи. .Его использование в системах передачи информации позволяет повысить точность преобразования. Устройство содержит сумматор 1, элементы НЕ 2, 3 и буферный регистр 4. Благодаря введению элементов ЗАПРЕТ 5-7, элемента

И 8, элемента ИЛИ 9, элемента 10 эквивалентности и коммутатора 11 уровня сигнала, в устройстве обеспечивается более точное кодирование сигнала ошибки при том же быстродействии.

1 ил.

1434547

2, е„„, -2,5, О, О cñ,å, (1,5

Таблица I

Xm е„,-о

Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах передачи информации.

Цель изобретения — повышение точ5 ности преобразования.

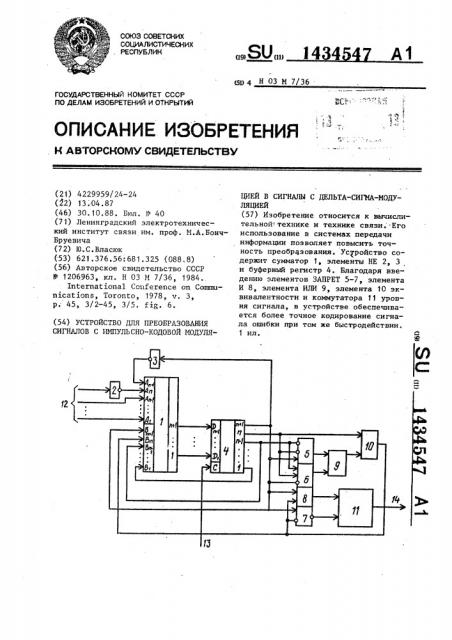

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит сумматор 1, первый 2 и второй 3 элементы НЕ, буерный регистр 4, первый 5, второй 6 и третий 7 элементы ЗАПРЕТ, элемент 1 8, элемент ИЛИ 9, элемент 10 экви:валентности, коммутатор 11 уровня сигнала, информационные. входы 12, тактовый вход 13 и выход 14.

Устройство работает следующим об,:разом.

Отсчеты ИКИ-сигнала (сигнала им пульсно-кодовой модуляции) поступают ! .:на входы 13, из разрядность равна и,, причем знаковый (старший) разряд ! отсчетов при подаче на сумматор 1 нвертируется элементом НЕ 2.

Работа устройства описывается вы раже нием е„,= е„„,+ Х„„- qm= (1) (е,- с1 ) + Х

30 где е и е, - сигналы на выходах сумматора 1 соответственно в моменты времени m u m-1, которые являются отсчетами сигнала ошибки ДСМ (дельта-сигма-модуляции)1 сигнал на выходе 14 устройства, который также является сигналом в цепи обратной связи ДСМ, входной сигнал.

Пусть входной сигнал имеет и-1 разрядов, включая знаковый, и (Х а 1.

Инвертирование знакового разряда первым элементом НЕ 2 означает преобразование сигнала в прямой код. Диапазон изменения сигнала е ошибки согласно (1) делится на три уровня, т.е.

О «- е щ 1,5, 1,5 « е„, а 2,5 и е 2 5 что приводит к оолее точному кодированию сигнала ошибки, который в ДСИ является проинтегрированным значением сигнала разности входного сигнала Х и аппроксимирующего сигнала с1.. Тогда

1,5 е с2 5 (2) Таким образом, если разбить диапазон изменения сигнала ошибки на три поддиапазона, то и аппроксимирующий сигнал q должен принимать три значения, которые могут быть закодированы не менее, чем двумя разрядами, а не одним, как в прототипе. С другой стороны, желательно, чтобы быстродействие устройства изменилось незначительно, т.е. необходимо не вносить существенной задержки в цепь обратной связи, а именно с выхода регистра 4 на вторые входы сумматора 1.

Составим табл. 1 всевозможных значений сигналов на и+1)-ом, и-ом и (n-1)-ом выходах сумматора 1, с учетом того, что этп разряды имеют соответственно веса равные 2, 1 и

0, 5 при (XI (1. В этой таблице, исходя из (2) запишем значение q и значения первых трех разрядов разности е,„, - q с учетом тех же весов.

1 2 3 4 5 6 7 8 и+1 1 1 1 1 О О О О

1 1 О О 1 1 О 0

1 О 1 О 1 О 1 О

2 2 2 1 1 0.0 О п+1 О О О 0 0 0 О О

1 1 О 1 О 1 .0 О и1.10101010

Из табл. 1 следует, что разность е,, — q может быть получена отбрасыванием (и+1)-го разряда сигнала на выходах регистра 4, сохранением (n-i).— го разряда и инвертированием и-го разряда для четвертой и пятой коло-.х нок. Таким образом, требуется во-первых, анализируя значения трех старших разрядов е „„, для комбинаций значений, представленных в четвертой и пятой колонках табл. 1, инвертиро1434547

Таблица 2 и-й вход сумматора 1

Вход 1 Вход 2

n+1 п п1

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

30

1 0 1

1 0

0

0 вать значение и-го разряда, а во всех остальных случаях оставлять значение и-го разряда без изменений, во-вторых, необходимо вырабатывать сигналы управления коммутатором 11, на выходе которого формируется трехуровневый сигнал с ДСМ, в зависимости от значения и . На основании табл. 1 легко составить табл. 2 требуемых переключений.

Выходы регистра Входы коммута4 тора 11

При этом считается, что управляющие сигналы на входах коммутатора 11 закодированы для различных значений д0

q, как представлено в.табл. 3. „

Таблица 3- о Вход 1 Вход 2

В качестве коммутатора 11 уровня сигнала можно применить любую схему, имеющую три уровня на выходе (например, можно использовать логические элементы, входящие в микросхему типа К155ЛП8 с тремя состояниями на выходе, подключив к ее выходу цепочку из двух одинаковых поспедовательно включенных резисторов, один конец которой соединен с общей шиной, а другой — с источником питания).

Следует отметить, что быстродействие устройства оценивается следующим образом:

Е r(t3 + t, 4) (Сълб+

- ;;) ° где t „ — время задержки логического блока 6.

Из чертежа видно, что t> = 3 С „, где,. — время задержки одного логического элемента. Поскольку, обычно, <(г.„„, то быстродействие устройства практически не изменяется.

Таким образом, за счет более точного кодирования сигнала ошибки повышается точность преобразования

ИКИ-сигнала в сигнал с ДСИ.

Формула из обр е те ния

Устройство для преобразования сигналов с импульсно-кодовой модуляцией в сигналы с дельта-сигма-модуляцией содержащее сумматор, входы первого— (n 1 -го разрядов первой группы входов которого (и -разрядность входного сигнала) непосредственно, а вход и-го разряда первой группы входов через первый элемент НЕ подключены к соответствующим информационным входам устрой тва, выходы сумматора соединены с одноименными информационными входами буферного регистра, выходы первого — (п-1)-ro разрядов которого соединены с входами одноименных разрядов второй группы входов .сумматора, выход (n+1)-го разряда буферного регистра подключен непосредственно-и через второй элемент

НЕ к входам (n+1)-х разрядов соответственно второй и первой групп входов сумматора, тактовый вход буферного регистра является тактовым входом устройства, о т л и ч а ю щ е е— с я тем, что, с целью повышения точности преобразования, в устройство введены коммутатор уровня сигнала, элемент ИН1, элемент эквивалентности, элемент И и элементы ЗАПРЕТ, первый запрещающий вход первого и первыи разрешающий вход второго элементов

ЗАПРЕТ объединены и подключены к

Составитель О.Ренинский

Техред М.Ходанич Корректор О,Кравцова

Редактор А.Ренин

Заказ 5564/56 Тираж 929 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5 1434547 6 выходу (n-1)-го разряда буферного ре- мента И и запрещающему входу третьегистра, выход n-ro разряда которого ro элемента ЗАПРЕТ, второй вход элесоединен с первым входом элемента мента И, разрешающие входы первого эквивалентности вторым запрещающим

Э

5 и третьего и запрещающий вход второвходом первого и вторым разрешающим ro элементов ЗАПРЕТ объединены и подвходом второго элементов ЗАПРЕТ, вы- ключены к выходу (и+1)-ro разряда буходы которых соединены с входами эле- ферного регистра, выход элемента И и мента ИЛИ, ныход которого соединен инверсный выход третьего элемента

С вторым входом элемента эквивалент- 1О ЗАПРЕТ соединены соответственно с

1 оати, выход которого подключен к первым и вторым входами коммутатора

Входу и-го разряда второй группы урания сигнала, вьщрд которого являНходов сумматора, первому нходу эле- ется выходом устройстна.