Устройство для оценки качества передачи сигналов по линейному тракту цифровой системы передачи

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и м.б. использовано для оценки готовности и качества передачи при эксплуатации и испытаниях многоканальнъпс цифровых систем передачи с временным уплотнением. Цель изобретения - расширение функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов (ЦС); Устр-во содержит блок 1 вьщеления ошибок, счетчик 2, блок 4 управления, формирователь (Ф) 5 тактовых импульсов, таймер 7 и блок 8 вычислений. В устр-во введены Ф 6 адреса, блок 3 памяти (ВП). В БП 3 для каждого низкоскоростного ЦС вьщелено требуемое кол-во ячеек памяти, в которых в течение одного цикла сохраняется измеренное значение суммы ошибок данного сигнала. В каждом такте последовательно выполняются след, операции: перенесение значения суммы ошибок данного ЦС в счетчик 2 измерения ошибок, прибавление единицы к записанному значению при наличии ошибки в ЦС, запись полученной суммы в соответствующие ячейки БП 3. Записанное значение хранится до следующего цикла, а в следующем такте вьшолняются аналогичные операции для ЦС со следующим номером, задаваемым Ф 6. Накопление информации об ошибках в каждом ЦС производится до конца периода измерения. 1 ил. (Л

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flG ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ g y Н 04 3 3/14 (21) 4093335/24-09 (22) 23.07.86 (46) 30.10.88. Бюл. № 40 (72) ВоИюМинкин ГеЕеИткис и А.С.Данилин (53) 621.395.664(088.8) (56) Авторское свидетельство СССР № 1061280, кл. Н 04 1 11/08, 1982 °

Авторское свидетельство СССР

¹ 1380585, кл. Н 04 J 3/14, 1986. (54) УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА

ПЕРЕДАЧИ СИГНАЛОВ ПО ЛИНЕЙНОМУ ТРАКТУ ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ (57) Изобретение относится к электросвязи и м.б. использовано для оценки .готовности и качества передачи при эксплуатации и испытаниях многока» нальных цифровых систем передачи с временным уплотнением. Цель изобретения — расширение функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов (ЦС); Устр-во содержит блок 1 выделения ошибок, счетчик

2, блок 4 управления, формирователь (Ф) 5 тактовых импульсов, таймер 7 и блок 8 вычислений. В устр-во введены Ф 6 адреса, блок 3 памяти (БП).

В БП 3 для каждого низкоскоростного

ЦС выделено требуемое кол-во ячеек памяти, в которых в течение одного цикла сохраняется измеренное значение суммы ошибок данного сигнала.

В каждом такте последовательно выполняются след. операции: перенесение значения суммы ошибок данного ЦС в счетчик 2 измерения ошибок, прибавление единицы к записанному значению при наличии ошибки в ЦС, запись полученной суммы в соответствующие ячейки

БП 3. Записанное значение хранится до следующего цикла, а в следующем такте выполняются аналогичные операции для ЦС со следующим номером, задаваемым Ф 6. Накопление информации об ошибках в каждом ЦС производится до конца периода измерения. 1 ил.

1434554

Изобретение относится к электросвязи и может быть использовано для оценки готовности и качества передачи при эксплуатации и испытаниях многоканальных цифровых систем передачи с временным уплотнением.

Цель изобретения - расширение функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов.

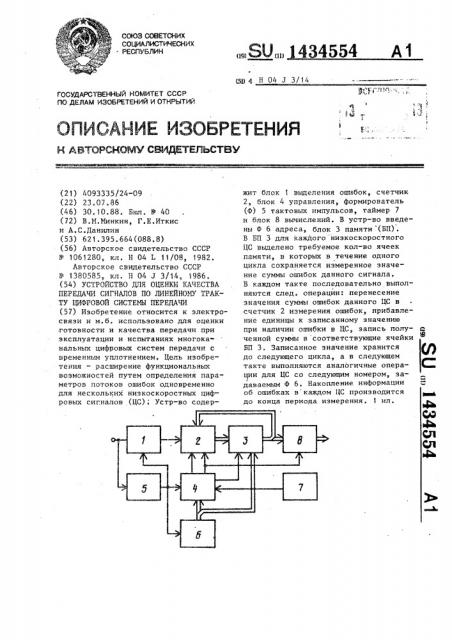

Яа чертеже приведена структурная электрическая схема предлагаемого устройства. 15

1 I

Устройство для оценки качества передачи сигналов по линейному тракту цифровой системы передачи содержит блок 1 выделения ошибок„ счетчик 2, блок 3 памяти, блок 4 управления, 20 формирователь 5 тактовых импульсов, формирователь 6 адреса, таймер 7 и блок 8 вычислений.

Устройство работает следующим образом. 25

Исследуемый сигнал образуется в результате прохождения высокоскоростного цифрового сигнала, сгруппированного из нескольких низкоскоростных сигналов (1), (2), (3), ..., через 3О линейный тракт, в котором некоторые из его символов "О", "1" принимают ошибочные значения, превращающие исходный "идеальный" сигнал в сигнал с ошибками, параметры которого (коэффициент ошибок и т.д.) подлежат измерению. Этот сигнал с ошибками подается одновременно на входы блока 1 выделения ошибок н формирователя 5 тактовых импульсов, на выходах кото- 10 рых образуются импульсы ошибок и тактовые импулЬсы соответственно.

Измерение количества ошибок в цифровых сигналах (1),(2),(3),... про" изводится следующим образом. В блоке 3 памяти для каждого низкоскоростного цифрового сигнала выделено требуемое количество ячеек памяти, в которых в течение одного цикла сохраняется измеренное значение суммы ошибок данного сигнала. В каждом такте последовательно выполняются следующие операции: перенесение значения сум" мы ошибок данного цифрового сигнала (с данным номером) в счетчик 2 измерения ошибок (режим считывания из блока 3 памяти и параллельной записи в счетчик 2); прибавление единицы: к записанному (перенесенному) значению при наличии ошибки в цифровом сигнале; запись полученной суммы в соответствующие ячейки блока 3 .памяти.

Записанное значение хранится до следующего цикла, а в следующем такте выполняются аналогичные операции для цифрового сигнала со следующим номером, задаваемым формирователем 6.

Накопление информации об ошибках в каждом цифровом сигнале (1),(2), (3),... производится до конца периода измерения..Окончание периода измерения определяется выдачей импульса с таймера 7. При поступлении этого импульса по сигналу блока 4 начинается считывание накопленных значений сумм ошибок из блока 3 памяти в блок 8.

Это производится в первой половине каждого такта по стробирующему сигналу. Этим же сигналом осуществляется установка в нулевое состояние счетчика 2. Во второй половине каждого такта производится прибавление к нулевому значению единицы (при наличии ошибки в цифровом сигнале) и запись полученного значения (нулевого или единичного) в соответствующей ячейке блока 3 памяти. Тем самым поочередно осуществляется подготовка к новому периоду измерения в ячейках памяти для каждого цифрового сигнала.

Эта процедура продолжается до тех пор, пока содержимое всех ячеек памяти не .будет перенесено в блок 8, и все они не будут подготовлены к следующе му периоду измерений. При поступлении очередного тактового импульса устройство продолжает работу в режиме измерения (накопления) ошибок.

В блоке 8, функции которого может выполнять, например, микроЭВМ, в соответствии с заданным алгоритмом осу. ществляется обработка результатов из" мерений с целью определения параметров цифровых сигналов и цифровыхтрактов: коэффициента готовности, длительностей перерывов связи и т.д.

Результаты обработки регистрируются в форме таблиц, графиков на соответствующих приборах, сопряженных с микроЭВМ.

В предлагаемом устройстве при проведении измерений подразумевается, что все каналы (цифровые сигналы) одинаковые, поэтому присваиваемые им номера (1),(2),(3),„.. условны и в общем случае не соответствуют реаль1434554

Составитель В.Смирнова

Редактор Т.Парфенова Техред М.дидык Корректор Э.Лончакова. Заказ 5565/57 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ным номерам каналов в исследуемой цифровой системе передачи. Такое упрощение вполне допустимо для большинст-. ства случаев применения предлагаемого устройства. Если же требуется точное, соответствие номеров цифровых сигналов (адресов), то необходимо подать на дополнительный установочный вход формирователя 6 импульс цикловой син- 1п хронизации с соответствующего блока цифровой синхронизации конечного оборудования линейного тракта цифровой системы передачи. При этом счетчик формирователя,6 устанавливается в ну- 15 левое состояние, и дальнейший отсчет адресов соответствует реальным номерам цифровых сигналов.

Формула изобретения щ

Устройство для оценки качества передачи сигналов по линейному тракту цифровой системы передачи, содер- жащее блок вычислений, таймер, последовательно соединенные блок выделения 25 ошибок и счетчик и последовательно соединенные формирователь тактовых импульсов и блок управления, причем вход и выход формирователя тактовых импульсов .соединены соответственно с первым и вторым входами блока выделения ошибок, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем определения параметров потоков ошибок одновременно для нескольких низкоскоростных цифровых сигналов, введены форми- рователь адреса и блок памяти, при этом выход счетчика через блок памяти подключен к информационным входам блока, вычислений и к входам параллельной записи счетчика, а выход формирователя тактовых импульсов через формирователь адреса подключен к адресным входам блока памяти и блока управления, вход меток времени и пер" вый, второй и третий выходы которого соединены соответственно с выходом таймера, с управляющим входом счетчика, с управляющим входом блока памяти и с входом обнуления счетчика, соециненным с входом стробирования блока вычислений.