Запоминающее устройство с резервированием

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам, в которых для повьшения надежности используется мажоритарное резервирование на уровне микросхем памяти. Целью изобретения является увеличение информационной емкости устройства. Устройство содержит накопитель, адресные входы которого соединены с выходами счетчика-регистра , информационные входы которого подключены к выходам умножителя на три, входы которого являются адресными входами устройства, контрольный регистр, формирователь сигнала ошибки, элементы задержки ИЛИ, И. Достижение цели изобретения обеспечивается умножением на три адреса обращения к накопителю с последующим чтением идентичной информации из каждой трети накопителя путем инкрементирования счетчика-регистра. Если в результате чтения из двух частей накопителя получены одинаковые данные , то они передаются на вьрсод устройства , в противном случае осуществляется чтение из третьей части накопителя и истинные данные определяются мажоритарным методом. Накопитель в устройстве используется полностью в отличие от устройства-прототипа, использующего только 3/4 полярной ем- 2 кости. 1 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИ4ЕСНИХ

РЕСПУБЛИК (дН 4 G 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕПЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4233082/24-24 (22) 20.04.87 (46) 15.11.88. Бюл. № 42 (72) М.И.Королев, В.И.Николаев, B.Н.Горшков, В.Г.Терехов и А.M.Çàÿö (53) 681.32?.6(088.8) (56) Авторское свидетельство СССР № 951406, кл. G 11 С 29/00, 1980.

Авторское свидетельство СССР № 1188784, кл. G 11 С 11/00, 1985. (54) ЗАПОМИНАКЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ (57) Изобретение относится к запоминающим устройствам, в которых для повышения надежности используется мажоритарное резервирование на уровне микросхем памяти. Целью изобретения является увеличение информацион— ной емкости устройства. Устройство содержит накопитель, адресные входы которого соединены с выходами счетчика †регист, информационные входы ко„„SU„„1437917 А 1 торого подключены к выходам умножителя на три, входы которого являются адресными входами устройства, контрольный регистр, формирователь сигнала ошибки, элементы задержки ИЛИ, И. Достижение цели изобретения обеспечивается умножением на три адреса обращения к накопителю с последующим чтением идентичной информации из каждой трети накопителя путем инкрементирования счетчика-регистра. Если в результате чтения из двух частей накопителя получены одинаковые данные, то они передаются на выход устройства, в противном случае осуществляется чтение из третьей части накопителя и истинные данные определяются мажоритарным методом. Накопитель в устройстве используется полностью в отличие от устройства-прототипа, использующего только 3/4 полярной емкости. 1 ил.

Изобретение относите-. к ::I=«по.."жнающим устройствам, н котор. ix для повы-шения надежности используется мажоритарное резервирование на уровне микросхем памяти.

Целью .изобретения является ув, икчение информационно.-.:.. =-;:;кости устрой-ства.

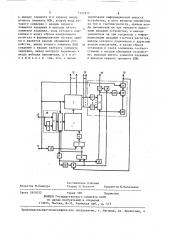

На чертеже кзобрю".н= . c:òj óêòójiiiàÿ схема предлагаемого з,::помкнаюш";i= устройстваЗапоминвющее сгройс":.зс с резс..-вкрованкем содеу,";;*-:. па:.огитель информационной емк-,ст.«.э„ в гз:. .: раза превьш1ающей треб TB;,, I для реше ;.:R задач системы. счетчик"-регистр 2 „ контрольный регкстр 3, формкрова.ел.=

4 сигнала ошибки сумматор 5„ первый

6 и второй 7 элем ..ты ИЛИ. "- — I:ö.j

И 8, первый 9, второй !0. ре и четвертый 12, пятый I3 э,... я;.еь1ть| за-держки, умножителт !,„у;то<-..й-т-вс имеет адресные входь 15,. кпформацко.;

° ные выходь1 1 î, вход: 7 обр1-,: =;-:::; .

ВЫХОД 18 СКГ,IBJ;.а P ë-"j еШЕ-:;--.= "-IXI -. т °вЂ”

11 ния, выход i9 с.:..гнала "Оы::б.=, э=: ходы 20 сигналов . - експ,:-.вныэ ра ряды

Формкров .тель сигнала слкбкк содержит группу инверторов 21, первый

22 элемент И, элемент И." .;И 23, кнвер тор 24, второй 25 эг.емен.. И,. шестой

26 элемент задержки триггер 27,, сядь мой 28 элемент задергх к, Блоки з,, представляют собой умкожк" .-.и-. 2с на трк.

Устройство ваботает слер .сшкм об. разом.

В накопитель 1, состояшкй к"- БИС оперативной клк постоянной памя":и,. количество адресов в кo!opс . :H рк раза превышает несбходк ое для рабстл вычислительного устройства ;.юбым способом записана информация, причем в каждых трех соседи :.х адресах, начь:ная с адреса, кратного туям., ..нформа-ция одинакова. На а, :;уес«ые в;:-;оды 3 устройств-. наступа."=т адрес обращения,,„

l,, который увелкчиваег;-:.;,гээс -:=, и---:в о» за, например, .путем дз.- .га е,.— один разряд:в сторону с"-.г.". Fãî вазр.:-. пает на зторой вход -.,".«матор» 5, Таким образом, на выходе су матора 5 получается адрес, в тр. .. раза превы;-шающий адрес обращения,. Зтст = .дь. -,:.с сохраняется до записи его .†:. сче"-ч. .-к ре1истр 2. Запрос, поданный на вход

17 устройства, стробирует блоки 2, 3, 4 к через пятый элемент 13 эадержкк подается на вход установки регистра счетчкка-регистра 2, разрешая ему прием адреса, к через второй 7 элем=-.нт ИЛИ к третий 11 элемент задержки поступает на вход выборки накопи".-«ля ",, Прок"водится считывание ран"е -апксанной информации по адресу, соответствующему поданному на адресныэ входы накопителя 1 коду адреса от -:чегчк,а-регистра 2. Считанная информация записывается B контрольный регистр 3, каждый разряд которого представляет собой, например, двух1 разрядный счетчик. В зависимости от содержани« считанной информации младшкй разряд каждого двухраэрядного счетчика переключается или не перез ii;Jlgji1 ет я .

После завершения первого цикла чктыванкя кз накопителя 1 происхо— ,jI-::. псзторное обращение к нему через интервал времени. задаваемый первым . .лементом задержки. При этом задержанный сигнал запроса с выхода пятого 13 элемента задержки поступает через первый вход первого б элемента ..1ЛИ на вхсд счета счетчика-регистра

2., увеличивая его содержимое на единицу„ Это обеспечивает переход к адресам второй трети накопителя 1. С

: ;D:àäà первого б элемента ИЛИ сигнал поступает на второй вход второго 7 э,1-,емента ИПИ,, с выхода которого через третий 11 элемент задержки он подается на управляющий вход выборки накопителя

При этом происходит считывание информации и= адреса другой трети накопителя 1, в котором ранее была записана та же информация, что и в вы—

pBI1BoM в предыдущем такте адреса. Считанная информация поступает на входы контрольнот.о регистра 3. Далее возможны два варианта функционирования.

1, Информация при первом и втором обращении совпадает. В этом случае после второго обращения на каждом из

:.падших разрядов двухразрядных счет=::,-кон контрольного регистра 3 устаз.вл;, ает я сигнал логического 0

Зтoi сигнал от всех разрядов контвЂ, ол:-:ного регкстра 3 поступает на пер— ые входы формирователя 4 сигнала ..-б:;ч„ даг.:ee через группу инверторов

2 . „:. входы элемента И 22. По исте1437917 чении времени, превышающего время выборки информации из накопителя, на второй вход формирователя 4 сигнала ошибки поступает сигнал от второго

10 элемента задержки, который вызывает срабатывание элемента И 22. Сигнал совпадения через элемент ИЛИ 23 выдает на выход 18 сигнал "Разрешение считывания информации, которая уста- 1р навливается после второго обращения на старших разрядах двухразрядных счетчиков контрольного регистра 3, соединенных с информационными вьходами 16. Поскольку эта информация, про- 15 веренная сравнением гри считывании из двух третей накопителя 1, признается истинной, она может быть использована процессором.

II. Информация при первом и втором 20 обращении не совпадает в одном или нескольких информационных разрядах, что является признаком неисправности накопителя 1. При этом после в-oporo обращения на выходах младших разря- 25 дов соответствующих двухразрядных счетчиков контрольного регистра 3 устанавливается логиче" êàÿ "1". После подачи сигнала от второго 10 элемента задержки элемент И 22 не срабаты- 30 вает, а на выходе 18 не появится сигнал "Разрешение считывания . На первый вход элемента И 25 через инвертор 24 подается сигнал логическои

1 . После подачи на второй вход эле- 35 мента И 25 задержанного на элементе 26 задержки сигнала от второго 10 эле1 мента задержки элемент И 25 срабатывает и вызывает переключение триггера 27. В результате этого на выходе 4О

19 устанавливается сигнал "Ошибка".

Этот сигнал подается на первый вход элемента И 8 и разрешает третье об— ращение к накопителю, так как на второй вход элемента И 8 будет подан сигнал запроса от входа 17 управле— ния через пятый 13, первый 9 и четвертый 12 элементы задержки. Через элемент И 8, первый 6, второй 7 элементы ИЛИ, третий 11 элемент задержки этот сигнал подается на вход выборки накопителя 1. Этот же сигнал с выхода первого 6 элемента ИЛИ оступает на третий управляющий вход счетчика-регистра 2, увеличивая его содержимое на единицу. При этом формируется адрес ячейки, соответствующий обращению к последней трети накопителя 1. Считанная при третьем обращении информация поступает на входы всех разрядов контрольного ре— гистра 3 и вызывает срабатывание соответствующих двухразрядных счетчиков, в результате чего на их старших разрядах и информационных выходах 16 устройства устанавливается информация, соответствующая истинной по мажоритарному принципу. После задержки на время считывания при третьем обращении, определяемой элементом 28 задержки формирователя 4 сигнала ошибки, через элемент ИЛИ 23 на выходе 18 появляется сигнал "Разрешение считывания . По этому сигналу установившаяся на информационных выходах 16 информация может быть использована процессором. Наличие на выходе 19 сигнала "Ошибка" после второго обращения обеспечивает оператору информацию о наличии неисправности в одной из третей накопителя 1, а состояние информации на выходах 20 после второго обращения позволяет локализовать ошибку с точностью до разряда.

Таким образом, в предлагаемом устройстве в отличие от устройствапрототипа накопитель 1 используется в полной мере. формула изобретения

Запоминающее устройство с резервированием, содержащее накопитель, выходы которого соединены со счетными входами контрольного регистра, выходЫ первой группы которого являются информационными выходами устройства, а вьгходы второй группы — выходами неисправных разрядов устройства и подключены к информационным входам формирователя сигнала ошибки, первый и второй выходы которого являются соответственно выходами разрешения считывания и ошибки устройства, первый и второй синхровходы формирователя сигнала ошибки соединены соответственно с выходами второго элемента saдержки и элемента И, первый и второй входы которого подключены соответственно к второму выходу формирователя сигнала ошибки и к выходу четвертого элемента задержки, вход которого соединен с выходом первого элемента задержки и с первым входом первого .элемента ИЛИ, второй вход и выход которого подключены соответственно

1437917

Составитель О.Исаев

Техред М.Ходанич Корректор М. Васильева

Редактор М,Бандура

Заказ 59GO/52

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ъ

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 к выходу элемента И и первому входу второго элемента ИЛИ, второй вход которого соединен с входом первого элемента задержки и выходом пятого элемента задержки, вход которого подключен к входу сброса контрольного регистра и формирователя сигнала ошибки и является входом обращения устройства, выход второго элемента ИЛИ 1р соединен с входом третьего элемента задержки, выход которого подключен к входу выборки накопителя, о т л ич а ю щ е е с я тем, что, с целью увеличения информационной емкости устройства, в него введены умножитель на три и счетчик-регистр, причем входы умножителя на три являются адресными входами устройства, а выходы умножителя на три соединены с информационными входами счетчика-регистра, выходы которого подключены к адресным входам накопителя, а входы сброса установки и счета соединены соответственно с входом обращения устройства, выходом пятого элемента задержки и выходом первого эпемента ИЛИ.