Способ перепрограммирования ячейки памяти на мноп- транзисторе

Иллюстрации

Показать всеРеферат

СО(ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 G 11 С 11/40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3936855/24-24 (22) 01.08.85 . (46) 15. 11. 88. Бюл. У 42 (72) В.А.Милошевский, А.П.Нагин, В.M.Òþëüêèí, А.И.Мальцев и Ю.P.×åðíüïïåâ (53) 681.327.66(088.8) (56) Мальцев А.И., Поспелов В.В. ЗУ на основе NHOII-структур. Микроэлектроника и полупроводниковые приборы/

Под ред. А.А.Васенкова и Я.А.Федотова. М.: Сов. радио, 1976, вып. 1, с. 58-76.

Авторское свидетельство СССР

У 1110315,.кл. G 11 С 11/40, 1979. (54) (57) СПОСОБ ПЕРЕПРОГРАММИРОВАНИЯ

ЯЧЕЙКИ ПАМЯТИ НА МНОП-ТРАНЗИСТОРЕ, заключающийся в подаче на затвор

МНОП-транзистора импульса напряжения запись-стирание амплитудой порога записи логической "1", о т л и ч аю шийся тем, что, с целью увеличения числа циклов перепрограммирования ячейки памяти, перед подачей импульса напряжения записи на затвор подают дополнительный импульс напряжения стирания амплитудой, которая не превышает амплитуду импульса записи.

1437918

Изобретение относится к запоминающим устройствам и может быть использовано для программирования энергонезависимых ЗУ на основе МНОП-тран5 зисторов.

Цель изобретения - увеличение числа циклов перепрограммирования ячейки памяти.

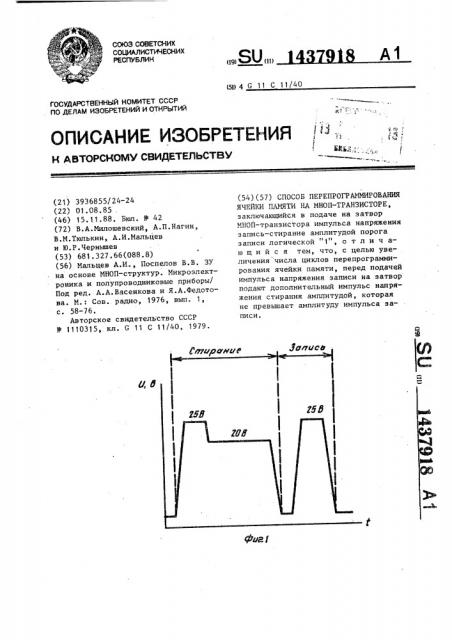

На фиг. 1 приведена временная пос" 1 ледовательность импульсов напряжения, подаваемых на затвор запоминающего

МНОП-транзистора, на фиг. 2 — зависимость пороговых напряжений элемента памяти в логических состояниях 1 — Н (1) и "0" — U (О) от числа циклов перепрограммирования, причем сплошными линиями показаны эти зависимости при преимущественной записи лог. "1" пунктиром и штрихпунктиром — зависимости при преимущественной записи лог. "0" в случае предлагаемого и известного (прототина), способов управления соответственно.

Перепрограммирование ячейки на- 25 мяти, согласно предлагаемому способу, осуществляется следующим образом.

Пусть, для определенности, низкое значение .порогового напряжения запоминающего NHOII-транзистора соответствует логическому состоянию "0", высокое — "1". Операция программирования ячейки памяти заключается в последовательном выполнении операций стирания ранее записанной информации и записи новой информации. Стирание

35 ! выполняют в два этапа: сначала проводят дополнительное стирание, подавая на затвор запоминающего МНОП-транзистора импульс напряжения стирания с амплитудой не меньшей амплитуды импульса напряжения записи, например равной ей и составляющей 25 В, и длительностью 5 мс (фиг. 1); В результате воздействия этого импульса пороговое напряжение запоминающего транзистора увеличивается и станет равным, например, 4,0 В, причем это произойдет на фоне некоторого общего сдвига межпороговой зоны этого транзистора. Затем пороговое напряжение

5О уменьшают до значения, соответствующего стертому состоянию, подавая на затвор запоминающего транзистора, например, импульс напряжения той же полярности,но с амплитудой, например, 20 В. В результате этого пороговое напряжение запоминающего транзистора уменьшается на 1,5-2,0 В, что соответствует информации лог. "О, записанной в ячейку. После этого ячейку памяти. либо оставляют в этом состоянии, либо переключают в состояние лог. "1", подавая на затвор запоминающего МНОПтранзистора импульс напряжения записи, например, с амплитудой 25 В н длительностью 1 мс. Для записи новой информации в ячейку опять повторяют описачную последовательность операций, причем эта последовательность обеспечивает значительно большее количество циклов перепрограммирования, при котором межпороговая зона ячейки памяти зависит от характера записываемой информации (фиг. 2).

Операции стирания могут выполняться как с помощью разделенных по времени импульсов, так и объединенным импульсом сложной формы. Кроме того, дополнительное стирание может быть использовано как при монополярном, так и разнополярном способе стирания информации из ячейки.

По сравнению с известными способамн перепрограммирования энергонезависимости памяти предлагаемый способ обладает следующими преимуществами: увели ывает максимальное число циклов перепрограммирования ячейки памяти не менее чем в 30-100 раз, повышает быстродействие программирования, так как дает возможность использовать сравнительно узкую межпороговую зону ячейки памяти, сохраняя при этом требуемьй ресурс ячейки по числу циклов перепрограммирования.

Реализация предлагаемого способа не практике позволит повысить долговечность и надежность БИС электрически стираемых ППЗУ и энергонезависимых

ЗУПВ, что может дать значительный экономический эффект в народном хозяйстве.

1437918

Составитель В.Лапшинский

Техред М. Ходанич Кор рек тор О. Кравцова

Редактор M.Áàíäóðà

Заказ 5900/52

Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4