Преобразователь последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в параллельный и является усовершенствованием изобретения по авт.св. № 1231613. .Цель изобретения - расширение области применения преобразователя путем обеспечения возможности съема информации , начиная с заранее определенного слова - достигается введением новых блоков и соответствующих функциональных связей между ними. 2 ил.

СО1ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А2 (19) f11) (50 4 н 03 M 9 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ (61) 1231613 (21) 4083374/24-24 (22) 02.07.86 (46) 15.11.88. Бюл. N 42 (72) В.И.Ковнир и Е.И.Цодыковский (53) 681.325(988.8) (56) Авторское свидетельство СССР

Ó 1231613, кл. Н 03 М 9/00, 1984. (54) ПРЕОБРАЗОВАТЕЛЬ. ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в параллельный и является усовершенствованием изобретения по авт.св, У 1231613. .Цель изббретення — расширение области применения преобразователя путем обеспечения возможности съема информации, начиная с заранее определенного слова — достигается введением новых блоков и соответствующих функциональных связей между ними. 2 ил.

1438007

Изобретение oтнcсится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в параплельный и является усовершенствова-нием изобретения по авr.ñâ.N 1231613., Цель изобретения — расширение области применения преобразователя путем обеспечения возможности съема информации, начиная с заранее опредеЛенного слова.

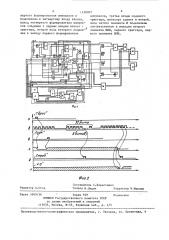

На фиг.1 представлена блок-схема 1 преобразователя последовательного ко-! да в параллельный; на фиг.2 — диаграммы, пояс:няющие его работу.

Преобразователь последовательно-а кода в параллельный (фиг.1;- содержит блок 1.1 преобразования и сопряжения, управляемый генератор 1, мультиплек- 20 сор 2, регистр 3 сдвига, блок 4 контроля нечетности, выходной регистр S, онтроллер 6, К каналов 7 преобразоваия, каждый иэ которых включает инверор 8, элементы HE 9 и 10 триггеры 25

11 — 16, формирователи 17-20 импульсов. элементы KIH 21-27 элементы И 28-33, счетчики 34-35„ регистры 36-38, блок

39 оперативной памяти, блок 40 сравнения, элемент 41 задержки. 30

Преобразователь работает следующим образом„

После включения питания в контроллере 6 вырабатывается сигнал "Сброс" (фиг.2а),. который приводит в исходное состояние все K каналов, в том числе регистр 37 сдвига, триггеры 15 и 16 в каждом из К каналов, запирая элементы И 32 и 33.

По команде Пуск", поступающей от элемента ИЛИ 22 (фиг.2в), триггер 16 перебрасывается и открывает элемент

II н

И 33. Независимо от команды Пуск поступают тактовые импульсы (фиг,2б)

:на элементы И 32 и сигнал "Пауза" на триггер 15„ По приходу первой паузы триггер !5 открывает элемент И 32 и тактовые импульсы поступают на сдвиговый регистр 37 синхронно с информаци! ей. После прихода восьмого им-

:пульса сдвиговый регистр 37 вырабаты-вает сигнал "строб" (фиг.2д).„ который поступает на элемент И 33 а также через элемент ИЛИ 27 и элемент 41." задержки на вход "Сброс" сдвигового ...35 регистра 37., Предварительно до коман-ды "Пуск" в регистр 38 адреса был занесен требуемый адрес слова, с которого надо принимать информацию в преобразователь. Это r адрес сравнивается в блоке 40 сравнения., Блок 40 сравнения имеет два выхода: выход ф 0" и выход "=0". Если после прохождения восьми импульсов срабатывает сигнал " 0" (фиг.2е), то сигнал

"Строб" проходит через элемент И 33 и обнуляет счетчик 34 адреса через элемент ИЗИ 26. Если вырабатывается сигнал =0", то сигнал "Строб" не проходит через элемент И 33, а триггер 16 сбрасывается и блокирует элемент И 33 для дальнейшего прохождения импульсов "Строб" дo прихода новогo сигнала "Пуск".

Таким образом находят нужное слово информации, и канал будет принимать информацию аналогично описанному для известного устройства.

Формула изобретения

Преобразователь последовательного кода в параллельньй по авт.св.

1Ф 1231613, отличающийся тем, что, с целью расширения области применения преобразователя путем обеспечения возможности считывания информации, начиная с заранее определенного слова, в каждый из К каналов преобразования введены пятый и шестой элементы И, пятый и шестой триггеры, регистр сдвига, блок сравнения, четвертый формирователь импульсов, седьмой элемент ИЛИ, элемент задержки и регистр адреса, информационный и управляющий входы которого подключены соответственно к восьмому и девятому входам канала преобразования, выход подключен к первому входу блока сравнения, выход пятого триггера соединен с первым входом пятого элемента И,, выход которого соединен с первым входом регистра сдвига, первый выход которого соединен с вторым входом блока сравнения,, выход которо-. го соединен с первыми входами шестого триггера и шестого элемента И, выход которого подключен к третьему. входу пятого элемента

ИЗИ, выход седьмого элемента ИЛИ через элемент задержки соединен вторым lxopoN регистра cpBBr G BTopoH выход которого соединен с первым вzoдом седьмого элемента ИП и третьим входом шестого элемента И, вторые вхОды седьмОго элемента ИПИ и шесто го TgHrÐßÄß Объединены с входом чет

Составитель С.Берестевич

Техред М.Дидык Корректор M. Шароши

Редактор А.Огар

Заказ 5969/56

Тираж 929

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, г. ужгород, ул. Проектная, 4

3 )438007

4 вертого формирователя импульсов и импульсов, третьи входы седьмого подключены к четвертому входу канала, триггера, регистра сдвига и второй„ выход четвертого формирователя импуль- вход пятого элемента И подключены сов соединен с первым входом пятого соответственно к выходам второго

5 триггера, второй вход которого подклю- элемента ИЛИ, первого триггера, пер" чен к выходу первого формирователя ного элемента ИПИ.