Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повышение помехоустойчивости путем режекции помех. Фильтр содержит частотный рециркулятор I, коммутаторы, блоки памяти 3,5 и 13, блоки ключей 4 и 11, блоки формирования (БФ) 6 и 7 верхнего и нижнего порогов, пороговый блок 9, блок дешифраторов 10, сумматоры-накопители 5, блок выбора 16 максимального числа и блок синхронизации 17. Фильтр позволяет формировать отклик на входной сигнал с более высокой помехоустойчивостью за счет использования оценок уровня входного шума и среднего значения уровня сигнала и за счет исключения при формировании порога мощных помех . Устройство по пп. 2-6 отличается выполнением БФ 6 и 7, блока выбора 16, блока синхронизации 17 и узла выбора минимального числа, входящего в состав БФ 6. Даны их ил. 5 з.п. ф-лы, 9 ил. с сл

СОЮЗ СОБЕТСНИХ

СОШ4АЛИСТИЧЕСКИХ

РЕСПУБЛИК

017 А1 (19) (1!) < 11 4 Н 04 L 27/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АBTOPCHGMV СВИДЕТЕЛЬСТВУ

1 (3

БИЫ,;

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4170978/24-09 (22) 29.12.86 ,(46) 15.11.88. Бюл. Р 42 (72) B.A.Сивов, И.Г.Вяткин, С.Н.Чистяков и В.И.Прытков (53) 621.376.5 (088.8) (56) Авторское свидетельство СССР

Ф 1225040, кл. Н 04 L 27/26, 1984. (54) ЦИФРОВОЙ СОГЛАСОВАННЬ111 ФИЛЬТР

СИГНАПОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение помехоустойчивости путем режекции помех. Фильтр содержит частотный рециркулятор 1, коммутаторы, блоки памяти 3,5 и 13, блоки ключей 4- и

11, блоки формирования (БФ) 6 и 7 верхнего и нижнего порогов, пороговый блок 9, блок дешифраторов 10 сумматоры-накопители 15, блок выбора 16 максимального числа и блок синхронизации 17. Фильтр позволяет формировать отклик на входной сигнал с более высокой помехоустойчивостью за счет испольsîâàíèÿ оценок уровня входного шума и среднего значения уровня сигнала и за счет исключения при формировании порога мощных помех. Устройство по пп, 2-6 отличается выполнением БФ 6 и 7, блока выбора 16, блока синхронизации 17 и узла выбора минимального числа, входящего в состав БФ б. Даны их ил. 5 з.п. ф-лы, 9 ил.

1438017

Изобретение относится к радиотех= нике и может быть использовано для приема цифровых сигналов в системах с дискретной частотной манипуляцией.

Цель изобретения — повышение помехоустойчивости путем режекции помех.

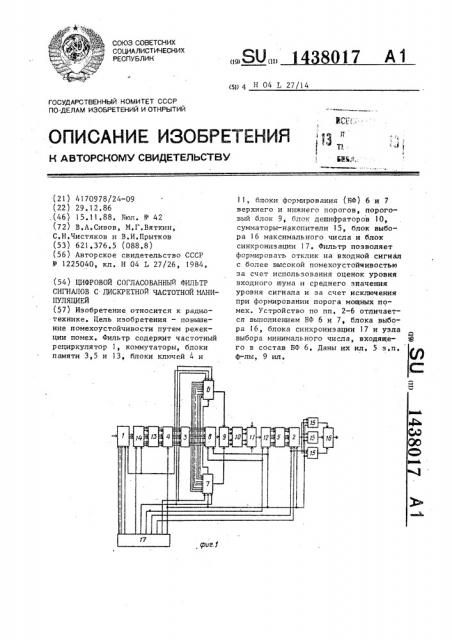

На фиг, I. изображена структурная электрическая схема предлагаемого согласованного »bHJIbTpB> на фиг. 2— структурная электрическая схема час1 тотного рециркулятора; на фиг. 3— структурная электрическая схема блока формирования верхнего порога; на ! фиг, 4 — структурная электрическая f5 схема блока выбора максимального числа; на фиг. 5 — структурная электрическая схема узла выбора минимального числа; на фиг. 6 — структурная электрическая схема блока формирова- 2р ния нижнего порога; на фиг. 7 — структурные электрические схемы порогового блока, блока дешифраторон, второго блока ключей и первого кйммутатора; на фиг. 8 . — структурная электри- 25, ческая схема блока синхронизации; на

: фиг. 9 — временные диаграммы работы блока синхронизации.

Цифровой согласованный фильтр сигналов с дискретной частотной манипу- 3р ляцией (ДЧМ) содержктт частотный . рециркулятор 1, первый коммутатор 2,, первый блок 3 памяти, первый блок 4 ключей, второй, блок 5 памяти, блок б формирования верхнего порога, блок 7 формирования нижнего порога, второй коммутатор. 8, пороговый блок 9,блок

10 дешифраторов, второй блок 11 ключей, третий коммутатор 12, третий блок 13 памяти, четвертьп» коммутатор »0

14, сумматоры-накопители 15, блок 16 выбора максимального числа и блок 17 синхронизации.

Частотный рециркулятор образуют

»»а»»о»»ители 1 8, каждый из тоит из первого и второго преобразователей 19 и 20 частоты, фазосдвигающего элемента 21, перного и второго фильтров 22 и 23, перного и второго аналого-цифровых преобразователей

{ЛЦП) 24 и 25, первого и второго регистров 26 и 27, первого и нторого сумматоров 28 и 29, третьего и четвертого регистров 30 и 31> первого перемножителя 32, блока 33 весовых коэффициентов (БВК), второго, третье55 го и четвертого перемножителей 3436, третьего и четвертого сумматоров

37 и 38, первого и второго квадраторов 39 и 40, пятого сумматора 41 и ключа 42, Блок формирования верхнего порога включает первый коммутатор 43, узел

44 ныбора максимального числа, второй коммутатор 45, запоминающий узел 46, узел 47 ключей, узел 48 выбора минимального числа, перемножитель 49,сумматор 50 и регистр 51.

Блок выбора максимального числа содержит первый, второй и третий компараторы 52 — 54, с первого по шестой ключи 55 — 60.

Узел выбора минимального числа образуют первый, второй и третий компараторы 61 — 63, с первого по шестой ключи 64 — 69.

Блок формирования нижнего порога содержит коммутатор 70, узел 71 выбора минимального числа, сумматор-накопитель 72, делитель 73, перемножнтель 74 и регистр 75.

Пороговый блок включает первый и второй пороговые узлы 76 и 77 °

Блок дешифраторов состоит из первого, второго и третьего дешифраторов 78 — 80, Второй блок клячей содержит первый, второй и третий клячи 81 — 83.

Первый коммутатор содержит коммутатор 84 первой ступени и коммутатор

85 нторой ступени.

Блок синхронизации включает задающий генератор 86 первый, второй и третий делители 87 — 89 частоты, узел 90 деши@раторов, перньп», второй и третий ключи 91 — 93, счетчик 94 импульсов и дешифратор 95, Фильтр работает следующим образом.

Входной сигнал, состоящий из аддитивной смеси шумов, гармонических и другого рода помех и полезного сигнала с ДЧИ н виде последовательности радиоимпульсон, каждый из которых передается на своей, отличной от других, частот (d ;, где i =. 1, М, поступает на вход цифрового частотного рециркулятора l, В каждом из накопителей 18 сигнал поступает на сигнальные входы преобразователей 19 и 20 частоты, на опорные входы которых поступают опорные сигналы: на преобразователь 19 частоты — непосредственно, на преобразователь 20 частоты — через фазосдвигающий элемент 21 на 90 . На выходах преобразователей 19 и 20 частоты об20

14380 разуются квадратурные сигналы, кото-. рые и подвергаются дальнейшей обработке. Они проходят через фильтры

22 и 23, выделяющие разностную или

5 суммарную частоту входного и опорного сигналов. Колебания с выходов фильтров 22 и 23 поступают на входы

АЦП 24 и 25, которые с частотой дискретизации РА образуют отсчеты сигнала в виде двоичных чисел, пропорциональных уровню входного сигнала. Двоичные числа с выходов АЦП 24 и 25 записываются в регистры 26 и 27, в которых они хранятся на интервале дискретизации и используются для дальнейшей обработки. Суть ее заключается в накоплении энергии входного сигнала в каждом из < квадратурных каналов накопителя 18 с последующим суммированием сигналов с выходов квадратурных ветвей. Процесс накопления проходит следующим образам. При первом шаге число A cosQ;t,, запомненное в регистре 26, подается на 25 сумматор 28, где суммируется с числом из регистра 30, в котором в начальный момент было записано ччсло О.

Сумма с выходов сумматора 28

А cosa;t< + О поступает на вход пе- З0 ремножителя 32, на второй вход которого поступает весовой коэффициен г сов Щ;из БВК ЗЗ. На выходе перемножителя 32 образуется произведение

А созЯ;1 cos 6 ;. Величину dq; выбира- З ют исходя из соотношения периода анализируемой частоты Т; = 2Л/сд; и числа выборок на периоде Т„, т.е. периода дискретизации Тд, Число с выхода сумматора 28 одновременно посту- 40 пает и на вход перемножителя 34, на второй вход которого подается коэффициент sin 6су, из БВК 33. На выходе перемножителя 34 формируется следующее число: А созЯ;1 sindhi;. Аналогич- 45 ные операции выполняются на первом такте и во втором квадратурном канале: из регистра 27 поступает на сумматор 29 число А sinQ;t,, которое суммируется с нулем из регистра 38, сумма подается на перемножитель 35, формирующий число А sin(2;ticos Щ;, и на перемножитель 36, формирующий

Ф число.А sin(0;t, sindhi . С выходов перемножителей 32 и 36 числа поступают на вход сумматора 37, на выходе которого появляется числа А соз(2;t х х cos dq; — А з* пса;1, sining@., А cos(Q;t, +

+ hg;), Числа с выходов перемножите17

4 лей 34 и 35 поступают на вход сумматора 38, на выходе которого формируется число А cosa;t sindhi; +

+ А sine;t,ñosÙ; = А sin(co;t< +

+ ЬЦ ; ), Число с выхода сумматора 37 записывается в регистр 30, число с выхода сумматора 38 — в регистр 33.

На втором шаге в регистры 26 и 27 записываются числа А cos(a;t и

А sino),t соответственно. По описанной процедуре эти числа обрабатываются, получаются числа: на выходе сумматора 28 А соз (а,t < + 2 dg;) +

+ А cos(Q,tg + Ьс ;); на выходе сумматора 29 А sin(Q; t 4- 2Ьу;) +

+ А sin(CD;t + dg; ). С учетом усло» вий выбора значения 6 Ц); и при условии 1 = КТд, где ТА - период дискретизации; 1 (Кс И, где N — число шагов за время, равное длительности посылки сигнала, эти числа будут соответственно равны 2А cosg,2Òä и

2А sing;?T . После N шагов за время

Т = 1ЧТ4 будут накоплены числа: на выходе. сумма тора 29 — число

NA зЫЯ;№4, на выходе сумматора

28 — число NA cosco;¹>, Эти числа, прошедшие через квадраторы 39 и 40, суммируются сумматором 41, на выходе которого будет число S;(N)

= А N cos Я;ИТА + А N sin я;№А

= А N, После окончания N выборок числа S; (N) с каждого из накопителей 18 считываются через ключи 42 на входы коммутатора 14, а импульсом с блока 17 синхронизации регистры

30 и 31 устанавливаются в нулевое состояние.

Числа Я"(N) с выходов накопителей

18 подаются на входы коммутатора 14, который переключается с частотой следования элементов ДЧМ сигнала и соединяет одновременно выходы всех M накопителей 18 с M ячейками блока 13 памяти. Условно блок 1 3 памяти можно представить в виде квадратного поля ячеек памяти, размерностью М х М ячеек. В первый момент опроса числа

S;,(И) = S « (N), S м,(И) с первого по

M-e записываются в М ячеек первого столбца, во второй момент опроса числа S; (N) = Я,Ä(N), S«Ä(N) записываются в M ячеек второго столбца ячеек и т.д. Таким образом, J-й столбец ячеек блока 13 памяти содержит отсчеты j-ro момента опроса, а i-.ÿ строка ячеек содержит отсчеты входного сигнала, сделанные на i-й частоте. При

5 14380 этом полезный сигнал, который в каж-, дый интервал анализа присутствует только на одной иэ частот, будет занимать М ячеек блока 13 памяти— по одной в каждом столбце и в каждой строке поля ячеек. Если на входе согласованного фильтра действует узкополосная помеха, ее отсчеты займут всю соответствующую строку ячеек бло- 1р

;.ка 13 памяти.

Для того, чтобы облегчить вопросы синхронизации, согласованный фильтр ,строится таким образом, что сначала 15

1 заполняются двоичными числами Б"

11 все M х М ячеек блока 13 памяти, затем подается импульс перезаписи на блок 4 ключей и все зти числа одновременно переносятся в блок 3 памяти 20 аналогично блоку 3 памяти с тем, чтобы обработать числа по описанному ниже алгоритму параллельно с работой частотного рециркулятора 1. по заполнению очередными отсчетами входного сигнала ячейки блока 13 памяти.

При воздействии входных сигналов в вице двоичных чисел первой строки из блока 3 памяти Б (N) на разрядо- 30 вые входы компаратора 52 на бдном из его выходов появляется разрешающий потенциал: на верхнем в случае

S Ä (N) ) S, (N), на среднем — в случае S «(N) Я

56, с управляющим первым входом ко, торого соединен третий выход компаратора 52, открывается при

Б S ц (N). Выходы ключей 55 и

56 объединены, следовательно, на пер- 45 вом входе компаратора 53 появляется большее из двух входных чисел Бд (N) и S « (N). На второй вход компаратора 53 подается третье из сравниваемых чисел S, (N). Компаратор 52 и 5О ключи 57 и 58 работают аналогично описанному, следовательно, на объединенных выходах ключей 57 и 58 может появиться только одно из сравниваемых чисел Б „ (N), S (1) и S „ (N), 55 а именно наибольшее из них. На выхо-де узла 44 выбора максимума числа через время установления также появляется наибольшее иэ сравниваемых чн"

17 6 сел Б 1 (И) м „с. Это число через ком=мутатор 43 подается на узел 46 памяти, состоящий из М ячеек памяти. С подключением к узлу 44 выбора максимального числа коммутатором 45 второй строки ячеек памяти блока 3 памяти наибольшее число иэ новых М чисел

S (N) коммутатором 43 будет под1 ключено и записано во второй ячейке узла 46 памяти, таким образом, после анализа содержимого всех строк ячеек блока 3 памяти в узел 46 памяти будут записаны М наибольших чисел — по од" ному из каждой строки. После этого узлом 47 ключей ячейки узла 46 памяти будут подключены к входам узла 48 выбора минимального числа, При сравнении чисел Я (1 (N)ease и Я (И) „с раэрешаюицгй потенциал на верхнем выходе компаратора появляется, как и в узле 44 выбора максимального числа, в случае Б<1(И)„„,„,.

Б21(N)ìàêñ H HHKHPM TIPH

S (N) „„ñ) S„(N) „акс . Входы ключей

64,65,67 — 69 включены перекрестно, т,е. к сигиальному второму входу ключа 64 подключен первый вход компаратора 61, а к первому входу ключа

65 — второй вход компаратора 61. Следовательно, разрешающий потенциал от действия большего числа открывает ключ 64 (65), который пропускает меньшее из сравниваемых чисел. На объединенных выходах ключей 64, 65 появляется меньшее из двух сравниваемых чисел, а на выходе всего узла 48 выбора минимального. числа появляется наименьшее из сравниваемых макси-. мальных чисел> т ° P ° Б 1(N)мак,мкя °

Наименьшее иэ максимальных чисел

Я, (И) м „„„с выхода узла 48 выбора минимального числа подается на вход перемножителя 49, к второму входу которого прпложено двоичное число

С выхода перемножителя 49 число

II, Б 1 (N)макс,мин подается на один вход сумматора 50, на второй вход ко" торого подается двоичное число с выхода блока 7 формирования нижнего порога. Выход сумматора 50 соединен с входом регистра 51, выход которого является выходом блока 6 формирования верхнего порога, Он соединен с первым (опорным) входом порогового блока 9.

Коммутатор 70 подключает к входам узла 71 выбора минимального числа

438017

ЗО

7

1 ячейки блока 3 памяти, образующие столбец, т.е. анализу подвергаются отсчеты, сделанные в один из,)-х моментов времени во всех частотных каналах. Узел 71 выбора минимального числа выбирает наименьший из отсчетов, соответствующий. каналу с шумами, т.е. каналу, в котором в момент формирования отсчета заведомо отсутствовали полезный сигнал и помехи.

С выхода узла 71 выбора минимального числа минимальное число из столбца S;> (N) щ„„подается на вход сумматора-йакопителя 72, который суммирует M чисел — по одному из столбца..

Двоичное число, равное сумме чисел, подается далее на делитель 73 на М, результат с выхода которого поступает на перемножитель 74, на второй вход которого подается двоичное число 1, являющееся коэффициентом при формировании нижнего порога,Двоичное число с выхода перемножителя

74 подается на вход регистра 75 для запоминания, с выхода которого оно подается на второй (опорный) вход порогового блока 9. Одновременно число с выхода перемножителя 74 подается на вход сумматора 50. Таким образом, нижний порог формируется в м виде II„= 1 —; S;,,И )м„,11

Б(И)„„,„, при этом выбирается из условия максимальной вероятности обнаружения сигнала при заданной вероятности пропуска сигнала. Верхний порог формируется в виде П вЂ” — П,, +, +,S.; (И)„„, при этом выбирается из условия максимальной вероятности обнаружения сигнала при его наличии при заданной вероятности ложных тревог.

II8 ) Б, (И) ) TI„, а дешифратор 80 — на случай П > Б; (N) ) Пд, Выходы блока

1)

10 дешифраторов соединены с (управляющими) входами блока 11 ключей, состоящего из трех ключей 81 — 83.

На объединенные сигнальные входы ключей 81 и 83 подается логический нуль, а на сигнальный вход ключа 82 — логическая единица. Поскольку разрушающий потенциал не может появиться одновременно на выходах двух или трех дешифраторов 78 — 80, то ключи 81

83 открываются по одному и пропуска15 ют ка выход ту или иную двоичную цифру (О или 1) в зависимости от соотношения уровня сигнала и порогов,Таким образом, производится замена двоичных чисел Я, (N) двоичными циф20 рами. в том случае, когда число

S 11(N) лежит между порогами .(меньше большего и больше меньшего порога), оно заменяется логической единицей, если число S;;(N) превышает верхний порог или оно меньше нижнего порога, оно заменяется логическим нулем, Двоичные цифры с выхода блока 11 ключей подаются на вход коммутатора

12, который работает абсолютно синхронно с коммутатором 8: каждой ячейке блока 3 памяти с содержанием

Я (И) коммутатор 12 ставит в соответствие ячейку блоки 5 памяти с за11 сылаемой в нее двоичной цифрой 0 или

1. Таким образом, в блоке 5 памяти после анализа всех М х М чисел из блока 3 памяти будет записано М х М нулей и единиц: так, где в блоке 3 памяти записано число II„ c S; (N), в блоке 5 памяти будет записана едйница, во всех остальных случаях в блоке 5 памяти залишутся нули.

Коммутатор 8 поочередно, по одно- 45 му, подает числа Я (N) из блока 3 памяти на (сигнальный) третий вход порогового блока 9, В пороговом блоке 9 эти числа подаются на входы пороговых узлов 76 и 77 и сравниваются о порогами П> и II> Выходы поро" говых узлов 76 и 77 соединены с входами блока 10 дешифраторов, который состоит из трех дешифраторов 78 — 80.

Дешифратор 78 устроен так, что на

его выходе появляется разрешающий потенциал при состоянии пороговых узлов 76 и 77, когда S; (И)>П, II„, де- шифратор 79 реагирует на случай

После заполкекия всех ячеек блока

5 памяти начинается анализ содержимо"

ro с целью обнаружения сигнала, К ячейкам блока 5 памяти подключены входы (двухступенчатого) коммутатора

1, состоящего из двух последовательно включенных коммутаторов 84 и 85.

Коммутатор 84 первой ступени имеет 2

М входов (по числу ячеек блока 5 памяти) и один выход, коммутатор 85 второй ступени — один вход и M выходов, соединенных с входами сумматоров-какопителей 15. Запуск коммутатора 85 происходит в M раз реже, чем коммутатора 84, таким образом, в каждом из сумматоров-накопителей 15 про38017 10

9 14 исходит накопление содержимого M ячеек блоке 5 памяти.

Работа согласованного Фильтра синхронизируется управляющими напряжениями с выхода блока 17 синхронизации. После заполнения отсчетами

S, (И) блока 13 памяти все М чисел

2 перезаписываются в блок 3 памяти и анализ их производится параллельно с работой частотного рециркулятора

1 по заполнения очереднь»ми отсчетами блока 13 памяти. За время анали| за поочередно выполняются основные операции: формирование порогов II > и П, сравнение М чисел из блока 3 памяти с порогами и заполнение блока

5 памяти, формирование отклика согласованного фильтра сумматорами-накопителями 15 и его выбор блоком 16 выбора максимального числа.

Задающий генератор 86 формирует »»сходное синусоидальное колебание с тр ебуемыми параметрами — частотой, амплитудой, стабильностью и т.д. Сиг1 .;нал с вь»хода задающего генератора

86 подается на делители 87 — 89 частоты. Дели» ель 87 частоты формирует опорные частоты Сд < ....СО,, подавае» мые в качестве гетеродинных колебаний нл преобразователи 19 и 20 частот накопителей 18. Делитель 88 частоты формирует импульсную последовательность с частотой дискретизации

Р, подаваемую на все одновременно накопители 18 частотного рециркулятора 1 ° Зтой последовательностью производится управление ЛЦП 24 и 25.Де-литель 89 частоты формирует сетку импульсных последовательностей. Формируются последовательности со следующими частотами: 4МРз, 4, 21з, 1- -„

2Г /М z» F /М =- F Здесь Уз — частота следования импульсов ДЧМ-сигнала;

M — число импульсов сигнала в перио-де перебора частот, т.ее число час тот, формирующих ДЧМ-сигнал. Выходы каскадов делителя 89 частоты с частотами 2F /М и F /М подаются на входы узла 90 деиифрлторов, который формирует стробы для управления ключами

91 — 93, Клич 91 управляется первым стробом, кличи 92 и 93 — соответственно вторым и третьим стробами (фиг.9л,б,в). Через клячи 91 — 93 в моменты действия стробов проходят импульcrrrre последовательности на входы коммутаторов 4,8 и 12 и на входы

45 ключей 91 — 93. Через кляч 91 проходит импульсная последонателвность

2Р, через ключ 92 — последовательность 4М1"н, через ключ 93 — последовательность 4MF и 4Рз (фиг. 9 r, д, е, ж). На фиг.9э приведена последовательность с часто" îé F При этом принято, что M = 8, л на фиг.9 д,е изображены условно 64 импульса.

Счетчик 94 импульсов и дешифратор 95 формируют строб (фиг.9и) для управления узлом 47 ключей и регистрами

5l и 75. Счетчик 94 считает число импульсов, прошедших через ключ 91, с тем, чтобы с приходом последнего импульса на ныходе дешифратора 95 сформировался строб-импульс, который открыл бы узел 47 кличей, чтобы подать содержимое ячеек узла 46 памяти па входы уэлл 48 выбора минимального числа. Срезом строба управляются (включаются на э апись) регистры 51 и

75. Коммутаторы 14,8,12,43,70,84 и

85 устанавливаются в исходное состояние один раз за период перебора частот импульсом с частотой Р—— F>/Ì (фиг.9к). С такой же частотой производится опрос блока 4 кх»»очей, сброс сумматоров 50 и 72 и сумматорон-накопителей 15. Импульсные последовательности для управления члстотным рециркулятором I коммутатором 14 и блоком 4 ключей подаются, минуя ключи 91,92 и 93.

Таким образом, согласованный фильтр Д»81-сигнала позволяет формировать отклик на входной сигнал с более высокой помехоустойчивостью за счет использования оценки уровня входного шума и зл счет оценки среднего значения vpoHHH сигнала и исключения при Формировании порога мощHbIx помех.

Формула и з о бр ет ения

1. Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией, содержащий частотный рециркулятор, первые входы синхронизации которого подключены к первым выходам блока с»»нхро»»изл»,и»», второй выход которого соединен с первым входом синхронизацин, первого коммутатора и с т»ервыми входами сумматоров-накопителей, вторые входь» которых подключены K третьему ныходу блока сипхронизлцни, перныи блок ключей,, первый

1438017 12 рой вход которого подключен к второму выходу блока формирования нижнего порога, второй вход синхронизации которого соединен с вторым входом синхронизации блока формирования верхнего порога и с шестым выходом

ы блока синхронизации, седьмой выход которого подключен к третьему входу - 10 синхронизации блока формирования д верхнего порога и к третьему входу синхронизации блока формирования нижнего порога, выход второго коммутатора соединен с третьим входом порого15 вого блока, выходы которого подключены к соответствующим входам блока дешифраторов, восьмой .выход блока синхронизации соединен с вторым входом синхронизации четвертого коммута20 тора, второй вхсд синхронизации третьего коммутатора соединен с четвертым выходом блока синхронизации, при этом сигнальный вход частотного рециркулятора является сигнальным входом цифрового согласованного к фильтра, первым и вторым опорными входами которого являются первый и второй опорные входы второго блока ключей, выхопом цифрового согласована З0 ного фильтра является выход блока выбора максимального числа.

I блок памяти, выходы которого соедине ны с соответствующими входами второго коммутатора, первый вход синхронизации которого подключен к четвертому выходу блока синхронизации, пороговый блок, блок выбора максимального числа, входы которого подключен к выходам сумматоров-накопителей, третьи входы которых подключены к вь ходу первого коммутатора, второй вхо синхронизации которого подключен к пятому выходу блока синхронизации, отличающийся тем, что, с целью повышения помехоустойчивости путем режекции помех, введены третий и четвертый коммутаторы, второй и третий блоки памяти, блок формирования верхнего порога, блок формирования нижнего порога, второй блок ключей и блок дешифраторов, выходы кото рого соединены с соответствующими сигнальными входами второго блока ключей, выход которого соединен с сигнальным входом третьего коммутато ра, выходы которого через второй бло памяти подключены к соответствующим сигнальным. входам первого коммутатора, третий вход син .poíèýàöèè которого соединен с третьим выходом блок синхронизации, с первым входом синхронизации третьего коммутатора, с вторым входом синхронизации второго коммутатора, с первым входом синхронизации блока формирования верхнего по- g5 рога, с первым входом синхронизации блока формирования нижнего порога, с входом синхронизации первого блока ключей, с первым входом синхронизации четвертого коммутатора и с вторым 40 входом синхронизации частотного рециркулятора, выходы которого соединены с соответствующими сигнальньпж входами четвертого коммутатора, выходы которого соединены с соответ- 45 ствующими сигнальными входами третьего блока памяти, выходы которого через первый блок ключей подключены к соответствующим сигнальным входам первого блока памяти, выходы которо- я0 го соединены с соответствующими сигнальными входами блока формирования верхнего порога и с соответствующими сигнальными входами блока формирования нижнего порога, первый выход которого соединен с дополнительным входом блока формирования верхнего порога, выход которого подключен к первому входу- порогового блока,вто2. Фильтр по п.l, о т л и ч а ю—

1 шийся тем. что блок формирования верхнего порога содержит регистр, сумматор, перемножитель, узел выбора минимального числа, узел ключей, запоминающий узел, два коммутатора и узел выбора максимального числа, выход которого соединен с сигнальным входом первого коммутатора, выходы которого через запоминающий узел подклю ены к сигнальным входам узла ключей, выходы которого через узел выбора минимального числа соединены с первым входом перемножителя, выход которого соединен с первым сигнальным входом сумматора выход которого соединен с сигнальным входом регистра, первый вход синхронизации которого соединен с входом синхронизации узла ключей, перва".": вход синхронизации первого коммутатора соединен с первым входом синхронизации второго коммутатора, второй вход синхронизации которого соединен с вторым входом синхронизации первогi коммутатора, с вторым входом синхронизации регистра и с входом синхрониизации суммато14

4380)7

10

20

1З

1 ра, входы узла выбора максимального числа подключены к выходам второго

Коммутатора„сигнальные входы которого являются сигнальными входами блока формирования верхнего порога,дополнительным входом которого является второй вход сумматора, первый и

Второй входЬ1 синхронизации второго коммутатора являются соответственно торым и первым входами синхронизаии блока формирования верхнего поога, третьим входом синхронизации оторого является первый вход синхонизации регистра, выход которого бвляетоя выходом блока формирования верхнего порога, опорным входом которого является второй вход перемножения, 3, Фильтр по п.1, о т л и ч а ю—

Ш и и с я тем, что блок формирования нижнего порога содержит регистр„ еремпожитель, делитель, сумматор акопитель, узел выбора минимальнот о исла и коммутатор, выходы которого оединены с входами узла выбора минимального числа, выход которого соединен с входом сумматора-накопителя, выход которого через делитель соедиНен с первым входом перемпожителя, Выход которого соединен с входом регистра, первый вход синхронизации

Которого соединен с первым Входом

Синхронизации сумматбра-накопителя ц первым входом синхронизации коммуа, àòîðà, второй вход синхронизации

Которого соединен с вторым входом

Синхронизации сумматора-накопителя и является вторым входом синхронизации блока формирования нижнего порога, Первым и третьим входами синхронизаЦии которого являются соответственно первый вход синхронизации коммутатора и второй вход синхронизации регнСтра, сигнальные входы коммутатора являются сигнальными входами блока формирования нижнего порога, первым

И вторым выходами которого являются соответственно выход перемножителя и выход регистра, при этом второй вход перемножителя является опорным входом блока формирования нижнего порога.

4. Фильтрпоп.1, отлич аюп и и с я тем, что. блок выбора

Максимального числа содержит шесть кличей и три компаратора, при этом

Первый и второй выходы первого компаратора соединены с первым входом первого клича, второй вход которого соединен с первым входом первого компаратора, третий выход которого соединен с первым входом второго ключа, второй вход которого соединен с вторым входом первого компаратора, выход первого ключа соединен с выходом второго ключа, с первым входом третьего ключа и,с первым входом второго компаратора, второй вход ко- . торого соединен с первым входом четвертого ключа, второй вход которого подключ ен к п ерв ому выходу в торо го компаратора, второй и третий выходы которого подключены к второму входу третьего ключа, выход которого соединен с вьглодом четвертого ключа, с первым входом пятого клича и первым

I входом третьего компаратора, второй вход которого соединен с первым входом шестого клича, в-орой вход которого соединен с первым выходом третьего компаратора, второй и третий выходы которого соединены с вторым входом пятого ключа, выход которого подключен к выходу шестого KJII0 ча и является выходом блока выбора максимального числа, входами которого лвляютсл первый и ВтОрОй ВхОды первого компаратора, второй вход второг о компаратора и Второй вход третьего компаратора.

5. Фильтр по п.1, о т л и ч а и— шийся тем, что блок синхронизации содержит три ключа, три делителя частоты, узел дешнфраторов, счетчик импульсов, дешифратор и задающий генератор, первый выход которого соединен с первым вхоцом первого делителя частоты и первым входом второго делителя частоты, второй выход задающего генератора подк почек к входу третьего делителя частоты, первый и второй Выходы которого соединены с первым и вторым входами узла дешифраторов,первый, второй и третий выходы которого соединены с первымн Входами соответственно первого, второго и третьего ключей, вторые Входы которых подключены соответственно к третьему, четвертому и пятому Выходам третьего делителя частоты, шестой выход которого соединен с первым ВХОДом счетчика импульсов, Выходы которого подключены к входам дешифратора, выход первого клича соединен с вторым входом счетчика импульсов, второй вход второго

1438017

16 ключа подключен к третьему входу третьего ключа, первый и второй выхоI ды которого являются соответственно четвертым и пятым выходами блока синхронизации, первыми выходами которого являются выходы первого и второго. делителей частоты, выход второго ключа является вторым выходом блока синхронизации, третьим, шестым, седьмым и восьмым выходами которого являются соответственно шестой выход третьего делителя частоты, выход первого ключа, выход дешифратора и седьмой выход третьего делителя частоты.

6. Фильтрпоп,2, отличаю— шийся тем, что узел выбора минимального числа содержит три компаратора и шесть ключей, при этом первый и второй выходы первого компаратора соединены с первым входом первого ключа, второй вход которого соединен с первым входом первого компаратора, второй вход которого соединен с первым входом второго ключа; второй вход которого подключен к третьему выходу первого компаратора, выход первого ключа соединен с выходом второго ключа, с первым входом третьего ключа и с первым входом второго компаратора, второй вход которого соединен с первым входом четвертого ключа, второй вход которого подключен к первому и второму выходам вто -"

10 рого компаратора, третий выход которого подключен к второму входу третьего ключа, выход которого соединен с выходом четвертого ключа, с первым входом пятого ключа и первым

15 входом третьего компаратора, второй вход которого соединен с первым входом шестого ключа, второй вход кото. рого подключен к первому и второму выходам третьего компаратора, третий

20 выход которого соединен с вторым входом пятого ключа, выход которого соединен с выходом шестого ключа и является выходом узла выбора минимального числа, входами которого яв25 ляются первый и второй входы первого компаратора и вторые входы второго и третьего компараторов.

1438017

) 438017

1438017

Мак,." м а.

Составитель О.Геллер

Техред JI.Олийнык

Корректор О.Кравцова

Редактбр А,Огар

Заказ 5971/57 Тираж 660

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4