Устройство для сравнения чисел

Иллюстрации

Показать всеРеферат

Изобретение, относится к вычислительной технике, может быть использовано в качестве устройства допусковой оценки при реализации технических средств дискретной автоматики и вычислительной техники и является усовершенствованием устройства по авт.св. СССР 1285461. Цель изобретения - повышение достоверности результатов сравнения с згчетом допустимой погрешности с изменением допуска в зависимости от величины сравниваемых чисел. Устройство для сравнения чисел содержит элементы И-НЕ 1, 2, 11, 21, элементы И-ИПИ 3, 4, элемент НЕ 5, триггеры 6-10, 19, сдвиговый регистр 20. Сдвиговый регистр 20, на информационные входы которого подается код заданной погрешности , обеспечивает задание требуемой допустимой разности сравниваемых чисело Триггер 9,предназначен для установки регистра 20 в режим параллельной записи вхвдной информации или в режим вьщачи информации в последовательном коде по сигналу с элемента И-НЕ 21, фиксирующего появление единицы в старшем разряде одного из сравниваемых чисел 1 ил. (Л

союз совктсних социалистичесних

РЕСПУБЛИН

09) (11) (5D 4 G 06 F 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСИОМУ СВИДЕТЕЛЬСТЕУ госуддрствснный номитет ссср по дала изоь1 етений и ото ыти: (61) 1285461 (21) 4235494/24-24 (22) 27.04.87 (46) 23.11.88. Бюл, У 43 (72) В.И.Петухов и И.З.Лимановский (53) 681 ° 328.5 (088.8) (56) Авторское свидетельство СССР

И 1285461, кл. G 06 F 7/02, 1985, (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ (57) Изобретение относится к вычислительной технике, может быть иснользовано в качестве устройства допусковой оценки при реализации технических средств дискретной автоматики и вычислительной техники и является усовершенствованием устройства по авт.св. СССР 1Г 1285461. Цель изобретения — повышение достоверности результатов сравнения с учетом допустимой погрешности с изменением допуска в зависимости от величины сравниваемых чисел. Устройство для сравнения чисел содержит элементы

И-НЕ 1, 2, 11, 21, элементы И-ИЛИ 3, 4, элемент HH 5, триггеры 6-10 19 сдвиговый регистр 20. Сдвиговый регистр 20, на информационные входы которого подается код заданной погрешности, обеспечивает задание требуемой допустимой разности сравниваемых чисел. Триггер 9.предназначен для установки регистра 20 в режим параллельной записи Вхбдной ин формации или в режим выдачи информации в последовательном коде по сигналу с элемента И-НЕ 21, фикси« руюшего появление единицы в старшем разряде одного из сравниваемых чисел. 1 ил, С::

Изобретение относится к вычисли.тельной технике, может быть использовано в качестве устройства допусковой оценки при реализации техни-ческих средств дискретной автоматики и вычислительной техники и является усовершенствованием устройства по авт.св. Р 1285461.

Цель изобретения — повьппение дос- 1О товерности результатов сравнения кодов чисел с учетом допустимой погрешности с изменением допуска в за висимости от величины сравниваемььх чисел. $$

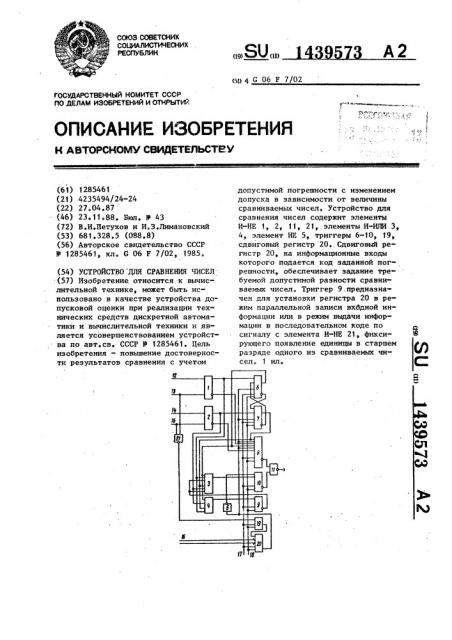

На чертеже изображена структур-ная схема устройства.

Устройство для сравнения чисел содержит элементы И-НЕ 1 и 2, элементы И-ИЛИ 3 и 4, элемент НК 5, 20 триггеры 6-10, элемент И-НЕ 11, входы 12-15 сравниваемых чисел„ вход

16 задания погрешности, тактовый вход 17, вход 18 начальной установки» триггер 19, сдвиговый регистр 20 и 25 элемент И-НЕ 21

Устройство работает следующим образом.

Допустимая разность сравниваемых чисел задается в виде ЗО

2% в где I. - значение первого старшего разряда, равного "1", в любом иэ сравниваемых чисел, n - =L-К; K:=

= О, l,2 — количество "1" в младших разрядах сдвигового регистра 20, определяющих допустимую погрешность;

n — степень числа 2, определяющая. абсолютную достоверность данной пары чисел.

При этом возможны следующие результаты сравнения чисел: после фиксации первого несравнения при А В разность сравниваемых чисел всегда

2L превьппает — — если и любом одном

2к ипи нескольких последующих старших разрядах, включая все К-е разряды, а; отличаются от 0 и Ь; отличается

It iI 5Î от "1", аналогично при А В разность сравниваемых чисел всегда превьшиет

2"

2н если в одном любом или нес кольиих последующих старших разрядах, 5

55 включая все К-е, а; отличается от

"1", а Ь; отличается от "0"; разность сравниваемых чисел не превьппа2" ет — — при А) В нли при А В если

2k после фиксации первого несравнения в результате сравнения оставшихся старших разрядов сравниваемых чисел, включая все К-е разряды, не зафиксировано превышение разностью чисел

2ь значения —,-- а младшие разряды сравниваемых чисел от нулевого до

n-I равньц при А> Б, если после фиксами первого несравнения, при сравнении оставшихся старших разрядов., включая все К-е разряды, не зафиксировано превышение разностью чисел значения

2Ь но зафиксировано первое нес2к У равнение в младших разрядах от и-1 до нулевого, разность сравниваемых

2L чисел превьппает †-„- при условии

2" 2ь

a ° Ь 1 и не лревышаст — при усло

B t

1 вом несравнении в младпп х разрядах с и -1 до нулевого при условии, если а; а Ь;, и не превьппает значение

2" если а Ь

9

Перед началом работы с входа 18 начальной установки устройства на входы установки в "О" с первого по шестой триггеры 6-10, 19 и сдвиговый регистр 20 (с параллельной записью и последовательным выходом) поступает сигнал установки, при этом на прямых и инверсных выходах триггеров

6-10, 19 устанавливаются соответственно нулевые и единичные сигналы.

С входа 16 задания погрешности на информационные входы сдвигового регистра 20 поступает параллельный код, соответствующий заданному допуску. При этом с выхода первого старшего разряда регистра 20 на пятый и шестой входы установки в "1" третьего 8, первого 6 и второго 7 триггеров поступает сигнал единичного уровня и через элемент НЕ 5 нулевым уровнем блокирует вторые входы установки в 1" четвертого 9 и пятого 10 триггеров.

С тактового входа 17 устройства на входы синхронизации триггеров

143

6-10, 19 и регистра 20 поступают тактовые импульсы.

На первые входы первого 1 и вто-. рого 2 элементов И-НЕ с первого 12 и третьего 15 входов сравниваемых чисел устройства соответственно синхронно поступает в двоичной системе счисления в последователвном коде старшими разрядами вперед в прямом и инверсном виде соответственно первое сравниваемое число.

На вторые входы первого 1 и второго 2 элементов И-НЕ и первый и второй вход элемента И-НЕ 21 с второго 13 и четвертого 14 входов сравниваемых чисел устройства в инверсном и прямом виде соответственно поступает синхронно с первым второе сравниваемое число. Инверсные значения первого и .второго чисел с входов

15 и 12 поступают на входы элемента

И-НЕ 21.

При появленич на первом или втором входах элемента И-НЕ 21 значения

"0" на выходе элемента И-НЕ 21 появляется сигнал "1", поступающий на первый вход шестого триггера 19. C выхода шестого 19 триггера поступает сигнал на первый вход регистра 20.

При поступлении сигнала "1" на первый вход регистра 20 начинается сдвиг записанной информации.

На прямых выходах первого 1 и второго 2 элементов И-НЕ определяется первая, ненулевая разность старших разрядов сравниваемых чисел.

Результат первого несравнения разрядов чисел А В формируется в виде сигнала "1" на прямом выходе первого элемента И-НЕ 1 результат -

А< В - на прямом выходе второго элемента И-НЕ 2. Единичный сигнал при

А> В поступает на первый вход установки в "1" первого триггера 6 и на первые входы первого 3 и второго 4 элементов И-ИЛИ. В случае А» В единичный сигнал поступает на первый вход установки в "1" второго 7 триггера и на первые входы вторых элементов И первого 3 и второго 4 элементов И-ИЛИ. В случае А) В по тактовому импульсу, поступающему с тактового входа 17 устройства, на прямом и инверсном выходах первого триггера 6 установится соответственно единичный и нулевой сигналы. При этом нулевым сигналом с инверсного выхода первого триггера 6 блокируется вто"

9573

4 рой вход установки в "1" второго триггера ?. Единичный сигнал с прямого выхода первого триггера 6 посту5 пает на вторые входы соответственно первого и второго элементов И первого 3 и второго 4 элементов И-ИЛИ и третий вход установки в "1" третьего

8 триггера.

Аналогично при А B по тактовому импульсу на прямом и инверсном выходах второго триггера 7 устанавливаются соответственно единичный и нулевой сигналы. При этом первым сигна15 лом с инверсного выхода второго TpHrгера 7 блокируется второй вход устанонки в "1" первого триггера 6. Единичный сигнал с прямого выхода второго триггера 7 поступает на четвер2О тый вход установки в "1" третьего триггера 8 и вторые входы второго и первого элементов И первого 3 и второго 4 элементов И-ИЛИ.

В случае А> В любое отличие каждо25 го последующего младшего разряда числа А от "0", а числа В от "1" дает разность сравниваемых чисел )

7 2, где m — номер разряда числа, начиная с мпадшего. Аналогично при 0 А В любое отличие любого последующего разряда числа А от "1", а числа

В от "0" дает разность сравниваемых чисел ) 2, где m — номер разряда числа, начиная с младшего.

При фиксации А В любое отличие последующих разрядов старше и— числа А от "0", а числа В от "1" приводит к появлению единичного сигнала на инверсном выходе второ40

ro элемента И-НЕ 2, поступаю- щего на второй вход установки в "1" третьего триггера 8. Наличие сигналов единичного уровня с входа 16 .задания погрешности устройства, с прямого выхода первого триггера 6

45 и с инверсного выхода второго элемента И-НЕ 2 переводит в единичное состояние третий триггер 8, сигнал

;с инверсного выхода которого поступает на первый вход элемента И-

НЕ 11, на выходе которого устанавливается единичный сигнал, соответствующий превышению разностью срав- .

2" ниваемых чи значения 2к

Аналогично при А(В .любое отличие числа А от "1", а числа В от "0" приводит к появлению сигнала единичного уровня на инверсном выходе пер5 !4 вого элемента И-HE 1, что в сочетании с сигналами единичного уровня с прямого выхода второго триггера 7 и входа 16 задания погрешности устройства обеспечивает наличие единичных уровней на первом, четвертом и пятом входах установки в "1" третьего триггера 8. При этом на инверсчом выходе третьего триггера 8 устанавливается нулевой уровень, а на вьасоде устройства — единичный, определяющий превышение разности сравниваемых чисел допустимого значения.

На время сравнения младших разрядов сравниваемых чисел c n-1 по нулевой на выходе регистра 20 устанавливается нулевой сигнал, который поступает на пятый и шестой входы установки в "1" третьего триггера 8 и третьи входы установки в "1" первого 6 и второго 7 триггеров и блокирует их. Одновременно нулевой сигнал с выхода регистра 20 поступает на вход элемента НЕ 5„ на выходе которого устанавливается единичнь;й сигнал, который поступает на вторые входы четвертого 9 и пятого 10 триггеров. В случае А » В, если при очередном сравнении младших разрядов сравниваемых чисел, начиная с п-1, а -- Ь;, где i изменяется от п-1 до

О, на прямом выходе перього элемента

И-НЕ 1 устанавливается единичный сигнал, который поступает на вторые входы первых элементов И первого 3 и второго 4 элементов И-ИЛИ и устанавливает единичный сигнал на его выходе. По тактовому импульсу с входа 17 устройства на инверсном выходе пятого триггера 10 устанавливается нулевой сигнал, который поступает на второй вход элемента И-НЕ 11, на выходе которого устанавливается еди. ничный сигнал, соответствующий превышению разностью сравниваемых чи2" сел значения — - .

Если при очередном сравнении младших разрядов а; < b-, единич-. ный сигнал устанавливается на прямом выходе второго элемента И-НЕ 2 и поступает на первые входы вторых элементов И первого 3 и второго 4 элементов И-ИЛИ, а на выходе второго элемента И-ИЛИ 4 устанавливается единичный сигнал, который поступает на первый вход четвертого триггера

9, на инверсном выходе которого по

По тактовому импульсу с входа 17

-5 устройства на инверсном выходе пятого тригг .:ра 10 устанавливается нуле« вой сигнал, который поступает на второй вход элемента. И-НЕ 1". При этом на вьгходе устройства устанавливается сигнал 1", что соответствует превышению разностью сравниваемых чисел

2 значения -р- . Если при очередном сравнении младших разрядов а; 0 Ь ; на прямом выходе первого элемента И-НЕ 1

З" устанавливается единичный сигнал который поступает на первые входы первых элементов И первого 3 и второго 4 элементов И-ИЛИ, на выходе второго элемента И-ИЛИ 4 устанавли40 вается единичный сигнал, который поступает на первый вход четвертого триггера 9. По тактовому импульсу на инверсном выходе четвертого триггера 9 устанавливается нулевой сигнал, который поступает на третьи входы элементов И первого элемента

И-ИЛИ 3 и блокирует дальнейшую рабо ту схемы, что соответствует невозможности превышения разностью сравБО 24 ниваемых чисел значения †-- и соот2к ветственчо появлению сигнала на выходе устройства.

Ф о р м у л а из обретения

Устройство для сравнения чисел по авт.св. Ф 1285461, о т л и ч а39 i 7 ) ii тактовому импульсу с входа 11 устройства устанавливается нулевой сигнал, который поступает на третьи входы элементов И первого элемента

И-ИЛИ 3 и блокирует дальнейшую работу схемы, что соответствует невозможности превышения разностью срав4 ниваемьл; чисел значения —,@- и соот)б

2 ветственно невозможности появления сигнала на выходе устройства. Аналогично в случае Л < В, если при сравнении младших разрядов сравничн - -ел naaHHasr c n-1, a. b;р

1 на прямом выходе второго элемента

И-НЕ устанавливается единичный сигнал, который поступает на. первые входы первых элементов И первого 3

20 и второго 4 элементов И-ИЗИ и устанавливает единичный сигнал на его выходе.

Составитель В.Журавлев

Техред А;Кравчук Корректор M.Ìàêñèèþïèíåö

Редактор С.Пекарь

Тиразк 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Заказ 6077/47

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4, 7 1439573 8 ю щ е е с я тем, что, с целью повы- но соединены с тактовыми входами и шения достоверности результатов срав входаья начальной установки всех кения с учетом допустимой погпешнос- триггеров, управляющий вход сдвигово" ти с изменением допуска в зависимос- го регистра соединен с прямым выхо5 ти от величины сравниваемых чисел, дом шестого триггера, информационный в устройство введены сдвиговый ре- вход которого соединен с выходом четгистр, шестой триггер и четвертый вертого элемента И-НЕ, входы которо; элемент И-НЕ, причем входы задания го соединены с вторым входом первого погрешностей устройства подключены 10 и первым входом второго элементов к информационнык входам сдвигового И-НЕ, выход старшего разряда сдвнгорегистра, входы синхронизации и ус- вого регистра соединен с входом элетановки в "0" которого соответствен- мента НЕ.