Устройство приоритета

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной текнике, в частности к многоканальным устройствам приоритета о Целью изобретения является повышение надежности устройства за счет исключения вьщачи на обслуживание более одного абонента Устройство приоритета содержит три регистра 1, 2, 11, группу триггеров 7, две ры элементов И 5, 6 элементы НЕ 9, И 8, РШИ 3, триггер 4 и элемент 10 задержкио В устройстве исключена возможность одновременной вьщачи разрешения на обслуживание двум абонентам за счет введения блокировки запроса об абонента с более высоким приоритетом , пришедшим после прохождения фронта опрашивающего сигнала 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

È9) (И)

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4247688/24-24 (22) 21.05.87 (46) 23.1.1,88. Бкл. 9 43 (72) А К. Вучнев, В.P. Горовой, О,А. Зимнович и Е.И; Карпунин (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 600557, кл. С 06 F 9/46, 19?6.

Авторское .свидетельство СССР

В 902016, ж. 0 Об F 9/46, 1982, (54) УСТРОЙСТВО ПРИОРИТЕТА (5?) Изобретение относится к цифровой вычислительной технике, в частности к многоканальным устройствам приоритета. Целью изобретения является повьппение надежности устройства за счет исключения выдачи на обслуживание более одного абонента. Устройство приоритета содержит три регистра 1, 2, 11, группу триггеров 7, две групры элементов И 5, 6 элементы НЕ 9, И 8, ИЛИ .3, триггер 4 и элемент 10 задержки. В устройстве исключена возможность одновременной выдачи разрешения на обслуживание двум абонентам за счет введения блокировки запроса об абонента с более высоким приоритетом, пришедшим после прохождения фронта опрашивающего сигнала. 1 ил.

1439587

Изобретение относится к цифровой, вычислительной технике, в частности к многоканальным устройствам приоритета, и может быть использовано в системах дискретной обработки инфор5 мации с применением ЭВИ.

Целью изобретения является повышение надежности устройства за счет исключения выдачи на обслуживание бо- 10 лее одного абонента.

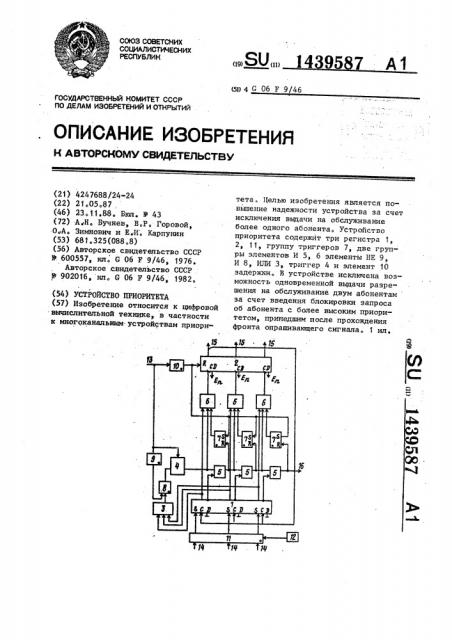

На чертеже представлена блок-схема устройства.

Устройство приоритета содержит регистры 1 и 2, элемент ИЛИ 3, триг,гер 4, группы из N элементов И 5 и б, группу из И триггеров 7, элемент И 8, элемент HF. 9, элемент 10 задержки, регистр 11, генератор 12 импульсов,,установочный вход 13, группу запрос- 20 ных входов 14, группу информационных выходов 15 и выход 16 расширения.

Устройство работает следующим образом.

В исходном состоянии регистры 1, 25 ,2 и 11 и триггер 4 находятся в нулевом состоянии. На группу входов 14 поступают запросы на обслуживание абонентов соответствующего приоритета в виде единичных импульсовр гене " 30

;ратор 12 импульсов осуществляет квитирование запросов во времени приФ ,вязывая запросы к заданной сетке частоты, соответствующие разряды регист, ра 1 устанавливаются в единицу, по,явление любого сигнала запроса в ре«гистре 1 вызывает через элементы ИЛИ 3 и И 8 установку в единицу триггера 4. Единица с выхода триггера ч начинает. распространяться по цепи сквозного, переноса, образованной элементами

И 5, до наиболее приоритетного поступившего запроса, например i-го.

Все элементы И 5 с (i+1)-го по N-й

3GKpblTbI уровнем напряжения с i 1 о 45 инверсного выхода регистра 1. По мере прохождения единицы через элементы

И 5 устанавливаются в нуль соответствующие триггеры 7, тем самым блокируя все предыдущие элементы И 6. Логическая единица, достигнув i-го элемента И б, соответствующего самому приоритетному из поступивших на данный момент запросов, через открытый

i-й элемент И б устанавливает в еди55 ницу i-й разряд регистра 2. В результате на i-м информационном выходе устройства появляется сигнал разрешения на обслуживание i-го абонента, являющегося на данный момент наиболее приоритетным. После окончания обслуживания i-ro запроса на входе 13 появляется (высокий уровень напряжения) ответный сигнал, который устанавливает в исходное состояние цепь сквозного переноса из элементов И 5, а затем через время, определяемое элементом 10 задержки, устанавливает в единицу триггеры 7 и сбрасывает в нуль

i-й разряд регистра 2, с выхода которого формируется сигнал (перепад из единицы в ноль) для записи логического нуля в i-й разряд регистра 1.

Если после обработки i-го запроса на запросных входах 14 другие запросы отсутствуют, то устройство остается в исходном состоянии, если есть еще запросы, то описанный цикл работы устройства повторяется.

Формула из обретения

Устройство приоритета, содержащее первый и второй И-разрядные регистры (N — число абонентов), элемент ИЛИ, триггер, первую и вторую группы из

N элементов И, группа выходов второго регистра соединена с группой инверсных тактовых входов первого регистра и является группой информационных выходов устройства, нулевой вход триггера является входом сброса устройства, каждый i-й (i = 1,М тактовый вход второго регистра соединен с выходом i-го элемента И второй группы, первый вход которого соединен с i-м прямым выходом первого регистра, каждый х-й инверсный выход которого соединен с первым входом

i-ro элемента И первой группы, втоРой вход каждого i-го элемента И пер. вой группы, кроме первого, соединен с вторым входом i-го элемента И второй группы и выходом (i-1)-ro элемента Ии первой группы, второй вход первого элемента И первой группы соединен с выходом триггера, о т л и ч а ю щ ее с я тем, что, с целью повьппения надежности устройства sa счет исключения выдачи на обслуживание более одного абонента, оно содержит группу из

N триггеров, элемент И, элемент НЕ, третий регистр, генератор импульсов и элемент задержки, причем нулевой вход каждого i-го триггера группы соединен с выходом i-ro элемента И первой группы, выход N-ro элемента

143

Составитель В. Красюк

Редактор А. Ворович Техред М.Ходанич Корректор О. Кравцова

Заказ 6078/48 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

И первой группы является выходом распМрения устройства, второй вход первого элемента И второй группы соединен с выходом триггера, выход каждого i-ro триггера группы соединен с третьим входом i-го элемента И второй группы, единичный вход триггера соединен с выходом элемента И, первый вход которого соединен с выходом элемента ИЛИ, а второй вход - с выходом элемента НЕ, вход элемента НЕ соединен с входом сброса устройства и

9587

4 входом элемента задержки, выход которого соединен с нулевым входом второго регистра и единичными входами триг5 геров группы каждый i-й вход элеменФ та ИЛИ соединен с i-м прямым выходом первого регистра, каждый i-й единичный вход первого регистра соединен с i-м выходом третьего регистра, каж10 дый i-й вход которого является х-и запросным входом устройства, вьмод генератора импульсов соединен с тактовым входом третьего регистра.