Устройство управления памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах для организации виртуальной памяти. Цель изобретения - расширеi3 ние функциональных возможностей за счет автоматического выбора номера сегмента. Устройство содержит регистр 1 команд, регистр смещения, регистр 3 номера сегмента, первый дешифратор 4, группу элементов ИЛИ 5, (К+1)-й регистр смещения 6, сумматор 7, рабочий регистр 8, второй дешифратор 9, блок 10 памяти, выходной регистр 11, регистр 12 обмена, группу элементов ИЛИ 13, группу элементов И 14, блок 15 управления, элемент .ИЛИ 16, триггер 17. Цель изобретения достигается за счет хранения номеров сегментов, размещенных в памяти, и их автоматической загрузки в случае отсутствия необходимого сегмента в памяти в текущий момент. 1 з.п.ф-лы, 2 ил. с ел 4:: СО СО О5 о 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 С 06 F 12/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4224405/24-24 (22) 06,0!4.87 (46) 23.1 1. 88. Бвл. У 43 (75) В.П.Морозов. В,Н.Барулин, Я.С.Дымарский, С.Г.Наумов, В.А.Назаров, Ю.Б.Рычагов, А.Н.Терехов и Н.Ф.Фоминь!х (53) 681,32 (088.8) (56) Заявка Японии М 54-16381, кл. С 06 F 11/00, 1979.

Патент США У 4187538, кл. С 06 F 13/00, 1980. (54) УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах для органиэации виртуальной памяти. Цель изобретения — расаиреÄÄSUÄÄ14 9 03 А1 ние функциональных возможностей эа счет автоматического выбора номера сегмента. Устройство содержит регистр

1 команд, регистр 2>-2 смещения, регистр 3 номера сегмента, первый дешифратор 4, группу элементов ИЛИ 5, (N+1)-й регистр смещения 6, сумматор

7, рабочий регистр 8, второй дешифратор 9, блок 10 памяти, выходной регистр 11, регистр 12 обмена, группу элементов ИЛИ 13, группу элементов

И 14, блок 15 управления, элемент .ИЛИ 16, триггер 17. Цель изобретения достигается за счет хранения номеров сегментов, размещенных в памяти, и их автоматической загрузки в случае отсутствия необходимого сегмента в памяти в текущий мамеит. 1 е.я.ф-вщ, g

2 ил.

1 »»(l A (,(I

Из о б р е т е н ие относится к цифровой выч и слительн о и т ех и гн е и может быть использовано при построении ц»»(:-::ровь»х вычислитегп ных систем и автоматизи5 рованных систем управ.т»ен»тя.

Цель изобретения - расп(»»реппе функциональпьх возможно;..-ей HH счет автОматическоГО выбора»(омероь с" Г ментов. i *é.

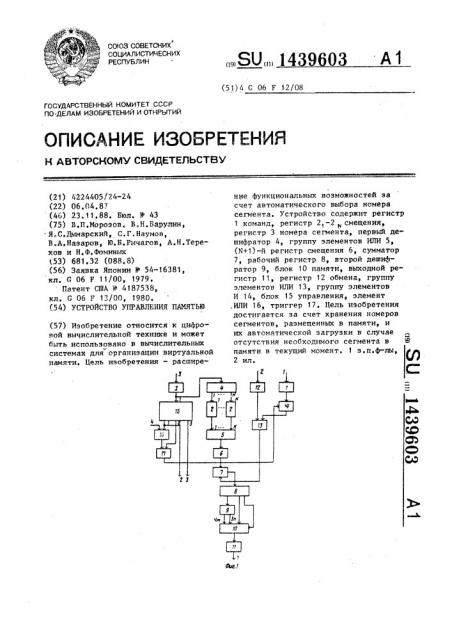

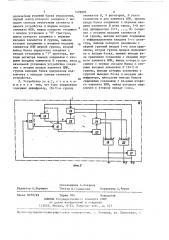

Па фиг.1 представлена структурная схема ycTpoiicTBH1 на фиг.2 - приведена структура блока управления.

Устройство (фиг.1) содерж.г регистр 1 команд, регистры ?»-2,, смещения с первого по N-й (N — максимальное число сегментов, размещенных в памяти), регистр 3 номера сегмента, первый дешифратор (», группа элементов

NOH 5 (N+ 1 )-й, регистр 6 смещения, сумлатор " рабочий регистр 8,. зторой дешифратор 9, блок 10 памяти, выходной регистр 11, регистр 12 Обмена, группы элементов ИЛИ 13 и И 1(». блок 15 управпения, элемент

HJK 16 триггер 17. Г>лок уп-равления (фиг.2) содержит группы элементов И с первой по И-ю 18,-18„,, первый и второй элемепть1 ИЛИ 19 и 20., (N+1)-ю группу элементов И 21 деЛ шифратор 22, группу регистров 231—

23НУ групу Ы уэлв 2/»1-24 и ср е-ния.

Устройство управления память:и работает следующим образом.

Перед началом работы устройства

На eI O ЧЕтВЕРтий (Уста»»ОВОтн»ЬП») ВХОД подается управляющий сигнал„ устанавливающий триггер 17 в состояние "0".

При этом запрещается продолжение сигналов через элемент И 14.

Прн ОбращЕНП»»; yCTpOт»СТВу Ч(Ер»ЗS его третий вход на вход регистра 3 номера сегмента поступает m-разряд-ный код номера сегмента, Через первый

»» 5 вход устройства на вход регистра поступает и-разрядный код обращения к блоку 10. При этом и-разрядный код обращения copepI .»IT и, -разрядный код операции (записи или чтеннн). Нт -тзазрядный код адрес". (в первом сегменте 50 блока 1 0) и п "разряд»»»ьп»»тпформаЦис и: ный код (для Операции эапт»сн) приче;т

n=n +п. »-и „.

С выхода реГистра 1 и pH3p»Iдньти, код поступает на входы элементов И 1 ..з5

С выходов регистра 3 номера сег-мента ьп-разрядный код пост;паeò на входы блока 15 управления,.:<ототтт,тй

ПРЕДНЯЗНЯ»»ЕН ДЛЯ УПРНБЛЕ»(НЯ ПРС)ЦЕ. »..H

MII Ит(форм ацно ННОГО О б .»ЕН т т(о,т(д » В НЕШней памятью»и блоком 10, Б".ок 10 управления анализирует тп-ра»зряд((ь(й(код сегмента„а затем либо разрешает

Гоохожцение и-разрнднОГО Ода обращения через элементы И 11 к блоку 10 (если ТрР 61/ емый сех 6!e!I 1 наход»(Гc!I B блоке памяти), либо организует запись

-:ðåáóå6»îão сегмента из,=I»eшней памяти в блок 10 (если требуемьп» сегмент отсутствует в нем) „а ".ÿòåê разрешает прохождение и- ;азрядного кода обращения (c помощь . триг1 QpH 1 7) через элементы И . (блоку 10. Кс.т»и требуемьп» сегме:(т .тт»"утствует в блоке 10 то yiipа13ляющий» си I»BI," с петрво гo выхода блока 15 управ:»-.Ния поступае г I!а второй выход устр"иствау а триггер !7 при эroI устанавливается в состояние "0", з т»т»е»т,ая прохождение сигналов неге.":: зпемет .-и 1I 1".. Номер сегмента (-и-ра. †;ядный код,т при этом с третьего,-шкода-:: блска 1.= yr;1»авленпн поступHpт =Id третий вьжод устрой ства. Если требуе;-ььп»- сегь»ент имееттсн в блоке 10 то управляющий (игн»»(» втОроГО в61хода блока 15 jï.— равления устанавливаеr триггер 17 в состояние ",", раH(peï!Hè прохождение сигналов чере - элементы И 1 4.

И:1(т:,Оркапт»тОННЬП» ОбМЕН МЕжд; ЗНЕЕ;-Ей памятью и блоком 10 (запись в блок 1С,» осуществляется г.-разрядньми кодами через регистр 12 обмена:, ВЫХОДа РЕГИСТРа 3 (»От ЕРа»" Еr! fe!» i H Ш--.таэрядНЬ»й КОд ПОСТупаст а ВХ-."т первого дешифратора»».,т(еш((фрато

Hнализирует код номера-:с гмснтя и в соответстви»» с тт»=:,т вырабатыв ет т»ПРПВЛ(»тО1 Цтй Ст»- »(аЛ Н ", COO (ПЕТСТВУт(тЩЕМ выходе, Зтот управляющии сиГнал с со

Ответствующего вьг,.ода дешифратора»» поступает на вход выбора соотв тствующего регистра 2 смещения, с выхода

КотОРОГО S-РаЗРЯДНЫй КО;т, СКЕЩЕНИЯ еоез элемечт ИЛИ 5 I»oступает на IIepвый вход сумматора 7.

». ут((»»ато p» c (::-п»итруe .(копы ЦО с. Гу т.т тт»т»ие на e-o первый и (: торой входы, В та Ет (» ВЫКОЦ »»OCT (IIH(:т тт .-т.аЗРЯДПЬП-" код обращения к блоку 10. Причем т1 -раэрядн»й код озра»(1(»н»»н при ="Tob» содержит и -разрядный код оп»зпации

1 „:-РаЗРЯД»»Ь»й КОЦ адРЕСа (C Ут..;:ТОМ

Ш Ния) И Г, " "РаЗРЯДНьтй (ПнфОРМаЦИОННЫй

КОД (ДЛЯ ОПЕРаЦИИ Запитзтт,т - ПР.": (ЕМ

» э 14 п, -Разрядный код операции посту-, пает на вход, второго цешифратора 9, который на основе анализа поступившего кода вырабатывает управляющий сигнал на первом или втором выходе (сигналы чтения или записи). С второго выхода рабочего регистра 8 S-разрядньгй код адреса поступает на адресный вход блока 10. С третьего выхода рабочего регистра 8 и -разрядный информационный код (в случае требования на запись) поступает на информационный вход блока 10, В случае требования на запись п -разрядный инфор3 мационный код записывается в блок 10 (в соответствующий сегмент и соответствующий адрес) . Б случае обращения на чтение и -разрядный информационный

Э код с выхода блока 10 через выходной регистр 11 поступает íà информационный выход устройства.

Блок 1 . Управления работает следующим образом.

Через вход блока 15 управления

m-разрядный код номера сегмента (по требованию) поступает на информационные входы элементов 18 и 2 1 и на вторые входы узлов 24 сравнения. Узлы

24 сравнивают поступивший m-разрядный код с ш-разрядными кодами, записанными в регистрах 23 номерами сегментов, которые в настоящий момент записаны в блоке 10. Если поступивппп!. ш-разрядный код треоуемого сегмента совпал с одним из m-palp;дных кодов которые записаны в регистрах 23, то со второго выхода соответствующего узла 24 управляющий сигнал поступает через элемент ИЛИ на второй выход блока

15 управления, Если поступивший m ðàçрядный код требуемого сегмента не совпал ни с одним из m-разрядных кодов, которые записаны в регистрах 23, то с первых выходов всех узлов 24 управляющие сигнан:. поступают на входы элементов ИЛИ 19, что приводит к тому что на вьгходе элемент" 19 появляется управляющий сигнал, коtорый разрешает прохождение m-разрядного кода номера сегмента через группы элементоь. И 21, Кроме того, этот управляющий сигнал поступает на первый выход блок". 15 управлення.

С выходов элементов И 2 1 ш-разрядный Код требуемого номере сегмента и.-:ступае г ня вьгходл блока 1 управления и ня входы дешнфраторя ?2. Дешифратор 22 я>.ялнзирует поступивший

39603

m-pa=рядныи код и разрешает запись

m-разрядного кода требуемого номера сегмента через соответствующую группу элементов И 18 в соответствующий регистр 23. формула изобретения

1. Устройство управления памятью, содержащее регистр команд, (И+1) регистров смещения, где N — - максимальное число сегментов, размещенных в памяти, регистр номера сегмента, два дешифратора, две группы элементов

HJ_#_, сумматор, рабочий регистр, блок памяти, выходной регистр обмена, при. чем входы ког1я команды устройства лодключены к информационным вхоцам регистра команд, информационные входы устройства соединены с информационными входами регистра обмена, выходы которого соединены с первыми входами элементов ИЛИ первой группы, 2я выходы которых соединены с входами первого слагаемог сумматора, выходы которого соединены с информационными входами рабочего регистра, выходы адреса и данных которого соединены с входами адреса и данных соответственно блока памяти, выход которого соединен с информационным входом выходного регистра., выход которого соединен с выходом устройства, входы номера сегмента устройства соединены с информационными входами регистра номера с сегмента, выходы которого соединены с входами первого дешифратора, i-й выход которого (i=1 ..., N) соеди нен с входом выбора i-ro регистра

40 смещения, выходы которого соединены с i-ми входами элементов ИЛИ второй группы, выходы которых соединены с информационными входами (N+1)-го регистра смещения, выходы которого подключены к входам второго слагаемого сумматора, выходы кода операции рабочего регистра соединены с входами второго дешифратора, первый, второй выходы которого соединены соответственно с входом чтения и записи блока памяти, о т л и ч а ю щ е— е с я тем, что, с целью расширения функциональных возможностей за счет автоматического выбора номеров сегментов, оно содержит группу элементов И, элемент IIJIH, триггер и блок управления, причем вь.ход регистра номера сегмента соединен с входом

5 1439б логиче ских условий блока управления, первый выход которого соединен с выходом сигнала отсутствия сегмента в памяти устройства и первым входом элемента ИЛИ. выход которого соединен

5 с входом установки в "0" триггера, выход которого соединен с первыми входами элементов И группы, выходы которых соединены с вторыми входами элементов ИЛИ первой группы, второй выход блока управления соединен с входом установки в "1" триггера, выходы регистра команд соединены с вторыми входами элементов И группы, вход 1 начальной установки устройства соединен с вторым входом элемента ИЛИ, группа выходов блока прерывания под, ключена к выходам номера сегмента устройства.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок управления содержит дешифратор, (К+1) -ю группу

Составитель А. Чеканов

Техтед Л.Сердюкова

Редактор A.Âoðîâè÷

Корректор С.Черни

Заказ 6079/49

Тираж 70ч Подписное

В!!ИИПИ Государственноге комитета ССС! по делам изобретений и открытий

113035, Москва, Ж-35, Раушекан наб., д. 4/5!!роизв дственно-полиграфи . екое иредпринтие, г, Ужгород, ул. Проектная, 4 ! ! !! !! !

03 6 элементов И, N регистров, N узлов сравнения и два элемента ИЛИ, причем входы блока соединены с первыми входами элементов И всех. групп, i-й выход дешифратора (=1, ..., N) соединен с вторыми входами элементов И

i-й группы, выходы которых соединены с информационными входами i-го регистра, выходы которого соединены с первой группой входов i-го узла сравнения, вторая группа входов подключена к входам блока, прямые выходы узла сравнения соединены с входами первого элемента ИЛИ, выход которого соединен с первым выходом блока и вторыми входами элементов И (И+1)-й группы, выходы которых соединены с группой выходов блока и входами дешифратора, инверсные выходы блоков сравнения соединены с входами второ" го элемента ИЛИ, выход которого подключен к второму выходу блока,