Устройство для формирования кодовых последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах автоматической обработки данных. Изобретение позволяет устранить влияние ограниченной продолжительности такта работы устройства . на частоту формирования элементов кодовых последовательностей, что повышает общее быстродействие устройства. Устройство для формирования кодовых последовательностей содержит генератор 1 импульсов, элемент 2 И,делитель 3 частоты, элемент 4 задержки, три счетчика 5,10 и I3 импульсов, элемент 6 сравнения, два триггера 7 и 9, два формирователя 8 и 15 коротких импульсов, три элемента памяти II, 14 и 21, демультиплексор 12, элемент 16 ИЛИ, регистр I7, два блока 18 и 19 триггеров (18.1,...,18.П и 19.,.«., 9.п), блок 20 регистров (20.1,..., 20.п). 1 ил. S СО

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н д ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4092800/24-24 (22) 16.07.86 (46) 23.11.88.Бил.9 43 (71) Одесский политехнический институт (72) И.Н.Николенко, А.В.Дрозд, P.Ã.Äæàãóïîâ, А.В.Дрозд и Е.Л.Полин (53) 681.325(088.8) (56) Авторское свидетельство СССР

N- 369705, кл. Н 03 M 7/00, 1971.

Авторское свидетельство СССР

Р 1231584, кл. Н 03 M 7/00, 1986. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

КОДОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к вычислительной технике и может быть использовано в системах автоматической об работки данных. Изобретение позволяет

Л0„„439744 А1 устранить влияние ограниченной продолжительности такта работы устройства .на частоту формирования элементов ко» довых последовательностей, что повышает общее быстродействие устройства.

Устройство для формирования кодовых последовательностей содержит генератор 1 импульсов, элемент 2 И,делитель

3 частоты, элемент 4 задержки, три счетчика 5,10 и 13 импульсов, эле мент 6 сравнения, два триггера 7 и 9, два формирователя 8 и 15 коротких импульсов, три элемента памяти ll

14 и 21, демультиплексор 12, элемент

16 ИЛИ, регистр 17, два блока 18 и 19 триггеров (18.1,...,18.п и 19.1,..., <О

19.n), блок 20 регистров (20.1,..., 20.n). 1 ил.

1439744

Изобретение относится к вычислительной технике и может быть исполь" зовано в системах автоматической обработки данных.

Цель изобретения — повышение быстродействия устройства.

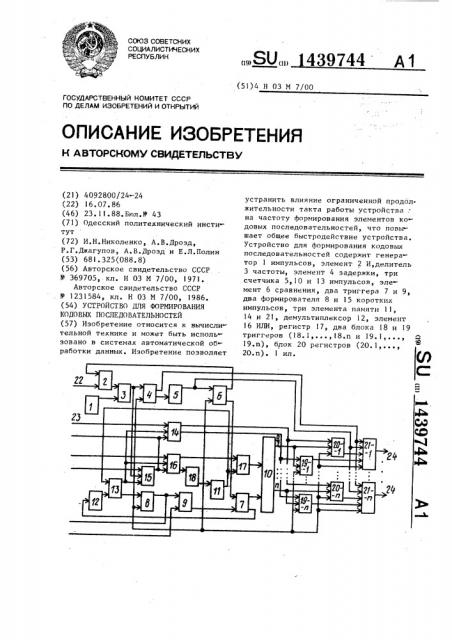

На чертеже приведена функциональная схема устройства.

Устройство содержит генератор 1 импульсов, элемент И 2, делитель 3 частоты, элемент 4 задержки, первый счетчик 5 импульсов, элемент 6 сравнения, первый триггер 7, первый формирователь 8 коротких импульсов, I5 второй триггер 9, второй счетчик 10 импульсов, первый элемент 11 памяти, демультиплексор 12, третий счетчик 13 импульсов, второй элемент 14 памяти, второй формирователь 15 коротких 20 импульсов, элемент ИЛИ 16, регистр

17, первый 18 и второй 19 блоки триг геров (18-1...,,18-n) и (19-1,..., 19-n), блок 20 регистров (?О-1,..., 20-n) и третий элемент 21 памяти. 25

Кроме того, обозначены входы запуска

22 и начальной установки 23 устройства и выходы 24 устройства.

Устройство работает следующим образом. 30

Перед пуском устройства сигналом

Начальная установка1, поступаюшим на вход 23 начальной установки устройства, сбрасывается в ноль счетчик

10 адреса,TV-триггеры 18-1,...,18-п первого 18 и 19 1,...,19-п второго 19 блоков триггеров, регистры 20-1, ...20-n блока 20 регистров, устанавливается в единичное состояние делитель 3 частоты, счетчик 5 и счетчик 13 адреса, а через элемент ИЛИ 16 сбрасываются в ноль также регистр 17 и RS-триггер 9.

Импульс запуска, поступающий на вход установки D-триггера 7, устанавливает его в единичное состояние, раз- 5 решая прохождение импульсов с выхода генератора 1 через элемент И 2 на счетный вход счетчика 13 адреса и вход делителя 3 частоты. С первого и второго выходов делителя 3 частоты снимаются синхросигналы типа меандр, отмеряющие собственно такты и полу такты работы устройства. Синхросигналы с первого зыхода делителя 3 час- тоты поступают на вход элемента 4 за55 держки, с выхода которого подаются на счетный Иход счетчика 5. Первый импульс с выхода элемента 4 задержки переводит счетчик 5 в следующее, нулевое состояние. Код с выходов счетчика

5 поступает на первый вход элемента

6 сравчения.

Нулевой код выхода счетчика !0 адреса поступает ня адресный вход первого элемента 11 памяти, хранящег0 номера тактов, в которых происходит изменение хотя бы одного из выхо-, дов ?4 устройства.

По нулевому адресу элемент 11 памяти считывает первый код номера такта, Этот код поступает на второй вход элемента 6 сравнения, который уменьшает "-нячение кода на единицу младшего разряда и сравнивает полученный результат с кодом счетчика 5.

При совпядении сравниваемых кодов потенциал логического 0" с инверсного выхода элемента 6 сравнения поступает на вход управления демультиплексора

l2 а единичный сигнал с прямого выхода элемента 6 сравнения поступает на первый формирователь 8 коротких импульсов. При этом формируется короткий единичный импульс, устанавливаюший по S-входу RS-триггер 9 в единичное состояние. Единичный сигнал с прямого выхода RS-триггера 9 пода " ется на входы выборки второго 14 и третьего 21 элементов памяти, а также на вход разрешения счета счетчика

13 адреса, который под действием синхросигнялов, поступаюших íà его счетный вход, начинает изменять свое состояние, формируя на адресных вхо дах второго 14 и третьего 21 элементов памяти последовательность значений адреса.

Во втором элементе 14 памяти хранится последовательность групп кодов, Каждая группа кодов взаимооднозначно соответствует одному коду (номеру такта) из элемента 11 памяти и содержит коды номеров каналов(номеров выходов 24 устройства), которые изменяют свое состояние в соответствующем так» те работы устройства. В группе коды перечисляются в произвольном порядке.

Код номера канала содержит дополни тельный разряд, принимающий в последнем коде каждой группы единичное зна» чение и нулевое значение в других кодах. Этот признак окончания группы кодов считывается с управляющего выхода второго элемента 14 памяти.

В третьем элементе 21 памяти хранятся двухразрядные коды переключений, взаимооднозначно соответствующие з 14397 кодам групп второго элемента 14 памяти. Первые (вторые) разряды кодов переключений указывают единичным значением на изменение выхода устрой5 ства на первом (втором) полутакте такта по отношению к соответствующему полутакту предшествующего такта.

Считываемые с второго элемента !4 памяти коды номеров каналов группы поступают на информационные входы регистра 17, а с его выходов на адресные входы демультиплексора 12, обеспечивая последовательное формирование единичных импульсов на его выходах, соответствующих номерам каналов группы.

С первого и второго выходов третьего элемента 21 памяти снимаются соответственно первый и второй раз- 20 ряды кода переключений, поступающие на V-входы TV-триггеров !8-1,..., 18-и первого блока 18 и ТЧ-триггеров

l9-1,...,19-п второго блока 19 соответственно (единичное значение на 25

U-входе TV-триггера разрешает изменять его состояние на инверсное с приходом единичного импульса (фронта) на Т-вход TV-триггера). На Т-входы

i-x TV-триггеров 18-, 19-i первого 30

18 и второго 19 блоков (i = 1, n) поступают единичные импульсы либо ну» левой уровень с i-x выходов демультиплексора 12. Единичные импульсы ин вертируют TV-триггеры, выбранные по

V-входу. Сигналы с выходов TV-триг» геров первого 18 и второго 19 блоков поступают на первый и второй входы соответствующих регистров 20-1,...

20-и блока 20. На синхровходы регист- 40 ров 20-1,...,20-п поступает синхросигнал с второго выхода делителя 3 частоты, а на управляющие входы поступает сигнал с выхода элемента 4 задержки, обеспечивая при нулевом зна-45 чении прием информации, а при единичном значении ее сдвиг на один разряд.

В результате приема информации на выходе регистра 20-i блока 20 появляется значение сигнала, принятого с вы-яО хода TV-.òðèããåðà 19-i первого блока 1

l9, а в результате сдвига - значение .сигнала, записанного в регистр 20-i с выхода TU-.òðèããåðà 19-i второго блока 19.

Одновременпо со считыванием последнего кода группы на управляющем выходе второго элемента 14 гамяти считывается единичный сигнал признака

Формула изобретения

Устройство для формирования кодовых последовательностей, содержащее генератор импульсов, выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом делителя частоты, пер вый выход которого через элемент задержки соединен со счетным входом первого счетчика импульсов, первый и второй выходы первого счетчика импульсов соединены соответственно с первым входом элемента сравнения и входом установки первого триггера, выход которого соединен с вторым входом элемента И, первый формирователь коротких импульсов, выход которого соединен с S-входом второго триггера, инверсный выход которого соединен со счетным входом второго счетчика импульсов, выход которого соединен с адресным входом первого элемента памяти, выход которого соединен с вторым входом элемента сравнения, выход которого соединен с входом управления демультиплексора, третий счетчик импульсов, выход кото. рого соединен с адресным входом второго элемента памяти, первый выход которого соединен с входом второго окончания группы. Этот сигнал поступает на вход второго. формирователя

)5 коротких импульсов, с выхода которого сформированный короткий импульс с задержкой на величину tp поступает через элемент ИЛИ !6 на вход сброса регистра 17 и на К-вход RS-триггера

9. При этом происходит обнуление регистра 17 и RS-триггера 9. Сигнал с прямого выхода RS-триггера 9 останавливает изменение состояний счетчика

13 адреса и переводит по входам выборки второй 14 и третий 21 элементы памяти в нулевое состояние. Сигнал с инверсного выхода RS-триггера 9 переводит в следующее состояние счетчик 10 адреса. При этом из первого элемента ll памяти считывается следующий код номера такта.

Импульсы с выхода элемента 4 задержки обеспечивают отсчет счетчиком

5 тактов реального времени и при установке старшего разряда счетчика

5 в единичное значение D-триггер 7 переходит в исходное нулевое состояние, завершая работу устройства.

l4 3974

Составитель Б.Ходов.

Техред М.Моргентал

Редактор М.Бланар

Корректор Э.Лончакова

Заказ 6089/56

Тираж 929

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r, Укгород, ул, Проектная, 4

5 формирователя коротких импульсов, выход которого соединен с первым входом элемента ИЛИ, второй выход второго элемента памяти и выход элемента ИЛИ соединены соответственно

5 с информационным входом и входом сброса регистра, выход которого соединен с адресным входом демультиплексора, выходы которого соединены с 1О T-входом одноименных триггеров первого блока триггеров, и второй блок триггеров, вход синхронизации первого триггера является входом запуска устройства, входы установки триггеров 16 ,первого и второго блоков триггеров объединены с вторым входом элемента

ИЛИ, с входами установки первого, второго и третьего счетчиков импульсов и делителя частоты и являются входом начальной установки устройства о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены блок регист-: ров и третий элемент памяти, первый 25 и второй выходы которого соединены с Ч-входами триггеров соответственно первого и второго блоков триггеров, 1

4 6 прямой выход второго триггера соединен с входами выборки второго и третьего элементов памяти и входом разрешения счета третьего счетчика импульсов, счетный вход которого подключен к выходу элемента И, Rвход второго. триггера подключен к выходу элемента ИЛИ, прямой выход элемента сравнения соединен с входом первого формирователя коротких импульсов, адресный вход третьего элемента памяти подключен к выходу третьего счетчика импульсов, выходы триггеров первого и второго блоков триггеров соединены соответственно с первыми и вторыми информационными входами одноименных регистров блока регист ров, второй выход делителя частоты соединен с входами синхронизации регистров блока регистров, управляю» щие входы которых подключены к выходу элемента задержки, входы уста» новки регистров блока регистров подключены к входу начальной установки устройства, выходы блока регистров являются выходами устройства.