Одноразрядный сумматор на моп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть исполь/4 i5 зовано в процессорах ЭВМ. Цель изобретения - упрощение одноразрядного сумматора на МОП-транзисторах. Одноразрядный сумматор на МОП-транзисторах .содержит нагрузочные 1-3 и функциональные 4-11 МОП-транзисторы, выходы 12, 13 суммы 5; и переноса С- сумматора, входы 14, 15, 16 первого X j и второго у; слагаемых и переноса С ,, сумматора . Транзисторы 1,4,5. образуют элемент РАВНОЗНАЧНОСТЬ 17, транзисторы 2,8,7 образуют элемент РАВНОЗНАЧНОСТЬ 18. На выходе 12 суммы сумматора образуется функция S; Xj ©У; ©С;,. На выходе 13 переноса сумматора реализуется логичес-3 кая функция С| (х;(Эу; ) S; f(x; ЙУ)х,-. (Л 00 оо

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) 7 А1 (5))4С 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H Д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4163580/24-24 (22) 18. 12.86 (46) 30.11.88. Бюл. )(- 44 (71) Ленинградский электротехнический институт нм. В.И.Ульянова (Ленина) (72) В.И.Варшавский, Н.А.Голдин, А.Ю.Кондратьев и Б.С.Цирлин (53) 68 1.325.5(088.8) (56) Авторское свидетельство СССР

В 1325465, кл . G 06 F 7/50,03.03.86.

Авторское свидетельство СССР

9 1357945, кл. G 06 F 7/50,07.04.86. (54) ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОПТРАНЗИСТОРАХ (57) Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения — упрощение одноразрядного сумматора на МОП-транзисторах. Одноразрядный сумматор на МОП-транзисторах .содержит нагрузочные 1-3 и функциональные 4-11 МОП-транзисторы, выходы 12, 13; и переноса С; сумматора, входы 14, 15, 16 первого х и второго у; слагаемых и переноса С;, сумматора. Транзисторы 1,4,5 образуют элемент РАВНОЗНАЧНОСТЬ 17, транзисторы 2,8,7 образуют элемент

РАВНОЗНАЧНОСТЬ 18. На выходе 12 суммы сумматора образуется функция S;

= х; Q+ у; (+) С;,. На выходе 13 переноса сумматора реализуется логическая функция С; = (х; Яу; ) $; (х Юу; ) хх(.

1441387

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения — упрощение одноразрядного сумматора на МОП-транзис5 торах.

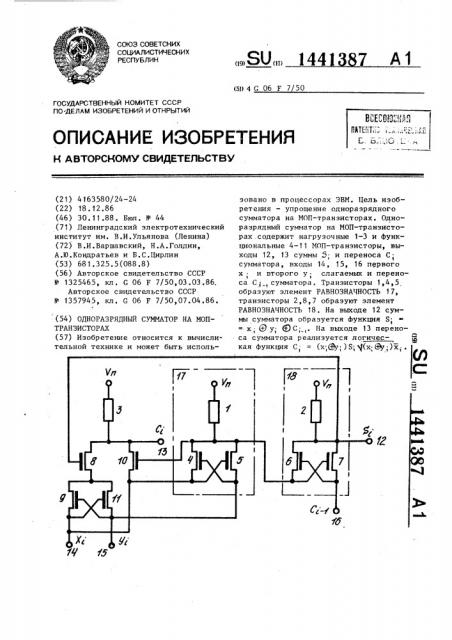

На чертеже представлена схема одноразрядного сумматора на МОП-транзисторах. 1а

Одноразрядный сумматор на МОПтранзисторах содержит нагрузочные

1-3 и функциональные 4-11 МОП-транзисторы, выходы 12 и 13 суммы (S;) и переноса (С;) соответственно и входы 14, 15 и 16 первого (х;) и вто рого (у. ) слагаемых и переноса (С;, ) соответственно. Транзисторы

4,5 и 1 и 6,7 и 2 образуют соответственно первый 17 и второй 18 эле- 2р менты РАВНОЗНАЧНОСТЬ.

Сумматор работает следующим образом.

Значения слагаемых с входов х, и у; поступают на входы первого элемен- 25 та 17 РАВНОЗНАЧНОСТЬ, значение с выхода которого поступает на первый вход второго элемента 18 РАВНОЗНАЧНОСТЬ, на второй вход которого поступает значение переноса с входа С;, . 3Р

;Таким-образом, на выходе второго

I элемента 18 РАВНОЗНАЧНОСТЬ, т.е. на на выходе S, суммы, реализуется функ, ция

S; = x;O+y; O+C;, °

При нулевом значении на входах обоих слагаемых (х, = у; = 0) на затворе транзистора 10 имеется единичное значение с выхода первого элемента 4р

17 РАВНОЗНАЧНОСТЬ, открывающее этот транзистор, а на выходе переноса— нулевое значение (С = 0).

Если на входе одного из слагаемых имеется единичное значение, а на 45 входе другого слагаемого — нулевое значение (х; = 1, у, = Оилих; = О, у; = 1), то на выходе первого элемента 17 РАВНОЗНАЧНОСТЬ имеется нулевое значение, которое, поступая на затвор тразистора 10, закрывает последний. Если при этом на выходе суммы имеется нулевое значение (S; = О), что, очевидно„возможно только при единичном значении на входе переноса (С;. = 1), то закрыт и транзистор 8, затвор которого соединен с выходом суммы, и на выходе переноса будет единичное значение (С;. = 1), Если же! на выходе суммы имеется единичное значение (S, = 1), что, очевидно, возможно только при нулевом значении на входе переноса (С1, — — О), то транзистор 8 открыт, а поскольку при этом открыт и один из транзисторов 9 нли

11, на затворе которого имеется единичное значение с входа одного из слагаемых, а стоке — нулевое значение с входа другого слагаемого, на выходе переноса будет нулевое значеНе (С„= О).

При единичном значении на входах обоих слагаемых (х, = у,,= 1) на стоках транзисторов 9,10 и 11 имеются единичные значения и такое же значение будет на выходе переноса (C; = 1) .

На выходе переноса реализуется логическая функция

С, = (х; Зу,)S; Y (х; (++y;)x;

Транзисторы 9 и 11 подключены к входам х и у ° первого и второго сла1 гаемых так же, как и транзисторы 4 и 5, образующие первый элемент 17

РАВНОЗНАЧНОСТЬ. Однако непосредственное подключение выхода первого эле" мента 17 РАВНОЗНАЧНОСТЬ к стоку транзистора 8 вместо транзисторов 9 и 11 недопустимо. При нулевых значениях на входах обоих слагаемых (х; = у, = 0) на выходе первого элемента 17

РАВНОЗНАЧНОСТЬ должно быть единичное значение, а на выходе переноса — нулевое значение (С„ = 0), но при единичном значении на выходе суммы (S; — 1) это нулевое значение с выхода

1 переноса через открытый транзистор

8 поступило бы на выход первого элемента 17 РАВНОЗНАЧНОСТЬ, что привело бы к искажению значения как на выходе первого элемента 17 РАВНОЗНАЧНОСТЬ, так и на выходе суммы и переноса.

Формула изобретения

Одноразрядный Сумматор на МОПтранзисторах, содержащий два элемента РАВНОЗНАЧНОСТЬ, четыре функциональных транзистора и один нагруэочный транзистор, причем входы первого и второго слагаемых сумматора соединены соответственно с первым и вторым входами первого элемента РАВНОЗНАЧНОСТЬ, выход которого и вход переноса сумматора соединены соответст1441387

Составитель А.Клюев

Редактор Е.Копча Техред М.Дидык Корректор Л.Пилипенко

Заказ 6289/52 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж- 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4. венно с первым и вторым входами второго элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с выходом суммы сумматора и затвором первого функционального транзистора, сток которого соединен с истоком второго функционального транзистора, а исток — с выходом переноса сумматора и истоком третьего функционального транзистора затвор и исток которого соединены соответственно с выходом первого элемента РАВНОЗНАЧНОСТЬ и входом перного слагаемого сумматора, а истоксо стоком нагрузочного транзистора, исток которого соединен с шиной пи5 тания сумматора о т л и ч а ю щ и йФ с я тем, что, с целью упрощения, истоки второго и четвертого функциональных транзисторов соединены между собой, а их затворы — .со стоками чет"

1р вертого и второго функциональных транзисторов и входами соответственно первого и второго слагаемых сумматора.