Устройство для поиска информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и-вычислительной технике и может быть использовано в системах обработки информации. Цель изобретения - повышение быстродействия устройства при поиске в нез порядоченном массиве и расширение функциональных возможностей за счет обновления информации в обрабатываемых MacciiBax в зависимости от результата поиска. С этой целью в устройство, содержащее блок 6 управления, блок 2 памяти и схему 8 сравнения, введены блоки 3-4 памяти, блок 1 обработки рубежа и коммутатор 9с соответствующими-связями. 4 з.п. ф-лы, 4 ил. г

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 G 06 F 15/40 огг;,r t °, 3" .::,.„-,:, 4Е->U "À»,, ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОбРЕТЕНИЙ И ОТНРЫТИЙ (21) 4084810/24-24 (22) 09.07.86 (46) 30.11.88. Бюл. - 44 (71) Рижский Краснознаменный институт инженеров гражданской авиации им.Ленинского комсомола (72) О.Р,Фролов и В.З.Самойленко (53) 681.325 (088.8) (56) Авторское свидетельство СССР

1Ф 1228116. кл. G 06 Р 15/40, 1984

Авторское свидетельство СССР 1 1278891> кл.С 06 F 15/40, 1985. (54) УСТРОЙСТВО ДЛЯ ПОИСКА ИНФОРМАЦИИ (57) Изобретение относится к ома

„„SU„„1441420 А 1 тике и вычислительной технике и может быть использовано в системах обработки информации. Цель изобретения — повышение быстродействия устройства при поиске в неупорядоченном массиве и расширение функциональных возможностей за счет обновления информации в обрабатываемых массивах в зависимости от результата поиска. С этой целью в устройство, содержащее блок

6 управления, блок 2 памяти и схему

8 сравнения, введены блоки 3-4 памяти, блок 1 обработки рубежа и коммутатор

9 с соответствующими связями. 4 s.n.

1441420

Изобретение относится к автоматике и !!ыч!!слительной технике и может быть использовано в системах обработки информации.

Пель изобретения — повышение быстродействия устройства при поиске в неут-Орядоченном массиве и расширение функциональных возможностей за счет обновления информации в обрабатываемых массивах в зависимости от результата поиска.

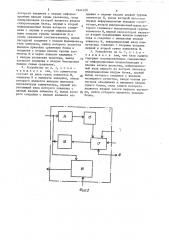

На фиг. 1 изображена схема устройства; на фиг. 2 — схема блока обработки рубежа; на фиг. 3 — схема блока управления; на фиг 4 — схема блока коммутаторов.

Устройство содержит блок 1 обработки рубежа, блоки 2-5 памяти„ блок

6 управления, регистр 7., схему 8 срав-2д нения и коммутатор 9, содержащий элемент 10 задержки, элемент И 11, группы 12 и 13 элементов И. Блок 1 обработки рубежа содержит элемент 14 задержки, триггер 15, формирователь 16 импульса, схему 17 сравнения, группу

18 элементов И. Блск 6 управления содержит элемент ИЛИ 19, элемент И 2С, S

21, формирователь 22 импульса, регистр

23., -.. p;II;ep 24 и распределитель им- 30 пульсов,, содержащий элементы И 25

28,, элементы ИЛИ 29 — 1, элемент 32 задержки, счетчики 33 и 34„ дешифратор 35 и генератор 36 !аипу!!ьсов.

Устройство работает следующим об.35 разом.

В исходном coстоянии триггеры 15 и 24 сброшены, олок 3 памяти содержит первьп обрабатываемы!! массив данных,. блок 4 памяти содержит второй обраба"",, тываемьп! Массив данных., Блоки 2 - 5 памяти имеют стековую структуру.

Перед запуском генератора 36 импульсов в регистр 7 записывается данное.

Счетчики 33, 34 и регистр 23 сброшены, „

C подачей разрешающего сигнала, разблокирующего генератор 36 импульсов, происходит запуск устройства„

По импульсам с выходов элементов 27, 31 происходит сдвиг информации из блока 3 в блок 2 памяти, в результате чего на первом выходе дешифратора

35 появляется уровень "i" сохраняющийся в течении (!1 + 1) — 21 тактов„ который подается на схему 8 сравнения, разрешая ее работу, и на первый упра ляющий вход коммутатора 9, который при отсутствии блокировки на втором управляющем входе подключает выход блока 2 памяти к входу блока 3 памяти.

В каждом такте схема 8 сравнивает кor, содержимого первого регистра блока 2 памяти с содержимым регистра 7, При сравнении этих кодов триггер 24 устанавливается в состояние "1", блокируя аботу устройства в момент появления азрешающего сигнала с второго выхода ! дешифратора 35.

Если в течение тактов (N + 1) — 2! сравнения содержимого регистра 7 с содержимым первого регистра блока 2 памяти не происходит, то содержимое блока 2 памяти переносится в блок 3 памяти. При этом на схеме 17 сравнения в течение тактов (N + 1) — 2N производится поиск первого нулевого (незначащего) элемента массива,.поступающего из блока 2 паь!ять!, путем сравнения каждого вновь поступающего элемента с кОДОм нуля При opBBHeIIHH очеред-.IoI о элемента с кодом нуля схема 17 сравнения выдает иа выходе сиг-. нал, временно (на один такт) бгокирующий тактовый вход распределителя импульсов и разрец!ающий прием кода

Ha pPI HeTpB 7 в последний påãистр блока 3 памяти и по прошествии указанного врРмени устанавливает триггер

15 в единицу, запрещая работу блока обработки рубежа в течен-.;е всех Ос"авшихся тактов работы устройства,.

На тактах (2N + 1) -- ÇN сигнал с ьтсрого выхода дешифратора 35 загрещает прием в блок 2 па:"«;H HIIIIiop:Ia HH из блока 3 памяти и pa=-решает и ием в блок 2 I!avirITH HI!формации из блока 4 памяти. Аналогично на тактах (311 + 1)— 4!1 информация из блока. 2 па::!яти сдвигается в третий блок памяти, сравниваясь в схеме 8 с содер!!!имьп! регистра 7. Переключение коммутатора

9 во время тактов (ЗМ + ) — Х происходит по сигчагу с трeòr eão выхода дешифратора 35. Если в течение тактов (ЗЧ + 1) — 4N в схеме 8 сравнения совпадает содержимое регистра

7 и регистра блока 2 памяти, то сигнал с выхода триггера 24 разрешает прием в регистр 23 номера текущего такта. (0 — N), во время которо-: го произошло сравнение информации, После этого информация заносится в блок 4 памяти из блока 2 памяти и на такте (4Ы + 1) сигналом с четвертого выхода дешифратора 35 блокируется работа генератора 36 импульсов, Этим

1.Устройство для поиска информации, содержащее блок управления, первый блок памяти и схему сравнения, первь|й информационный вход которой соединен с информационным входом устройства, о т л и ч а ю щ е с я тем, что,. с целью повышения быстродействия - стройства при поиске в неупорядоченном массиве и расширения функциональных возможностей за счет обновления информации в обрабатываемых массивах в зависимости от результата поиска, в него введены второй и третий блоки памяти, блок обработки рубежа и коммутатор, выход признака переключения которого соединен с синхровходом блока обработки рубежа, информационный выход которого поразряд4 но объединен с первым информационным выходом коммутатора и соединен с информационным входом второго блока памяти, первый выход которого поразрядно объединен с выходом третьего блока памяти и соединен с информа4 ционным входом первого блока памяти, выход которого соединен с вторым входом схемы сравнения и информацион ным входом коммутатора, второй инфор» мационный выход которого соединен с информационным входом третьего блока памяти, вход сдвига/записи которого соединен с первым выходом бло" ка управления, второй выход которого соединен с входом сдвига/записи первого блока памяти, третий выход блока управления соединен с входом сдвига второго блока памяти, второй вы55 з 144 же сигнапом разрешается прием кода в блок 5 памяти.

Таким образом, в результате работы устройства производится проверка массива данных, содержащегося в блоке 3 памяти, на наличие элемента, идентичного вновь вводимому данному из регистра 7, дописывание этого данного на первое свободное место в этот массив, затем поиск идентичного элемента во втором массиве данных, содержащемся в блоке 4 памяти, определение номера (адреса) этого элемента и добавление этого номера (адреса) в массив адресных констант, хранящийся в блоке 5 памяти. Среди данных и адресов не должно содержаться нулевых элементов. формулаизобретения

4 ход которого соединен с первым информационным входом блока обработки рубежа, второй информационный вход которого соединен с информационным входом устройства, четвертый выход блока управления соединен с синхро- входом схемы сравнения и первым управляющим входом коммутатора, второй управляющий вход которого соединен с пятым выходом блока управления, выход номера адреса и шестой выход которого являются выходом номера адреса и выходом сигнала сопровождения устройства, выход схемы сравнения соединен с входом останова блока управления, вход блокировки которого соединен с входом записи второго блока памяти и выходом признака сравнения блока обработки рубежа.

2 ° Устроиство IIo II 1, Q T JI H ч а ю щ е е с я тем, что блок управления содержит генератор импульсов, распределитель импульсов, элемент ИЛИ, 5 два элемента И, регистр и триггер, вход установки которого является входом останова блока, вход блокировки которого соединен с входом блокировки распределителя импульсов, с первого по шестой выходы которого являются выходами блока с первого по шестой соответственно, выход номера адреса которого соединен с выходом регистра, информационный вход которого соединен с группой выходов распределителя, седьмой выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом останова генератора импульсов, выход которого соединен с тактовым входом распределителя

О импульсов, восьмой выход которого соединен с первым входом первого элемента И, выход которого соединен с входом разрешения записи регистра, выход триггера соединен с вторым и первым входами первого и второго элементов

И соответственно, девятый выход распределителя импульсов соединен с вторым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ.

3. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок обработки рубежа содержит схему сравнения, формирователь импульса, элемент задержки, триггер и группу элементов И, выход которой является информационным выходом блока, вход логического нуля

144142 которого соединен с первым информационным входом схемы сравнения, вход синхронизации которой является входом синхронизации блока, первый и второй информационные входы которого соединены с первым и вторым информационными входами группы элементов И и схемы сравнения соответственно, выход последней соединен с входом формирова-1д теля импульса, выход которого является выходом признака сравнения блока и соединен с вторым входом группы элементов И и через элемент задержки— с входом установки триггера, выход которого соединен с входом блокировки выхода схемы сравнения.

4. Устройство по п. 1, о т л и— ч а ю щ е е с я гем, что коммутатор состоит из двух групп элементов И, элемента И и элемента задержки, выход которого является выходом признака переключения коммутатора, первый управляющий вход которого соединен с прямым входом элемента И, выход кото- 25 рого соединен с входом элемента зао б держки и первым входом первой группы элементов И, выход которой является первым информационным выходом ко -мутатора, второй информационный выход ко" торого соединен с выходом второй группы элементов И, первый вход которой является вторым управляющим входом коммутатора и соединен с инверсным входом элемента И, информационный вход коммутатора соединен с вторыми входами первой и второй групп элементов И.

5. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок памяти содержит последовательно соединенные по информационным входам/выходам и входам записи регистры, информационный вход первого из которых является информационным входом блока, первый выход которого соединен с выходом последнего регистра, входы чтения регистров объединены и являются входом сдвига блока, вход записи которого является входом зап: си первого регистра, выход которого является выходом блока.

1441420

Составитель Н.Матвеев

Редактор И.Рыбченко Техред Л.Олийнык

Корректор N. Васильева

Тираж 704 Подписное

ВНИИПО Государственного комитета СССР по делам изобретений и открытий

1l3Î35, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6291!54

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4