Дельта-кодер

Иллюстрации

Показать всеРеферат

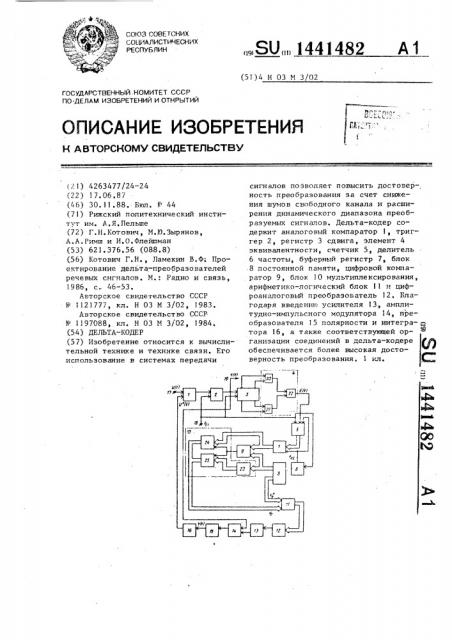

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи сигналов позволяет повысить достовер-, ность преобразования за счет снижения шумов свободного канала и расширения динамического диапазона преобразуемых сигналов. Дельта-кодер содержит аналоговый компаратор 1, триггер 2, регистр 3 сдвига, элемент 4 эквивалентности, счетчик 5, делитель 6 частоты, буферный регистр 7, блок .8 постоянной памяти, цифровой компаратор 9, блок 10 мультиплексирования, арифметико-логический блок II и цифроаналоговый преобразователь 12. Благодаря введению усилителя I3, амплитудно-импульсного модулятора 14, преобразователя 15 полярности и интегра-J2 тора 16, а также соответствующей S ганизации соединений в дельта-кодере обеспечивается более высокая достоверность преобразования. 1 кл. (Л

СОЮЗ COBF TCHHX

СОЫ1АЛИСТИЧЕСНИХ

РЕСПУБЛИН (5l)4 Н 03 М 3/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГА"

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н д BTOPCH0MV СВИДЕТЕЛЬСТВУ

12 1) 4263477/24-24 (22) 1 7. 06.8 i (46) 30. 11.88. Бюл. К 44 (71) Рижский политехнический институт им. А, Я. Пельше (72) Г. Н. Котович, M l0. Çûðÿíoâ, А.A.Pèìø и И.О.Флейшман (53) 621.376.56 (088.8) (56) Котович Г.Н., Ламекин В.Ф; Проектирование дельта-преобразователей речевых сигналов. M.: .Радио и связь, 1986, с. 46-53.

Авторское свидетельство СССР

Р 1121777, кл. Н 03 М 3/02, 1983.

Авторское свидетельство СССР

111 1197088, кл. Н 03 М 3/02, )984. (54) ДЕЛЬТА-КОДЕР (57) Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи

„„Я0„„1441482 А 1 сиги алов по зволяет повысить достовер-, ность преобразования за счет снижения шумов свободного канала и расширения динамического диапазона преобразуемых сигналов. Дельта-кодер содержит аналоговый компаратор 1, триггер 2, регистр 3 сдвига, элемент 4 эквивалентности, счетчик 5, делитель б частоты, буферный регистр 7, блок .8 постоянной памяти, цифровой компаратор 9, блок 10 мультиплексирования, арифметико-логический блок 11 и цифроаналоговый преобразователь 12. Благодаря введению усилителя 13, амплитудно-импульсного модулятора 14, преобразователя 15 полярности и интегратора 16, а также соответствующей организации соединений в дельта-кодере обеспечивается более высокая достоверность преобразования. 1 ил.

144 I -4 аж 929

Попписнае

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 пис ill()l î в б:l

5 группы 23. При поступлении с выхода компаратора 9 нулевого импульса, что соответствует V < V + d, на выходе с группы 25 элементов И-ИЕ появляется двоичное напряжение V + Л в параллельном коде, что делается с целью задания мичимального напряжения V +

+1, ниже которого не может быть напряжения V слогового интегратора, ° при этом (при дальнейшем вычитании

7с — 7 ) разность V с — V » всегда по— ложительная. Такая операция устраняет пульсации на выходе слогового интегратора (;.е. счетчика 5, делителя 2О

6 и регистра 7).

C выходов блока 10 на первый вход

ЛЛГ 11 поступает цифровой сигнал

Ч< Ч „-ь d .. Iа вторые входы АЛБ 11 заведены вторые выходы блока 8, где 25

B параллельном коде записано вычиты+ ваемое напряжение V Это напряжение вычитается с целью повышения степени сжатия динамического диапазона.

Разность Vp — о с выходов ЛЛБ 11 д11 в параллельном коде подается на входы

ЦАП 12, где греобразуется в аналоговое напряжение ", - Ч и, пройдя через усилитель 13, умножается на коэффициент К„. усиления, Полученное напряжение К c (V e — V o) поступает на первый вход AIII 14, на второй вход которого подается выходной сигнал

Y(t). С выхода AIBA 14 сиг à"ë 7(t) с амплитудой, измененной в соответствии 4О

» с уровнем К, (Vt — Vp) постугает на вход преобразователя 15 полярности.

С его вых >да двухполярное напряжение

U(t) гостуг ает на вход интегратора

16,.формирующего ступеньку аппроксимирующего напряжения U (t), поступающего на второй вход компаратора 1.

Таким образом, в дельта-кодере обеспечивается сжатие динамического ди;пазона и уменьшение шумов свободного канала в режиме холостого хода, благодаря чему повышается достоверность преобразования.

Формула изобретения

Дельта-кодер, содержащий аналогоьь:й компаратор, первый вход которого

В1ИИПИ Заказ 6296/57 Тир

82 4

sEEUlÿåòñÿ информационным вхолом дельта-кодера, выход соединен с информационным входом триггера, выход которого подключен к информационному входу регистра сдвига и является выходом дельта-кодера, тактовый вход регистра сдвига объединен с тактовым входом триггера и входом делителя частоты и является тактовым входом дельта-кодера, прямь.е и ипвер"ные выходы разря-, дов регистра сдвига соединены с пер- .выми и вторыми входами элемента эквивапентности, выход которого подключен к счетному входу счетчика, буферный регистр, блок постоянной памяти, первые выходы которого соединены с первыми входа@и цифрового компаратора, блок мультиплексирования арифметико-логический блок и цифроаналоговый преобразователь, о т л и ч а ю шийся тем, что, с целью повышения достоверности преобразования за счет снижения шумов свободного канала и расширения динамического диапазона преобразуемых сигналов, в дельта кодер введены усилитель и последовательно соединенные амплитудноимпульсный модулятор, преобразователь полярности ":: интегратор, выход которого подключен к второму входу аналоI овоrо компаратора, выход делителя частоты соединен с тактовым входом буферного регистра и входом обнуления счет .:.ика, тактовый вход которого подключен к тактовому входу дсльтакодера, выходы счетчика .-. зединены с информационными входами буферного регистра, выходы которого подключены к первым информаш онным входам блока мультиплексирования и соответствующим вторым входам цифрового компаратора, выход которого соединен с управляющим входом блока мультиплексирования„ вторые информационные входы которого подключены к первым выходам блока постоянной памяти, выходы блока мультиплексирования и ETopblB .выходы блока постоянной памяти соединены с первыми и вторыми входами арифметико-логического блока, выходы которого подключены к входам цифроаналогового преооразователя, выход которого через усилитель соединен с первым входом амплитудно-импульсного модулятора, второй вход которого подключен к выходу триггера.