Устройство для вычисления элементарных функций табличным методом

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и может быть применено в специализированных вычислителях . Целью изобретения является повышение точности вычисления функций за счет введения четвертого блока памяти и двух дополнительных сумматоров . Устройство осуществляет вычисление функции путем задания таблицы опорных значений функции и таблицы логарифмов скорости изменения функции по значениям старших разрядов аргумента в первом блоке памяти 2, задания логарифмов младших разрядов аргумента табличным методом во втором блоке памяти 3, вычисления логарифмов приращения функции между опорными точками суммированием значеиийГ логари( скорости изменения функции и младших разрядов аргумента в первом сумматоре 5, вычисления приращений функции в третьем блоке памяти 4 путем взятия антилогарифмов и последующего суммирования во втором сумматоре 7 значений функции в опорных точках с приращением функции, учета в четвертом блоке памяти 6 кода текущей погрешности аппроксимации функции между опорньми табличными значениями полиномом первого порядка, кодов усечения разрядных сеток операндов и суммирования значения функции с указанным кодом коррекции ошибки в третьем сумматоре 8. 1 ил. i (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 С 06 F 1/02, 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I (2l) 4238028/24-24 (22) 04.05,81 (46) 07.)2.88. Бюл. У 45 (71) Муромский филиал Владимирского политехнического института (72) В.В,Чекушкин (53) 681.325(088 ° 8) (56) Смолов В.Б. Функциональные преобразователи информации. " Л.: Знер- . гоиздат, 1981, с,30, рис.2-9, Авторское свидетельство СССР

У 826324, кл. С 06 F 7/38, 1981. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ ТАБЛИЧНЬИ МЕТОДОМ (57) Изобретение относится к вычислительной технике и может быть применено в специализированных вычислителях. Целью изобретения является повышение точности вычисления функций за счет введения четвертого блока памяти и двух дополнительных сумматоpos. Устройство осуществляет вычисление функции путем задания таблицы опорных значений функции и таблицы логарифмов скорости изменения функции по значениям старших разрядов аргумента в первом блоке памяти 2, задания логарифмов младших разрядов аргумента табличным методом во втором блоке памяти 3, вычисления логарифмов приращения функции между опорными точками суммированием значений( логарифмов скорости изменения функции и младших разрядов аргумента в первом сумматоре 5, вычисления приращений функции в третьем блоке памяти

4 путем взятия антилогарифмов и последующего суммирования во втором сумматоре 7 значений функции в опорных точках с приращением функции, учета в четвертом блоке памяти 6 кода -текущей погрешности аппройсимации функции между опорными табличными значениями полиномом первого порядка, ко- . дов усечения разрядных сеток операндов и суммирования значения функции с указанным кодом коррекции ошибки в третьем сумматоре 8. l ил.

1442984

Изобретение относится х вычислительной технике и может быть применено в специализированных вычислителях.

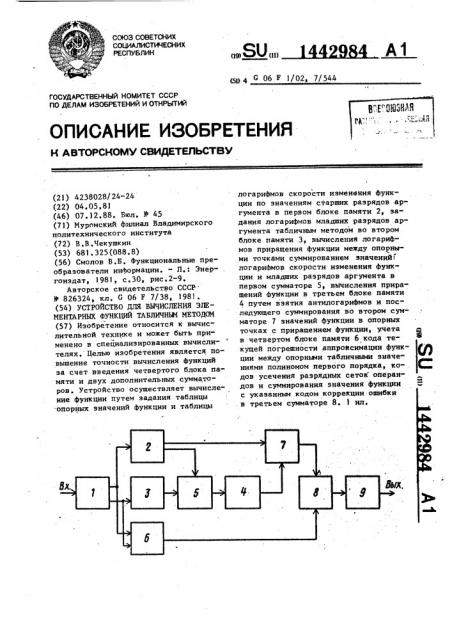

На чертеже представлена блок-схема предлагаемого устройства.

Целью изобретения является повышение точности, Устройство содержит регистр 1 ар- 1О гумента, первцй 2,.второй 3 и третий 4 блоки памяти, первый. сумматор

5, четвертый блок 6 памяти, второй 7 и третий 8 сумматоры и регистр 9 функ-. .ции. 15

Устройство работает следующим об- разом.

Входной параллельный код угла Р с регистра i аргумента разбивается на группы старших 1 и младших „ 2О разрядов, Все старшие разряды кода подаются на вход первого блока 2 памяти, а на первый вход четвертого . блока 6 памяти подаются лишь несколько старших разрядов. На втором выхо- 25 де первого блока, 2 памяти формируется код .функции sin P; в опорных точках j. Код функции з1.п p(задается в таблице с симметричным округлением, Таким образом, точность задания функции sin P в опорных точках

Ь „= "1/2 2

На первом выходе первого блока 2 памяти формируется логарифм скорости изменения функции в опорных точках

lnK;. Таблица значений логарифма строится с учетом полученных значений погрешностей функции sinp;, образом, эти погрешности в 4 значительной степени компенсируют в конечном счете друг друга, На вход второго блока 3 памяти подаются все младшие разряды кода Р .

Блок 3 памяти осуществляет вычисление логарифма аргумента с r дополнительными разрядами, На выходе первого сумматора 5 имеют логарифм приращения Функции. Этот логарифм третий блок 4 памяти переводит в действительное приращение Функции также с

r дополнительными разрядами. Непосредственно этот блок дает ошибку (и н 1

- 2 в приращении функции. На вы-55

2 ходе второго сумматора 7 имеют значение функции sin (3 с r дополнительными разрядами. Значение погрешности ) аппроксимации функции полиномом первого порядка определяется следующим выражением:

8 =(-Pi) (P Pjí ) .-„.---(p-P;) (P-P;„) in(, (1) где j — номер опорной точки.

С учетом пересчета в радианную меру угла максимальное значение ошибки аппроксимации

Четвертый блок 6 памятч осуществ" ляет приближенное формирование .суммарного кода коррекции ошибки аппроксимации в соответствии с (1) и кода коррекции ошибки урезания r дополни1 тельных разрядов в третьем сумматоре

8, Значение последней ошибки постоянно и равно 1/2 2, В четвери том блоке 6 памяти производится анализ значений только первых разрядов

KOQOB . Рс, H P g °

Третий сумматор 8 осуществляет суммирование значения функции c r дополнительными разрядами и значения кода коррекции ошибки.

Результирующая ошибка вычисления функции

1/2 ° 2-я + 2 (") 5 14

Ф о р м у л а и з о б р е. т е н и я.

Устройство для вычисления элементарных функций табличным методом, содержащее регистр аргумента, три блока памяти, первый сумматор и регистр функции, причем вход аргумента устройства соединен с информационными входами регистра аргумента,,выходы старших и младших разрядов которого соединены с адресными входами соответственно первого и второго блоков памяти, первый выход первого и выход второго блоков памяти соединены с входами соответственно первого и второго слагаемых первого сумматора, выход которого соединен с адресным входом третьего блока памяти, о тл и ч а ю щ е е с я тем что, с целью повышения точности, в него дополнительно введены второй и третий сумматоры и четвертый блок памяти, причем выходы младших разрядов ре" гистра аргумента соединены с первой

Составитель С.Куликов

Редактор О.Юрковецкая Техред Л.Сердюкова Корректор M.Øàðoøè

Заказ 6385/45 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж- 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

144 группой адресных входов четвертого блока памяти, вторая группа адресных входов которого соединена с выходами соответствующих старших разрядов регистра аргумента, второй выход первого блока памяти и выход третьего блока памяти соединены с входами первого и второго слагаемых второго сум2984 матора, выход которого соединен с входом первого слагаемого третьего сумматора, вход второго слагаемого

Б которого соединен с выходом четвертого блока памяти, выход которого соединен с информационными входами регистра функции, выход которого является выходом результата устройства.