Устройство для синхронизации модулей вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и можетбыть использовано при построении вычислительных систем на основе об-:-. щей магистрали при необходимости организации надежной работы синхронизации нескольких одновременно работающих модулей. Целью изобретения является повьшение помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы. Предложенное устройство состоит из активного и группы пассивных блоков синхронизации, каждый из которых связан с модулем вычислительной системы. В блок синхронизации входит коммутатор и распреде-пи гель, содержащий . три....алемента-1 И-ИЛИ-НЕ, три элемента НЕ, три элемента И-НЕ. 4 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 09) (И) А1 (51)4 G 06 F i/04, 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4125020/24-24 (22) 29 ° 09.86 (46) 07. 12. 88. Бюл. Р 45 (71) Ленинградский электротехнический институт им. В.И. Ульянова (Ленина) (72) Л.Я. Розенблюм, О .А, Федорова, . А.В. Яковлев и И.В. Яценко (53) 681. 325(088.8) (56) Sutherland I.Е. et. а1. The

ТКХИОБВЦЯ. — Proc. Caltechconference

on VLSI, 1979., р. 395-427, 409, fig. 5b.

Taub D.Ì. Pardwa re method of

synhronising processes without a

clock. — Electronic letters, 1983, ч. 19, Р 19, р. 772-773.. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

МОДУЛЕЙ ВИЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении вычислительных систем на основе об-:: щей магистрали при необходимости организации надежной работы синхронизации нескольких одновременно работакщих модулей. Целью изобретения является повышение помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы. Предложенное устройство состоит иэ активного и группы пассивных блоков синхронизации, каждый из которых связан с модулем вычислительной системы. В блок синхронизации входит коммутатор и распределитель, содержащий . три элемента.

И-ИЛИ-НЕ, три элемента НЕ, три эле-мента И-НЕ. 4 ил.

1442985

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении вычислительных систем на основе об5 щей магистрали при необходимости органиэации надежной работы синхрони- зации нескольких одновременно работающих модулей. . Целью изобретения является повышение помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы.

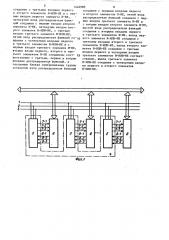

На фиг. 1 представлена блок-схема системы с использованием предложенного устройства; на фиг. 2 — схема активного блока синхронизации; на фиг. 3 — пример реализации пассивных блоков синхронизации; на фиг. 4— временная диаграмма работы устройст- 20 ва.

В состав общей магистрали входят командные шины 1 "3, предложенное устройство 4 вычислительной системы, содержащее блоки 5 синхронизации, 25 соединенное с модулями б вычислительной системы шиками 7 и 8 .запрос-ответ.

Блок 5 синхронизации содержит (фиг. 3 и 4) коммутатор 9, соединенный через выходы 10 с раепределителем 11 функций, элементы И-НЕ 12, И-ИЛИ-НЕ 13 и НЕ 14.

Устройство работает следующим образом.

В исходном состоянии после установки на шинах 1-3 устанавливается команда 110.

Принцип синхронизации модулей заключается в следующем.

Задающий блок синхронизации выдает на стык запрос на выполнение одной из трех операций (фиг. 4), которым присваивают символы i, j и 1: (например i 1, j 3, k = 2). Считают, что текущей операции предшествует операция j, а последующей является операция k. Выполнение операции i начинается в исходном состоянии с того, что в задающем блоке сигнал на выходе 7-i переходит нэ "1" в "О", после чего. через некоторое время (равное длительности выполнения этой операции активным модулем) задающий

- блок получает сигнал ответа по входу

8-i {переключение иэ 1 в О ).

11 11 !! II $5

После этого командная шина i переходит в состояние низкого потенциала

"О" что вызывает последовательно пе,Ф реходы иэ "1" в "0" на шинах 7-i u

8-i в остальных ячейках, причем функционирование соответствующих им модулей происходит параллельно. После отработки всеми модулями операции i шина может установиться в состояние высокого потенциала "!". На этом заканчивается рабочая фаза выполнения операции i. Начинается фаза гашения, в ходе которой все блоки одновремен но выставляют значение "1" на выходах 7-i. После получения "1" на входах 8-i задающий блок начинает выполнение следующей операции, à so всех остальных блоках установка всех входов 8-i в "1" служит условием, необ.-,: ходимым для возврата шины i a следующей операции в состояние высокого потенциала.

В каждом из блоков на выходах

10-1 !0-3 коммутатора 9 установлены соответственно "! "1" и "О". На выходах элементов И вЂ” НЕ 12-i, соответствующих входам 7-i запроса синхронизируемого модуля б„ а также на выхо:I дах 8 †ответа того же модуля установлены "1". Выходы элементов

И-ИЛИ-НЕ 13"1 — 13-3 находятся соответственно в состояниях "0", "О" и

"1", а выходы элементов НЕ 14-i соответствуют состояниям командных шин.

Последовательность действий устройства при выполнении i-й (i 1, 2, 3) запрос-ответной операции по синхронизации модулей 6 следующая. В одном из блоков, задающих синхронизацию, происходит переключение элемента И-НЕ 12-1 иэ "1" в " О", тем самым выдается сигнал запроса модуля б для выполнения i-й операции. После ее выполнения модуль 6 выдает сигнал ответа путем переключения выхода

8-i из "1" в "О", после чего переключается элемент И-ИЛИ-НЕ 13-i иэ

"0" в "! вызывая затем переключение элемента НЕ 14-1 из "1" в "0".

Тем самым шина i приобретает низкий потенциал "О".

Переход шины i в "0" вызывает.паг. раллельные переключения в самом задающем блоке и во всех остальных блоках. В задающем блоке процесс продолжается так. Выход 10-i коммутатора 9 переходит из "O" в "1", затем элемент И-ИЛИ-НЕ 13-j (для i 1, 2, 3; j 3, 2, 1 соответственно) переходит из "1" в О"., вызывая переключение элемента НЕ 14-j нз "0" в "1".

1О

35

55

3 14

Однако, так как выход элемента НЕ

14-1 подключен к шине j по и!;оводному ИЛИ, шина j переходит в состояние высокого потенциала "1" лишь в ре-зультате срабатывания из "0" в элементов НЕ 14-1 во всех остальных блоках устройства; В n; т на переход шины х в "0" происходит переключение выхода 10-.i коммутатор 9 дз

If !! tl. u

0 в 1, после чего элсмен И-ЧЕ

12-1 переключается в,"Г", теь самым выдавая сигнал запроса модуля ча вы" полнение i-й операции. После ее выполнения модуль 6 ьндает сигнал ответа путем переключения своего выхода 8-i из "1" в "0", что вызывает переход элеме ".а Р -ИЛИ-HE 13-i из, "0" в ")", а затем элемента НЕ 14-j дэ "1" в "0" и элемента И-ИЛИ-НЕ

13-j из "I" в "0, после чего элемент НЕ 14-j переходит из "0" в "1", вызывая переход управляющей линии j в состояние высокого потенциала 1" (эффект проводного ИЛИ).

Таким образом, к .моменту переключения линии j из состояния низкого потенциала "0" в состояние высокого потенциала "1" все модули завершили операцию i, Далее начинается фаза гашения сигналов запроса и ответа по i-й операции. В задающем блоке она происходит, следующим образом. После перехода шины j в состояние "1" выход 10-j коммутатора 9 .переходит из "1" в "0", вызывая далее переход выхода элемен- та И-НЕ 12-i из "0" в "I" (гашение модуля 6 путем возврата сигнала запроса по входу 7"i в "1"), а после гашения модуля 6 последний восстанавливает на выходе 8-i ответа значе. ние "1", после чего элемент И-НЕ 12-k (для i =* 1, 2, 3; I: = 2, 3, 1) переключается из "1" в "0", начиная тем, самым выполнение фазы запроса и ответа k-й операции, которая выполняется ана.огично i-й с учетом того, что сийвон, j, k описания заменяются на k i, j соответственно.

Gapanneëüéî в остальных ячейках после перехода шины j в состояние

"1" выход 10-j коммутатора 9 перехо-,. дит из "l" в "0", вызывая далее переход выхода элемента НЕ 14-д иэ "0" в "I" а после гашения модуля 6 последний восстанавливает иа выходе 8-i ответа значение "I"; затем оно служит условием для переключения элемента

42985 .И-ИЛИ-HE 13-i из "1" в "0" при выполнении j-й операции.

Формула изобретения ).

Устройство для синхронизации мо дугей вычислительной системы, содержащее группу блоков синхронизации по числу модулей вычислительной системы, каждый из которых содержит коммутатор и распределитель функций, причем в каждом блоке синхронизации группы первый, второй и третий выходы распределителя функций соединены с соответствующими информационными входами коммутатора и в совокупности образуют входы †выхо устройства для подключения к командным шинам управляющей магистрали вычислительной системы, четвертый, пятый и шестой выходы распределителя функций являются выходами устройства для подключения к первому, второму и третьему входам запроса соответствующего модуля вычислительной системы, первый, второй и третий входы распределителя функций каждого блока синхронизации группы являются входами устройства для подключения к первому, второму и третьему выходам ответа соответствующего модуля вычислительной систеи-.. мы, в каждом блоке синхронизации группы первый, второй и третий выходы коммутатора соединены соответственно с четвертым, пятым, шестым входами распределителя функций, о т л и ч аю щ е е с я тем, что, с целью повы-, . шения помехоустойчивости устройства при одновременной работе нескольких модулей вычислительной системы, группа блоков синхронизации состоит из активного и пассивных блоков синхронизации, в каждом блоке синхронизации группы распределитель функций содержит три элемента И-ИЛИ-НЕ, три элемента И-НЕ и три элемента Е1Е с открытым коллектором, выходы которых являются соответственно первым,. вторым и третьим выходами распределителя функций, первый, второй и третий входы которого соединены соответственно с объединенными первыми и вторыми входами первого, второго, третьего элементов И-ИЛИ-НЕ, выходы которых соединены с входами соответствующих элементов НЕ с открытым коллектором, в активном блоке синхронизации r-руппы шестой вход распределителя функций.

985

5 1442 соединен с третьими входами первого и второго элементов И-ИЛИ-НЕ и с первым входом первого элемента И-НЕ, четвертый вход распределителя Функций соединен с первым входом второго

5 элемента И-НЕ, четвертым входом второго элемента И-ИЛИ"НЕ, с третьим входом третьего элемента И-ИЛИ-НЕ, пятый вход распределителя функций со- 0 единен с четвертыми входами первого н третьего элементов И-HJIH-НЕ и с первым входом третьего элемента И-НЕ, вторые входы первого, второго и третьего элементов И-НЕ соединены соот- 15 ветственно с третьим, первым,и вторым входами распределителя Функций, в пассивных блоках синхронизации группы четвертый вход распределителя функций соединен с первыми входами первого и второго элементов И-НЕ, пятый вход распределителя функций соединен с первым входом третьего элемента И-HE u с вторым входом второго элемента И-HF, шестой вход распределителя функций соединен с вторыми входами первого и третьего элементов И-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с третьими входами второго и третьего элементов И-ИЛИ"НЕ, выход второго элемента И-ИЛИ-HE соединен с третьим входом первого и четвертым: входом третьего элементов И-ИЛИ-НЕ соответственно, выход третьего элемента.

Ff-ИЛИ-НЕ соединен с четвертыми входами первого и второго элементов

И-ИЛИ-НЕ.

) 442985

1442985

Составитель Г. Стернин

Редактор О. Юрковецкая Техред Л.Сердюкова Корректор М, Деичик

Подписное

Тираж 704

Заказ 6385/45

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4