Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Постоянное запоминающее устройство предназначено для использования в области вычислительной техники для создания БИС ЗУ. Целью изобретения является упрощение устройства за счет уменьшения количества шин программирования. Поставленная задача решается тем, что в качестве запоминающего элемента (ЗЭ) используется НДП-транзистор, и дешифратор строк имеет,прямые и инверсные вьосоды, что обеспечивает использование ЗЭ как передающего или инвертирующего в зависимости от программируемой информации, , следствием чего является уменьшение количества шин, подводимых к каждому ЗЭ, приблизительно на 40%. 2 ил.

СО)ОЗ СОБЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„80„„1443030 А 1 ()Л 4 G ll С 17/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

110 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К д BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4219446/24-24 (22) 02. 04. 87 (46) 07. 12. 88. Бюл. ¹ 45 (72) А.И. Комарова и Е.В. Федоров (53) 681. 327. 66 (088. 8) (56) Авторское свидетельство СССР № 881862, кл. G 11 С 17/00, 1980.

Авторское свидетельство СССР

¹ 1096694, кл. С 11 С 17/00, 1982. (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Постоянное запоминающее устройство предназначено для использования в области вычислительной техники для создания БИС ЗУ. Целью изобретения является упрощение устройства за счет уменьшения количества шин программирования. Поставленная задача решается тем, что в качестве запоминающего элемента (33) используется НДП-транзистор, и дешифратор строк имеет, прямые и инверсные выходы, что обеспечивает использование ЗЭ как передающего или инвертирующего в зависимости от программируемой информации, о следствием чего является уменьшение количества шин, подводимых к камсцому ЗЭ, приблизительно íà 40Х. 2 ил.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

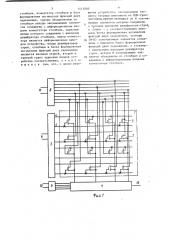

Изобретение относится к вычисли- выходов — прямых 4 и инверсных 5

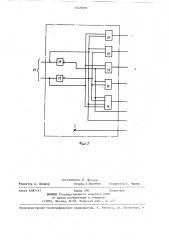

S тельной технике и может быть ис- дешифратор 6 столбцов, коммутатор 7 пользовано для построения запоми- столбцов, блок 8 формирования логиченающих устройств в виде интеграль5 ских функций двух переменных три

1 ных схем. группы адресных входов 9-11 и выЦель изобретения — упрощение уст- ход 12. ройства за счет сокращения количест— ва шин программирования. Блок 8 формирования логических функНа фиг. 1 приведена схема ПЗУ, на !0 ций от двух переменных содержит, нафиг. 2 — схема блока формирования ло- пример, два элемента НЕ 13, элемент гических функций. ИСКЛ10ЧА10ЩЕЕ ИЛИ 14 и четыре элеменУстройство содержит матрицу 1 из та И 15.

M запоминающих элементов 2, дешиф- Полный набор логических функций от ратор 3 строк, имеющий две группы 15 двух переменных следующий:

f = А!ЛА2; f = AlhA2; f = А1ЛА2;

2 1 3

Г = AIAA2 К = Ai vA2; и = AIVA7;

Ет = Al V A2; Ев Al А2

К = (A!ÜA2) Y(AIAA2); f „= (А1ЛА2) 4(AIt A2)

Причем функции f <, Е2, f» f 9, f 9, f «, Г, f < инверсны соответственно функциям Ь .1 Е б 1 7 1 51 <а 1 <2 1 25 <9 1 <6 °

В предлагаемом устройстве блок 8 формирования логических функций формирует, например, прямые функции f 21 91 а 1 9 1 << 1 Я<3 1 Й<5. Функ — ЗО ционирование предлагаемого ПЗУ основывается на свойстве запоминающих элементов 2, выполненных на транзисторах, передавать прямое или инверсное значение функции в зависимости от того, к какому входу запоминающего элемента подключен выход блока 8 формирования логических функций.

Устройство работает следующим образом. сЩ

Разряды кода с адресных входов 9 и

l0 поступают соответственно на входы дешифраторов строк 3 и столбцов 6, два разряда кода с адресного входа

11 поступают на входы блока 8 форми- 45 рования логических функций. При этом происходит выборка запоминающего элемента 2, находящегося на пересечении строки и столбца матрицы 1, соответствующих поданному на входы 9 и 10. коду адреса.

У выбранного запоминающего элемента 2 первый вход подключен к одному из выходов 4 дешифратора 3 строк, имеющему при данном коде адреса состояние логической "1", либо второй вход подключен к одному из выходов 5 дешифратора 3 строк, имеющему при данном коде адреса состояние логического "0". При этом на выходе запоминающего элемента 2 формируется соответственно значение функции, соответствующей выходу блока 8, подключенному к второму входу данного запоминающего элемента 2, либо инверсное значение функции, соответствующей выходу блока 8, подключенному к первому входу запоминающего элемента 2.

Таким образом, если .в матрице из

11 запоминающих элементов 2 необходимо на К запоминающих элементах программировать значения функций f<, а 9 « (М-К) элементах — инверсные значения этих функций, то в первом случае соответствующие выходы блока 8 f< -fа1

f „, f f,- подключаются к вторьм входам запоминающих элементов 2, а их первые входы — к соответствующим выходам 4 дешифратора строк, а во втором случае соответствующие выXOPbt 6JIOKB 8 f f9 1 f91,f„1 f < 1

f подключаются к первым входам запоминающих элементов 2, а их вторые входы — к соответствующим выходам 5 дешифратора строк.

Технико †экономическ преимущества предлагаемого устройства заключаются в том, что сокращается в 2 раза количество шин программирования.

Ф о р м у л а изобретения

Постоянное запоминающее устройство, содержащее матрицу из М запоминающих элементов, дешифраторы строк и! 443030 столбцов, коммутатор столбцов и блок формирования логических функций двух переменных, причем объединенные по столбцам выходы запоминающих элементов соединены с информационными входами коммутатора столбцов, адресные входы которого соединены с выходами дешифратора столбцов, выход коммутатора является информационным выходом устройства, входы дешифраторов строк, столбцов и блока формирования логических функций двух переменных являются входами первой, второй и третьей групп адресных входов устройства соответственно, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, запоминающие элементы матрицы выполнены на МДП-транзисторах, причем затворы К из M запоминающих элементов матрицы соединены

5 с прямыми выходами дешифратора строк а стоки — с соответствующими выходами блока формирования логических функций двух переменных, затворы g (M — К) запоминающих элементов соединены с выходами блока формирования функций двух переменных, а стоками— с инверсными выходами дешифратора строк, истоки М запоминающих эле) ментов объединены ио столбцам и соединены с информационными входами коммутатора столбцов.

E 443030

Составитель Н. Шустов

Техред A.Кравчук, Корректор С. Черни

Редактор А. Шандор

Тираж 590 Подписное

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6387/47

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4