Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и связи. Цель изобретения - расширение диапазона частот входного сигнала. Умножитель частоты содержит формирователь 1 импульсов, регистры 2 и 3 памяти, эл-ты задержки 4 и 5, счетчики 6 и 7, делитель 8 частоты с переменньт коэф. деления, делитель 9 частоты, опорный г-р 10, блок орав-, нения 11 кодов и управляемые делители 12 и 13 частоты. Цель достигается путем реализации высоких коэф. деления без,снижения быстродействия.1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИ4ЕСНИХ

РЕСПУБЛИК (51)4 Н 03 В 19/00

КГОИЗИЦ

Цайъ :d 1„„:ð Лс„:!и

i;óÜéÈO i C.::

ОПИОАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3981436/24-09 (22) 25.11.85 (46) 07.12.88. Бил. М- 45 (71) Харьковский филиал Центрального конструкторского бюро Главэнергоремонта (72) В. К.Боярчук, В.Я. Красюк, В.Н.1!аслий и С.Я.Попов (53) 621. 374. 44 (088. 8) (56) Авторское свидетельство СССР

У 836756, кл. Н 03 В 19/00, 27.07. 79.

Авторское свидетельство СССР

У 1238194,кл. Н 03 В 19/00, 10.11,84.

Я0 1443121 А i (54) У1 1НОЖИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к радиотехнике и связи. Цель изобретения— расширение диапазона частот входного сигнала. Умножитель частоты содержит формирователь 1 импульсов, регистры

2 и 3 памяти, эл-ты задержки 4 и 5, счетчики 6 и 7, делитель 8 частоты с переменным коэф. деления, делитель 9 частоты, опорный г-р 10, блок сравнения 11 кодов и управляемые делители 12 и 13 частоты. Цель достигается путем реализации высоких коэф. деления без снижения быстродействия.1 ил.! 443121

Изобретение относится к радиотехнике и связи и может быть использовано в измерительной технике.

Цель изобретения — расширение диа5 пазона частот входного сигнала.

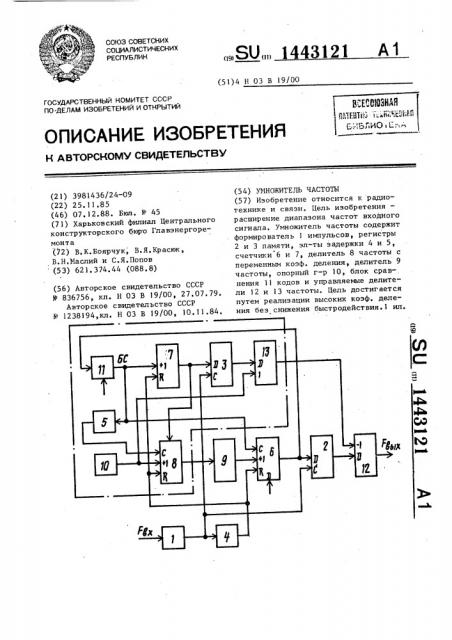

На чертеже представлена структурная электрическая схема умножителя частоты.

Умножитель частоты содержит форми- IP рователь 1 импульсов, первый 2 и второй Э регистры памяти, первый 4 и второй S элементы задержки, первый 6 и второй 7 счетчики, делитель 8 частоты с переменным коэффициентом де- !5 ления, делитель 9 частоты, опорный генератор 10, блок I! сравнения кодов, первый 12 и второй 13 управляемые делители частоты.

Умножитель частоты работает сле- 20 дующим образом.

В начале каждого периода входного сигнала формирователь 1 формирует короткий импульс, который поступает на входы записи первого 2 и второго 3 25 регистров и на вход первого элемента

4 задержки. Задержанный импульс поступает на вход начальной установки первого 6 и второго 7 счетчиков и делителя 8, коэффициент деления которо-. 30 го К, устанавливается равным единице.

Периодическая последовательность импульсов с частотой ог

Я

К,К

35 .где К вЂ” коэффициент деления делителя 9;

F — частота следования импульсов

or на выходе опорного генератора 1О, 40 поступает на счетный вход первого счетчика 6, При совпадении текущего значения двоичного кода на выходе первого счетчика 6 с двоичным кодом, установ- 45 ленным в блоке 11 сравнения кодов,на выходе последнего формируется импульс, который поступает на установочный вход первого счетчика 6 и на счетный вход второго счетчика 7 ° при этом значение двоичного кода на выходе первого счетчика 6 уменьшается в два раза, а значение двоичного кода на выходе второго счетчика 7 удваива ется (начальное состояние второго счетчика 7 соответствует единице).

Сформированный на выходе блока 11 сравнения кодов импульс через второй элемент 5 задержки поступает на вход записи делителя 8, коэффициент деления которого увеличивается в два раза. Таким образом, значение двоичного кода на выходе второго счетчика 7 и значение коэффициента деления делителя 8 совпадают, а количество импульсов на выходе опорного генератора 10 за один период входного сигнала К =

= К„ К К, где Кз — значение двоичного кода на выходе первого счетчика 6. С приходом очередного импульса с выхода формирователя I текущие значения (К и К,) двоичных кодов с выходов первого 6 и второго 7 счетчиков переписываются соответственно в первый 2 и второй 3 регистры, а первый 6 и второй 7 счетчики и делитель 8 устанавливаются в начальное состояние, с которого начинается измерение очередного периода входного сигнала. Коэффициент деления первого управляемого делителя 12 принимает значение К, а коэффициент деления второго управляемого делителя 13 " К . Частота сигнала на выходе умножителя частоты может быть представлена в виде

For

Зй к к л а частота входного сигнала

Fог

Вх К тогда Ох

F — — — -- = F ° К еых К, К вх з

Коэффициент деления второго управляемого делителя 13 принимает значения: К, = 1,2,4,...,2", где и — количество разрядов второго управляемого делителя 13. Указанная особенность позволяет реализовать высокие коэффициенты деления без снижения быстродействия, что приводит к расширению диапазона частот входного сигнала.

Формула изобретения

Умножитель частоты, содержащий последовательно соединенные делитель частоты, первый счетчик, первый регистр памяти и первый управляемый делитель частоты, опорный генератор, формирователь импульсов и первый элемент задержки, вход которого соединен с входом записи первого регистра памяти, о т л и ч а ю щ и.й с я тем, что, с целью расширения диапазона частот входного сигнала, введены по"

1443!

Составитель Ю.Максимов

Техред M.Äèäûê Корректор М. Демчик

Редактор М.Бланар

Заказ 6393/52 Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 следовательно соединенные блок сравнения кодов, второй счетчик, второй регистр памяти и второй управляемый делитель частоты, делитель частоты с переменным коэффициентом деления и второй элемент задержки, выход которого соединен с входом записи делителя частоты с переменным коэффициентом деления, входы начальной установ- 0 ки первого и второго счетчиков и делителя частоты с переменным коэффициентом деления соединены с выходом первого элемента задержки, вход которого соединен с выходом формирова- 15 теля импульсов и с входом записи второго регистра памяти, выход опор21

4 ного генератора соединен со счетным входом делителя частоты с переменным коэффициентом деления и с счетным входом второго управляемого делителя частоты, выход которого соединен со счетным входом первого управляемого делителя частоты, выход первого счетчика соединен с входом блока сравнения кодов, выход которого соединен с установочным входом первого счетчика и с входом второго элемента задержки, выход второго счетчика соединен с ин" формационным входом делителя частоты с переменным коэффициентом деления, выход которого соединен с входом делителя частоты.