Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - повьшение точности подстройки фазы при выполнении фазового детектора с релейной х-кой. Устр-во содержит опорный г-р 1, дапители 2 и 4 с переменным коэф. деления,фазовый детектор 3 с релейной х-кой, управляемый г-р 5, . блоки установки 6 и 10 делителя, блок выбора 7 режимов, цифровой вычислитель 8 сигнала ошибки и преобразователь 9 цифра - аналог. Цель достигается за счет возможностей более точного измерения разности фаз сигналов. 6 ил., 2 табл. Вымд (Л ф 4i С Ч СО

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1443173 (51)4 Н 03 r. 7 00

11 э " Ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО-ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ и A BTOPCHGMY СВИДЕТЕЛЬСТВУ (21) 4164083/24-09 (22) 18. 12.86 (46) 07.12.88 Бюг.. w 45 (72) H.H Колтуков (53) 621.396.666(088.8) (56) Авторское свидетельство СССР

Р 932623, кл. Н 03 L 777/ 0088, 1980. (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение точности подстройки фазы при выполнении фазового детектора с релейной х-кой. Устр-во содержит опорный г-р 1, делители 2 и 4 с переменным козф. деления,фазовйй детектор 3 с релейной х-кой, управляемый r-p 5, блоки установки 6 и 10 делителя, блок выбора 7 режимов, цифровой вычислитель 8 сигнала ошибки и преобразователь 9 цифра — аналог. Цель достигается за счет возможностей более точного измерения разности фаэ сигналов.

6 ил., 2 табл. дыхок

1443173

Изобретение относится к радиотехнике и может быть использовано в устройствах авторегулирования частоты и фазы сигналов.

Цель изобретения — повышение точности подстройки фазы при выполнении фазового детектора. с релейной характеристикой. 10

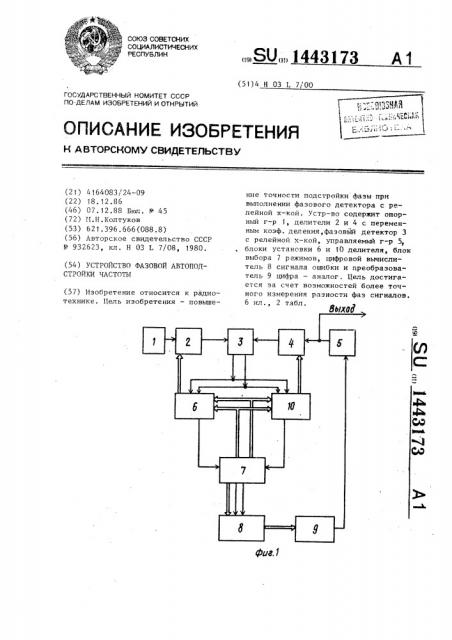

Ня фиг. 1 представлена структурная электрическая схема устройства фазовай автападстройки частоты; на фиг.2 — структурная электрическая схе. мя первого и второго блоков установки делителя; ня фиг. 3 — структурная электрическая схема. блока выбора режимов; ня фиг.4 -- пример выпалне— ния фязогага детектора с релейной характеристикой; на фиг.5 и 6 — при- 2О меры выпал-. †:.ения цифрового вычислителя сигналя ошибки.

Устройство Фазавой автаподстройки частоты содержит опорный генератор 1, первый делитель 2 с переменным каэф- 25 фициентам деления (ДПКД), фазовый детектор 3 с релейной хяряктеристи— кай„ второй ДПКП 4, управляемый генератор 5,, первый блок 6 установки де-! лителя (БУД), блок 7 выбора режимов, 30 цифровой вычислитель 8 сигнала ошибки, преобразователь 9 цифра — аналог, второй БУД 10, при этом первый и второй БУД содержат формирователь 11 импульсов„первbIA дешифратор 12 и

35 элемент i3 памяти, блок 7 выбора режимов содержит элемент ИЛИ 14, счет— чик 15. второй дешифратор 16 и ячей— ку 17 памяти, цифровой вычислитель 8 сигнала ошибки, реализующий статичес- А кие свойства устройства, как системы автаподстройки фазы, содержит дво— ичный счетчик 18 и блок 19 памяти, а цифровой вычислитель 8 сигнала ошибки, реализующий статические свойства устройства, как системы автоподстройки фазы, содержит цифровой счетчик 20, первый регистр 21 памяти, трехвходовый сумматор 22, блок 23 выбора,двухвхадавый сумматор 24 и второй регистр 25 паь.яти.

".c pGAcTB0 Ip83oBoH автападстрайки частоты работает следующим образам.

Первый 2 и второй 4 ДПКД формируют сигналы с различными периодами соответственна из сигнала опорного генератора 1 и выходного сигнала, получаемого ат управляемого генератора 5.0тличие в длине периодов всегда имеет заданную определенную величину при каждой паре коэффициентов деления первого 2 и второго 4 Д КД.Фазовый детектор 3 сравнивает ва времени моменты поступления сигналов с первого 2 и второго 4 ДПКД и фиксирует полярность сигнала ошибки, Если сигнал с второго ДПКД 4 поступил раньше, то фазовый детектор 3 выдает сигнал ошибки опережения (ОП), а если отстает, та отставания (ОТ). Первый и второй БУД по полярности сигнала ошибки устанавливают коэффициенты деления первого 2 и второго 4 ДПКД таким образом, чтобы эту ошибку уменьшить, а затем изменить ее полярность.В конце общего периода сравнения, который определяется счетчиком 15 в блоке 7 выбора режима, коэффициенты деления первого 2 и второго 4 ДПКД устанавливаются такими, чтобы общий период сравнения фаз поделенных сигналов (N сигналов с первого 2 и второго 4 ДПКЛ)бып одинаков для эталонного сигнала и сигнала управляемого генератора. Порядок изменения коэффициентов деления первого 2 и второго 4 ДПКД устанавливается сигналами управления с блока 7 выбора режимов.

Один из этих сигналов указывает на порядок сближения фаз поделенных сигналов, а другой на число этапов сравнения, по которым формируется общий период сравнения. Результаты грубога сравнения фаз, когда периоды сигналов с первого 2 и второго 4 ДПКД сильно отличаются друг от друга, формируют сигнал установки в блоке 7 выбора режимов, который поступает на цифровой вычислитель 8, а результаты точного сближения фаз сигналов с первого 2 и второго 4 ДПКД, когда их периоды отличаются незначительно (вплоть до тысячных долей такта управляемого генератора 5) подаются на циФровой вычислитель 8 с блока 7 выбора ревкомов в виде импульсов счета числа сравнений. Начало нового общего периода сравнения соответствует формированию сигнала перезаписи,который также подается с блока 7 выбора режимов на цифровой вычислитель 8.Выходной сигнал; сформированный в цифровом вычислителе 8, преобразуется с помощью преобразователя 9 в управляющий сигнал, который поступает на управляемый генератор 5.

Устройство фазовой автоподстройки частоты, содержащее соединенные последовательно опорный генератор, первый делитель с переменным коэффициентом деления и фазовый детектор, второй вход которого соединен с выходом второго делителя с переменным коэффициентом деления, а также управляемый генератор, выход которого подключен к входу второго делителя с переменным коэффициентом деления, о т л и ч а ю щ е е с я тем, что, с целью повышения точности подстройки фазы при выполнении фазового детектора с релейной характеристикой, в него введены между первым выходом фазового детектора и управляющим входом управляемого генератора последовательно соединенные первый блок уста,новки делителя, блок выбора режимов, цифровой вычислитель сигнала ошибки и преобразователь цифра-аналог, меж- . ду вторым выходом фазового детектора и вторым входом блока выбора режимов введен второй блок установки делителя, выходы управления блока выбора з 14431

Входные сравниваемые сигналы с первого 2 и второго 4 ДПКД имеют положительную полярность. Фазовый детектор 3 фиксирует какой из входных сиг5 налов поступил раньше и на выходе фазового детектора 3 устанавливается . сигнал ошибки "ОТ" или "ОП" .

В формирователе 11 импульсов в

БУД 6 или БУД 10 из входных сигналов фазового детектора 3 формируются тактовые импульсы а и в. При поступлении сигнала ОТ (ОП), что соответствует напряжению логической единицы и до поступления с фазового детектора 3 нулевого потенциала, на выходе в(а) имеется положительный сигнал логической единицы.

Первый дешифратор 12 по заданной табл. 1 истинности устанавливает нужный коэффициент, деления в ДПКД, который запоминается элементом 13 памяти. Выходной сигнал первого дешифратора 12 зависит от сигналов на цифровых входах С и С1 с БВР 7 и вход- 25 ных сигналов в или а.

Блок выбора режимов (БВР) 7 работает следующим образом: счетчик 15 считает число тактов в или а, поступающих к нему на вход через элемент ИЛИ 14. д0

Последнее состояние счетчика соответствует началу общего периода сравнения фаз. Сигнал с выходов счетчика 15 (цифровой код) С1 подается на выход управления БВР 7 и на второй дешифратор 16. Таблица истинности второго дешифратора 16 приведена в табл.2.

Данные с второго дешифратора 16 поступают на ячейку 17 памяти и с нее в виде сигнала С на вход второго де- 40 шифратора 16 и на выход управления

БВР 7 (С). Формирование сигналов с второго дешифратора 16 происходит в соответствии с тактами в и а. Кроме того, во втором дешифратора 16 форми- 4> руются сигналы "счета" (е), "установки" (8) и "перезаписи" (h), которые поступают в цифровой вычислитель 8 (табл.2).

В цифровом вычислителе 8 сигнал

"установки" определяет начальное состояние двоичного счетчика 18 а сигнал "Счет", поступивший на счетный вход, уточняет это значение °

В конце общего цикла сравнения сигналом "перезаписи" данные с двоичного счетчика 18 перезаписываются в блок 19 памяти и оттуда поступают на выход цифрового вычислителя 8 для преобра73 4 зования в преобразователе 9 и управления частотой управляемого генератора 5.

В случае использования цифрового вычислителя 8 в виде фиг.6 сигналы с цифрового счетчика 20 (А) перезаписываются в первый регистр 21 памяти, где хранилось значение сигнала с цифрового счетчика 20 за прошпый цикл сравнения (В). Во второй регистр 25 памяти записывается уточненное значение управляющего выходного сигнала с этого же второго регистра 25 памяти (С). В трехвходовом сумматоре 22 (2 С + А — В) происходит уточнение кода на величину изменения сигнала ошибки, а в двухвходовом сумматоре 24 (.ЕС + А) — на величину сигнала ошибки. Блок 23 выбора выбирает сигнал с нужного сумматора в конце общего цикла сравнения и подает его на второй регистр 25 памяти.

Точность установки фазы выходного сигнала в предлагаемом устройстве импульсно-фазовой автоподстройки частоты, выполненного по предлагаемому способу, выше чем у известного устройства за счет возможностей более точного измерения разности фаз сигналов.

Формула изобретения

1443173 режимов соединены с управляющими входами первого и второго блоков установки делителя управляющие выходы которых соединены с установочными входами

5 соответственно первого и второго де— лителей с переменным коэффициентом деления, а первый и второй выходы фазового детектора дополнительно соединены соответственно с „Вторыми входа- 1п ми второго и первого блоков установ— ки делителя„ причем каждый блок установки делителя выполнен в виде последовательно соединенных формирователя импульсОВ ВхОды кОтОрогО явля ются входами блока установки делителя, а один из выходов является выходом блока установки делителя,первого дешифратора и элемента памяти, выходы которого являются управляюпдми gg выходами блока установки делителя, при этом управляющими входами блока установки делителя являются первый и второй цифровые входы первого дешифратора, а блок выбора режимов выполнен в виде последовательно соединенных элементов ИЛИ, входы которого являются первым и вторым входами блока выбора режимов, счетчика, второго дешифратора и ячейки памяти, причем входы элемента ИЛИ соединены также с тактовыми входами второго дешифратора, а выход элемента ИЛИ с входом записи ячейки памяти, выходы ячейки памяти и счетчика являются управляющими выходами блока выбора режимов и соединены с управляющими входами второго дешифратора, устано« вочный выход второго дешифратора подключен к входу сброса счетчика в ноль, при этом выходы второго дешифратора "Счетный", "Установка" и "Перезапись" являются выходами блока выбора режимов.

1443173

Таблица

Цифровые входы (Управляющие сиг

12 кте а

000

0110

1010

100

0110

1010

101

0000

1010

100

000 оооо

1010

010

000

1010

1010

101

000

0001 оооо

100

100

0001 оооо!

0110

010

100

О! 10

100

000!

0001

100

010

0010

0010

0001

101

010

0001

100

001

0010

0010

001

001

0110

0»О

101

i 01

В табл.1 при всех остальных видах управляющих сигналов выходные сигналы равны 0000.

Единица в выходном сигнале изменяет состояние триггера запоминания в элементе 13 памяти. Первые два разряда изменяют состояние первого триггера, а вторые два разряда — второго. По сигналу d

)010 на выходе соответствующих триггеров устанавливается 00

0101 на выходе соответствующих триггеров устанавливается

1001 на выходе соответствующих триггеров устанавлив,".ется 01

0110 на выходе соответствующих триггеров устанавливается 10

Знак "-" управляющих сигналов допускает любое значение данного символа (О или 1).

Такты а и в во времени не совпадают.

Знак инверсии 00 обозначает любой сигнал, но не

00, т.е. 10 или 01, или 11.

Сигнал С1 имеет шесть значений — "0" — код 100

"1" — -"- 010

N -2 — -"- 001

N -1 — -"- 101

N — -"- — 11 от 2 — до N --3- код 000

Примеч а ни е: 1

4.

6.

f443173!

О

Таблица 2

Выходные сигналы второго дешифратора 1б

Управ. сигналы при такте в при такте а

1 °

< h e g

h e в

-!1 000

ООО

100 1 .!

i00

010 1 0

001 1 0

000 0 0

000 0 0

011 1 0

000

100

000

ООО

000

ООО

101 011 1 О 0

f00 110 1 О 0

000

f01

100

010!

100 0

100

100

100

-11 010 0 О 1

000

О!О

-11 001 О О

000

00!

011 О О 0 000

110 О 0 1 000

101 О О 1 000

111 О О 0 000

0f1

101

110

101

101

101

1. В табл. 2 приняты те же условия, что заданы в примечании п. 3-6 табл.1.

2. Сигнал d подается на входы D — триггеров запоминания ячейки 17 памяти.

3. Единица на выходах f u h обозначает наличие управляющего сигнала, а "0" его отсутствие.

4. Сигнал 000 на выходе g обозначает отсутствие сигнала установки.По сигналу 100 устанавливается "О", по сигналу 110 — N, 101 — максимальное значение счетчика 15, 010 — "N — !", 001

"Я вЂ” 2" и 011 — минимальное значение счетчика 15.

Примечание:

10! ООО 1 1 1 000

100 ООО О О О 000

010 000 О 0 0 000

000 000 О О 0 000

001 000 О О 0 000

010 101 1 0 0 001

000 100 0 0 0 000

001 100 О О 0 000

101 100 О 0 О 000

-11 111 1 О 0 01f

100 0

100 0

100 0

100 0

100 0

111

010 0

001 0

011 0

110 0

10! 0

111 0

0 000

0 000

0 100

0 110

0 000

0 000

0 101

0 000

0 000

0 000

0 000

0 000

0 011

0 000

0 000

0 000

0 000

0 000

0 000

1443173 бинФониьирующив УюРм

Тактобые &оА

1443173

Переианись

У

У иг. 5

ФМ8. б

Составитель А.Кабанов

Редактор В. Бугренкова Техред Л.Олийнык Корректор Н.Король

Заказ 6396/55

Производственно-полиграфическое предприятие, г, Ужгород, ул. Ilpcектная, 4

lcm

У й

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д, 4/5