Частотный детектор цветного телевизионного приемника системы секам

Иллюстрации

Показать всеРеферат

Изобретение относится к цветному телевидению. Цель изобретения - повьшение устойчивости работы частотного детектора за счет исключения сбоев. Устр-во содержит формирователь 1 квадратурных сигналов, преобразователи 2 и 3 частотной модуляции в частотно-импульсную модуляцию и блок вычисления (БВ) 4 девиации. Из квадратурных сигналов формирователя 1 преобразователи 2 и 3 формируют сигиалы, в которых амгоштуды оказываются пропор19 ональными синусу девиации. Затем БВ 4, работа кбторого основана на итерационном алгоритме, вьщеляет зту амплитуду. Устойчивость работы устрва достигается тем, что в нем отсутствует операция деле(шя на текущее значение сигнала, обусловливаннцая сбой работы в случае, когда делитель принимает нулевые значения. 2 з.п. ф-лы, 3 ил.S

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (Ц) (Ю4 Н 04 N 9/64 щц щ ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ!

Й Уиг!

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО.ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) . 4079076/24-.09 (22) 19.06.86 (46) 07.12.88 Бкл. ((- 45 (72) Б.Н.Хохлов (53) 621 397(088.8) (56) ACTA ELECTP0NICA, 1984, N 3-4, р. 199-207. (54) ЧАСТОТНф1 ДЕТЕКТОР ЦВЕТНОГО ТЕЛЕВИЗИОННОГО. ПРИЕМНИКА СИСТЕИЫ СЕКЛИ (57) Изобретение относится к цветному телевидению. Цель изобретения — повьппение устойчивости работы частотного детектора за счет исключения сбоев. Устр-во содержит формирователь 1 квадратурных сигналов, преобразователи 2 и 3 частотной модуляции в частотйо-импульсную модуляцию и блок вычисления (БВ) 4 девиации. Из квадратурнык сигналов формирователя 1 преобразователи 2 и 3 формируют сигналы, в которых амплитуды оказываются пропорциональными синусу девиации. Затем

БВ 4, работа кбторого основана на итерационном алгоритме, выделяет эту амплитуду. Устойчивость работы устрва достигается тем, что в нем отсутствует операция деления на текущее значение сигнала, обусловливающая сбой работы в случае, когда делитель принимает нулевые значения. 2 з.п. ф-лы, 3 нл.

1443210

Изобретение относится к цветному телевидению, в частности к декодирующим устройствам с цифровой обработкой сигнала.

Цель изобретения — повышение устойчивости работы частотного детектора за счет исключения сбоев.

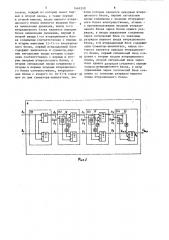

На фиг.1 представлена структурная электрическая схема частотного детектора цветного телевизионного приемника системы СЕКАИ; на фиг.2— схема блока вычисления девиации, на фиг.3 — АЧХ предлагаемого устройства.

Частотный детектор цветного телевизионного приемника системы СЕКЛИ содержит (фиг.1) формирователь квадратурных сигналов, первый преобразователь 2 частотной модуляции (ЧГа) В ЧаСтОтНО-ИМПУЛЬСНУЮ МОДУЛЯ- 20 цию (ЧИИ), второй преобразователь 3

ЧМ и ЧИИ, блок 4 вычисления девиации. Преобразователи 2 и 3 ЧК в ЧИМ содержат регистры 5 и 6 задержки и сумматоры 7 и 8. Формирователь 1 25 квадратурных сигналов может быть выполнен в вице двух последовательно соединенных регистров задержки на такт и вычитателя, входы которого со.единены с входом первого регистра и выходом второго регистра, соединение регистров является первым выходом формирователя квадратурных сигналов, а выход вычитателя — вторым выходом.

Формирователь 1 квадратурных сигналов может быть также выполнен в виде нерекурсивного фильтра, содержащего n последовательно соединенных регистров задержки на такт и два сумматора, выходы которых являются, выхо- 40 дами формирователя. Входы первого сумматора соединены через формирователи весовых коэффициентов (умножители) с выходами нечетных регистров задержки, а выходы второго сумматора через формирователи весовых коэффициентов с выходами четных регистров задержки Блок 4 вычисления девиации может быть выполнен в виде двух квадраторов, сумматора и вычислителя

50 квадратного корня. При этом в качестве квадраторов и вычислителя квадратного корня могут использоваться постоянные запоминающие устройства (ПЗУ). Лучшие результаты дает итерационный блок (фиг.2), который содержит и итерационных блоков 9.1...9.п.

В состав первого блока входят вычитатель 10 и сумматор 11. Блоки со второго по (и-1) -й содержат по два сумматора-вычит теля 12, 13 и 14, 15, логические блоки 16 и 17 и блоки

18-?1 сдвига разрядов. Последний п — и блок содержит только один сумматор-вычитатель 22, логический блок

23 и блок 24 сдвига разрядов. Блоки

18 — 21, 24 осуществляют сдвиг данных в ту или иную сторону на заданное число разрядов. Выполнение логических блоков зависит от особенностей применяемых сумматоров-вычитателей в части входов управления режимом работы (суммирование или вычитание). В простейшем случае блоки

i6, 17 и 23 содержат по одному инвертору 25, 26 и 27.

Частотный детектор работает следующим образом.

Для пояснения работы устройства рассмОтрим дискретизированные ЧИ синусоидальный (У) и косинусоидальный (Х) сигналы. В каждом из сигналов выцеляют по два отсчета с интервалом в два такта

УТ(2) -Asin(2«(fр +ЬЕ) (т ь )), ХТ(2),=Acos t2«(f +hf) (t+ с )j, где c, = 1/4f — период тактового сигнала.

Находят выражения для сумм этих отсчетов: A,= =У! + У2, В = Х1 + Х2.

После преобразований получают: Ар(В,)=

2Азхп(соя) P2» (f + gЕ) tjsin(«/2 и f/f ).

Иодуль этого выражения пропорционален синусу от девиации и с учетом того, что в системе СЕКАИ Ьf fo

Z =/A, е В,= 2Аакп(Т!2 df/f ) ир /А«Ар+ Вр (2)

Таким обпавом, вычисление А Н р р соответствует демодуляции цифрового

ЧИ сигнала. На фиг.3 дано поле допуска I-I для АЧХ аналогового частотного детектора СЕКАИ. График II фиг.3 соответствует выражению (3).Он с большим запасом укладывается в поле допуска. Если необходима более высокая линейность АЧХ, то после определения модуля производится вычисление функции F=arcsin(Z/2А) с помощью ПЗУ. Тогда АЧХ становится строго линейной (график III фиг.3).

14432

Формирователь 1 квадратурных сигналов дает на выходах сигналы У и Х.

В преобразователях 2 и 3 ЧМ и ЧИК производится сложение с помощью суммато- 5 ров 7 и 8, сдвинутых в регистрах

5 и 6 на два такта отсчетов. При этом формируются сигналы А0 и Во, в которых амплитуды оказываются пропорциональными синусу девиации. 1С

Блок 4 выделяет амплитуду сигнала, пропорциональную синусу девиации:

Z2 = 2Asin(s/2 М/f ).

Работа блока 4 основана на итера- 15 ционном алгоритме;

А;,=А; -(2 В;, где, = 1 ив1у =Big@ А; „

«озффипиент 1, показывает, н каком режиме должны работать сумматоры-вычитатели данного итерационного блока.

Если А; 7 О, то (; = 1. Тогда А;, вычисляется вычитанием, а В;, суммированием. При A, 0 действия меняются на обратные. На выходе сумматоравычитателя 22 последнего итерационного блока 9.п формируется значение 30

2 = K À е В, пропориионапнное синусу девиации.

Устойчивость работы частотного де тектора достигается благодаря тому, что в нем отсутствует операция деления на текущее значение сигнала,обуславливающая сбои работы в случае, когда делитель принимает нулевые значения. Выражение (3) становится равным нулю только в том случае, когда одновременно А,= 0 и В = О, т.е, когда девиация частоты сигнала равна нулю. При этом сбои в работе устройства также не возникают.

Пример (фиг.2) . Пусть А0

0,3421 B,= 0,939, П = 20 и А*, е B1= 1..

На выходе первого итерационного блока 9.1,получают A< = — 0 597 и

В, = 1,281. А,(О, значит Я1р А,.= 1 и Р = -1.Сигналы А, и В< поступа21 ют на основные входы второго итерационного блока 9.2. Знаковый разряд A1(si n А<-1) проходит на вход управления сумматора-вычитателя 12 непосредственно, обеспечивая режим суммирования, и.через инвертор 25 на вход управления сумматора-вычитателя 13, обеспечивая режим вычитания, 1О

На выходах блока 12 получают:

A = 0,0435, В = 1,5795 Si)n А = 0

Сигналы А, В и Gi)23 А поступают на входы третьего итерационного блока 9,3, который формирует сигналы

А» В и 511)н А, и т.д. Проведя вычисления, получают:

А = -0,3513, В = 1,5903, = -1

А = — 0,1525, ВА= 1,6342, (= -1

А = -О, 0503,. B = 1,6437, = — 1

Аб= -0,001, В = 1,6452, 6 = 1

А = -0,0015, В = 1,645215, (= -1 и так далее.

Из результатов вычислений видно, что уже после четырех ступеней итерации приращение В; становится менее

1Х стремится к значению близкому к 1,645, поэтому А, + В

В1

1, 645

Формула изобретения

1. Частотный детектор цветного телевизионного приемника системы

СЕКАИ, содержащий формирователь квадратурных сигналов, вход которого является входом устройства, о т л ич а ю шийся тем, что, с целью повышения устойчивости работы частотного детектора за счет исключения сбоев, введены первый и второй преобразователи частотной модуляции в частотно-импульсную модуляцию и блок вычисления девиащж, выход которого является выходом устройства, а входы соединены через преобразователи частотной модуляции в частотно-импульсную модуляцию с выходами формирователя квадратурных сигналов.

2. Детектор ло п.1, о т л и ч аю шийся тем, что каждый из преобразователей частотной модуляции в частотно-импульсную модуляцию выполнен в виде сумматора, первый вход которого соединен с входом преобразователя частотной модуляции в частотно-импульсную модуляцию непосредственно, а второй — через регистр задержки.

3. Детектор по п. 1, о т л и ч а юшийся тем, что блок вычисления девиации состоит из и итерационных

5 14432 волоков, каждый из которых имеет первый и второй входы, а также первый и второй выходы, входы первого итерационного блока являются входами бло5 ка вычисления девиации, выход n-ro итерационного блока является выходом блока вычисления девиации, первый и второй входы i-ro итерационного блока соединены соответственно с первым !О и вторым выходами (i-1)-;"о итерационного блока, первый итерационный блок содержит вычитатель и сумматор,первые сигнальные входы которых соединены соответственно с первым и вто- 15 рым входами итера данного блока, а вторые сигнальные входы соединены с вторым и первым входами итерационного блока соответственно, итерационные блоки с второго по (n-1)-й содер- 20 жат по два сумматора-вычитателя, вы10 ходы которых являются выходами итерационного блока, первые сигнальные входы соединены с входами итерационного блока непосредственно, вторые— с противоположными входами итерационного блока через блоки сдвига разрядов, а входы управления соединены через логический блок со знаковым разрядом первого входа итерационного блока, п-й итерационный блок содержит один сумматор-вычитатель, выход которого является выходом итерационного блока, первый сигнальный вход соединен с вторым входом итерационного блока, второй сигнальный вход через блок сдвига разрядов соединен с первым входом, итерационного блока, а вход управления через логический блок соединен со знаковым разрядом первого входа итерационного блока.

3443210

Составитель Г.Росаткевич

ТехРед Л,Олийнык Корректор H.Максимишинец

Редактор Л.Зайцева

Подписное

Тираж 660

Заказ 6398/56

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4