Устройство для измерения амплитуды синусоидального напряжения

Иллюстрации

Показать всеРеферат

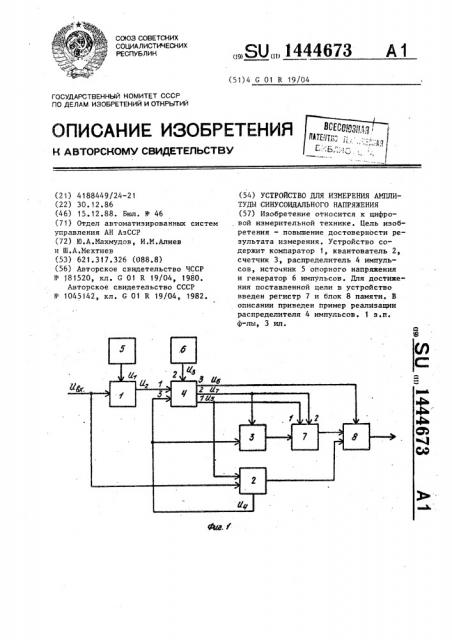

Изобретение относится к цифро- . вой измерительной технике. Цель изобретения - повышение достоверности результата измерения. Устройство содержит компаратор 1, квантователь 2, счетчик 3, распределитель 4 импульсов , источник 5 опорного напряжения и генератор 6 импульсов. Для достижения поставленной цели в устройство введен регистр 7 и блок 8 памяти. В описании приведен пример реализации распределителя 4 импульсов. 1 з.п. ф-лы, 3 ил. с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 01 R 19/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И д ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4188449/24-21 (22) 30.12.86 (46) 15.12.88. Вюл. № 46 (71) Отдел автоматизированных систем управления АН АЗССР (72) Ю.А.Махмудов, И.М Алиев н Ш.А.Мехтиев (53) 621.317.326 (088.8) (56) Авторское свидетельство ЧССР № 181520, кл. G 01 R 19/04, 1980.

Авторское свидетельство СССР № 1045142, кл. С 01 R 19/04, 1982.

„„SU„„1444673 А 1 (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ СИНУСОИДАЛЬНОГО НАПРЯЖЕНИЯ (57) Изобретение относится к цифро, вой измерительной технике. Цель изобретения — повышение достоверности результата измерения. Устройство содержит компаратор 1, квантователь 2, счетчик 3, распределитель 4 импульсов, источник 5 огорного напряжения и генератор 6 импульсов. Для достижения поставленной цели в устройство введен регистр 7 и блок 8 памяти. В описании приведен пример реализации распределителя 4 импульсов. 1 з.п. ф-лы, 3 ил.

1444673

Изобретение относится к цифровой измерительной технике и может быть использовано при создании приборов для регистрации амплитуды синусои5 дального напряжения низкой и инфранизкой частоты.

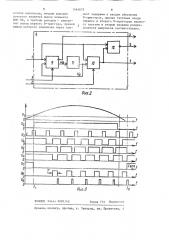

Цель изобретения — повышение достоверности результата измерения, На фиг.1 представлена блок-схема 10 предлагаемого устройства, на фиг.2 распределитель импульсов; на фиг.3 временные диаграммы работы устройства, Устройство для измерения амплитуды 15 синусоидального напряжения содержит подключенные к входной шине компаратор 1 и квантователь 2, счетчик 3, управляющий вход которого подключен к первому выходу распределителя 4 им- 20 пульсов, первым входом подключенного к выходу компаратора 1, опорный вход которого подключен к выходу источника 5 опорного напряжения, генератор

6 импульсов, регистр 7, йодключенный входом к выходу счетчика 3, блок 8 памяти, выход которого является выходом устройства, причем первый управляющий вход регистра 7 и управляющий вход квантователя 2 подключены к первому выходу распределителя 4 импульсов, второй выход которого подключен к входу обнуления счетчика 3 и к второму управляющему входу регистра 7, выход которого подключен к адресному входу блока 8 памяти, управляющий вход которого подключен к третьему выходу распределителя 4 импульсов, BT opbtM входом подключен ного к выходу генератора 6 импульсов, 40 а третьим входом совместно с счетным входом счетчика 3 — к управляющему выходу квантователя 2, информационный выход которого подключен к информационному входу блока 8 памяти. 45

Распределитель 4 импульсов состоит из первого 9 и второго 10 D-триггеров, элемента 11 задержки и элемента

ИЛИ-НЕ 12, первый вход которого совместно с D-входами триггеров являет- 50 ся первым входом распределителя 4 импульсов, а второй соединен с прямым выходом второго 10 D-триггера, являющимся первым выходом распределителя

4 импульсов, вторым выходом которого 55 является выход элемента ИЛИ-HE 12, а третьим выходом — инверсный выход первого 9 D-триггера, прямой выход которого подключен через элемент 11 задержки к входам обнуления D-триггеров, причем тактовые входы первого и второго 9 и 10 D-триггеров являются третьим и вторым входами распределителя 4 импульсов соответственно.

Устройство работает следующим образом.

Измеряемое напряжение одновременно подается на входы компаратора 1 и квантователя 2. При достижении входным напряжением 0 „ некоторого порогового уровня напряжения U, устанавливаемого при помощи источника 5 опорного напряжения, на выходе компаратора 1 устанавливается напряжение Q высокого уровня. Напряжение

U высокого уровня сохраняется до тех пор, пока входное напряжение U „ остается больше U а затем вновь переключается на низкий уровень.

Напряжение U< с выхода компаратора 1 поступает на первый вход распределителя 4 импульсов, где. разветвляется на D-входы первого 9 и второго

10 D-триггеров и на первый вход элемента -HJIH-НЕ 12. D-триггеры управляются фронтом импульса на их тактовых входах. При наличии напряжения

U высокого уровня и по фронту импульса U с выхода генератора 6 импульсов, который действует на второй вход распределителя 4 импульсов (т.е. на тактовый вход второго 10

В-триггера), второй 10 D-триггер устанавливается в единичное состояние.

По фронту импульса Б с прямого выхода этого В-триггера, прямой выход которого является и первым вы,ходом распределителя 4 импульсов, параллельно происходят: запуск квантователя и загрузка содержимого счетчика 3 в регистр 7. Напряжение U

**;a управляющем выходе квантователя 2 изменяется в следующей последовательности: по сигналу запуска напряжение

U с высокого уровня переходит на низкий и. остается на низком уровне в течение одного преобразования. По окончании преобразования в квантователе 2 указанное напряжение вновь переключается на высокий уровень, свидетельствуя о готовности результата измерения на информационном BBI ходе квантователя 2. По фронту U,, который одновременно поступает на

1444673

20 жается в регистр 7 . снова запускает- 30

45 ля 4 импульсов. По фронту этого напряжения содержимое регистра 7 сдви- . В0

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что распределитель импульсов содержит первый и второй D-триггеры, элемент задержки и элемент ИЛИ-НЕ, первый вход которого совместно с D-входами триггеров является первым входом распределителя импульсов, а второй вход соединен, с прямым выходом второго D-триггера„ являющимся первым вьжодом распредесчетный вход счетчика 3 и второй вход распределителя 4 импульсов, содержимое счетчика 3 увеличивается на единицу, а первый 9 D- òðèããåð распределителя переключается в единичное состояние. Тогда низкий уровень напряжения U с инверсного выхода первого 9

D-триггера, являющегося третьим выходом распределителя 4 импульсов, поступая на управляющий вход блока 8 памяти, инициирует в последнем процесс записи результата измерения с информационного выхода квантователя

2 в блок 8 по адресу из регистра 7.

Высокий уровень напряжения U с пря9 мого выхода первого 9 D-триггера соединенного через элемент 11 задержки с входами обнуления D-триггеров, устанавливает их в нулевое состояние.

Таким образом на управляющем входе блока 8 низкий уровень напряжения

U записи по длительности равен задержке i . Далее до следующего фронта импульса U с выхода генератора 6 устройство находится в режиме ожидания. С приходом очередного фронта увеличенное в предыдущем такте на единицу содержимое счетчика 3 загруся квантователь 2. Регистр 7 таким образом будет адресовать следующую незанятую ячейку блока 8. По окончании преобразования текущее измеренное значение входного напряжения записывается в адресуемую регистром 7 ячейку блока 8. Эти операции повторяются до тех пор, пока входное напряжение больше напряжения U и на выходе компаратора 1 сохраняется высокий уровень напряжения U . Если же на выходе компаратора 1 устанавливается низкий уровень, а в устройстве окончены очередное преобразование и запись в блок 8, тогда высокий уровень напряжения U появится на выходе элемента ИЛИ-НЬ 12, который является и вторым выходом распределитегается на один разряд вправо, а счет чик 3 устанавливается в нулевое состояние. По прошествии и преобразований и записей в блок 8 и одного сдвига вправо в регистре 7 будет число и ° и

2 которое будет адресовать — — ую

2 ячейку блока 8, в котором хранится значение измеренного синусоидального напряжения, соответствующего моменту времени, когда измеряемое напряжение достигало своего максимального значения. Высокий уровень напряжения U на управляющем входе блока 8 иницииП рует по адресу — чтение из блока 8

2 максимального, т.е. амплитудного значения либо суммарного значения постоянной составляющей и амплитуды синусоидального напряжения, соответствующего указанному полупериоду.

Формула изобретения

1. Устройство для измерения амплитуды синусоидального напряжения, содержащее подключенные к входу устройства комнаратор и квантователь, счетчик, распределитель импульсов, первым входом подключенный к выходу компаратора, опорный вход которого подключен к выходу источника опорного напряжения, и генератор импульсов, о т л и ч а ю щ е е с я тем, что, с целью повьппения достоверности результата измерений, в него введены регистр, подключенньп входом к выходу счетчика, и блок памяти, выход которого является выходом устройства, причем первый управляющий вход регистра и управляющий вход квантователя подключены к первому выходу распределителя импульсов, второй выход которого подключен к входу обнуления счетчика и к второму управляющему входу регистра, выход которого подключен к адресному входу блока памяти, управляющий вход которого подключен к третьему выходу распределителя импульсов„ вторым входом подключенного к выходу генератора импульсов, а третьим входом совместно со счетным входом счетчика — к управляющему выходу квантователя, информационный выход которого подключей к информационному входу блока памяти.

i444673

ВНУШИ Заказ 6501!43

Тираж 772 Подписное

Произв.-полигр. пр-тие, r. Ужгород, ул. Проектная, лителя импульсов, втОрым ВЫХОдом которого является выход элемента

ИЛ 1--НЕ, а третьж1 вьгходом — инверсный выход первого D-григгера, прямой выход которого подключен через элемент задержки к входам обнуления

D-триггеров, причем тактовые входы первого и второго D-триггеров являют= ся третьим и вторым входами распределителя импульсов соответственно,