Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для вычисления сложньпс математических функций в быстродействующих специализированных процессорах во многих Ьбластях народного хозяйства . Целью изобретения является расширение области применения за счет дополнительной возможности воспроизведения монотонно возрастающих четных и нечетных функций. Цифровой функциональный преобразователь состоит из регистров младших и старших разрядов аргумента, триггера знакового разряда аргумента, блока памяти коэффициентов, блока памяти опорных значений функции, пяти коммутаторов, умножителя, двух сумматоров, двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двух элементов И. 1 ил. 1 табл. о (Л

СОЮЗ СОВЕТСНИХ

СООИАЛИСТИЧЕСНИХ

РЕСПУБЛИН д 11 4 G 06 F 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИЯ с е

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4274516/24-24 (22) 01. 07. 87 (46) 15.12.88. Бюл. К 46 (71) Институт проблем моделирования в энергетике АН УССР (72) М.В. Синьков, В,И.Ц1ербаков и А.В. Савчук (53) 681.325(088.8) (56) Авторское свидетельство СССР

N- 1027732, кл. G 06 F 7/544, 1982.

Авторское свидетельство СССР

Р 1361547, кл. G 06 F 7/544, 1987. (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЬЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к области вычислительной техники и может быть использовано для вычисления сложных

„.SU,„, 1444758 А 1 математических функций в быстродействующих специализированных процессорах во многих Ьбластях народного хозяйства. Целью изобретения является расширение области применения за счет дополнительной возможности воспроизведения монотонно возрастающих четных и нечетных функций. Цифровой функциональный преобразователь состоит из регистров младших и старших разрядов аргумента, триггера знакового разряда аргумента, блока памяти коэффициентов, блока памяти опорных значений функции, пяти коммутаторов, умножителя, двух сумматоров, двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двух элементов И. 1 ил.

1 табл.

Изобретение относится к вычислительной технике и может быть использовано для вычисления сложных математических функций в быстродействующих специализированных процессорах.

Цель изобретения — расширение области применения цифрового функционального преобразователя за счет дополнительного воспроизведения монотонно возрастающих четных и нечетньм функций.

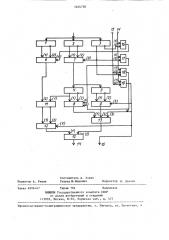

На чертеже изображена блок-схема цифрового функционального преобразователя. 15

Цифровой функциональный преобразователь содержит регистр 1 младших разрядов аргумента, регистр 2 старших разрядов аргумента, триггер 3 знака блока 4 памяти коэффициентов и блока 20

5 памяти опорных значений функции, коммутаторы 6-10, умножитель 11, два сумматора 12 и 13, вход 14 задания убывающе-возрастающей функции, вход

15 задания четной-нечетной функции25 два элемента ИСКЛЮЧАКЩЕЕ ИЛИ 16 и 17 и два элемента И 18 и 19.

Алгоритм работы цифрового функционального преобразователя следующий:

30 т;;(Х) = y, Е т;(Х,,.}ау. О 4"К ;(Х„, )+

W 9 (g hK )+7o Л hy + Wtt hy где Хст = Хо .® Хст

f

Хмл т- Р ® Хна;;, р(Х, „,,5 К, X ...; х х °

Х вЂ” знак аргумента;

Ь вЂ” вес единицы младшего разряда

fi операнда;

К вЂ .коэффициент наклона;

Ъ, и i — индексы соответственно номера опорного значения и точки между опорными значения- 45 миу у, — знак функции, W — коньюнкция от значений, сигналов на входе 14, входе 15 и Х у

50 — сумма по модулю два сигнала на входе 14 и Х

P — сумма по модулю два сигналов на входе 14 и Х„.

Цифровой функциональный преобразователь работает следующим. образом.

С помощью внешних сигналов, указывающих на вид воспроизводимой функции, а также значения знакового разряда

8 2

Ф аргумента в логических элементах И 19 и 18 и двух логических элементах ИСКЛЮЧАКЩЕЕ ИЛИ 16 и 17 производится формирование управляющих сигналов, которые поступают на управляющие входы коммутаторов 6, 8, 9 и 10 и обеспечивают вычисленные функции по заданному алгоритму.

Алгоритм работы цифрового функционального преобразователя приведен в таблице.

Формула изобретения

Цифровой функциональный преобразователь, содержащий регистр младших разрядов аргумента, регистр старших разрядов. аргумента, триггер знака, пять коммутаторов, блок памяти коэффициентов, блок памяти опорных значений функции, умножитель и первый сумматор, причем вход аргумента устройства соединен с информационными входами регистров младших и старших разрядов, вход знака аргумента устройства соединен с установочным входом триггера знака, прямой выход которого соединен с управляющим входом первого коммутатора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходами регистра старших разрядов аргумента, прямой и инверсный выходы регистра младших разрядов аргумента соединены соответственно с первым и вторым информационными входами второго коммутатора, выход которого соединен с входом первого сомножителя умножителя, второй вход которого соединен с прямым выходом блока памяти коэффициентов и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с инверсным выходом блока памяти коэффициентов, адресный вход которого соединен с выходом первого коммутатора и адресным входом блока памяти опорных значений функции, прямой и инверсный выходы которого соединены соответственно с первым и вторым информационными входами четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены с входами соответственно первого и второго слагаемых первого сумматора, прямой и инверсный выходы умножителя соединены соответственно с первым и вторым входами пятого коммутатора, о т л и ч аВход Вход Х Х Алгоритм работы

14 15

Вид функции

О О О

О О 1

2 C

К Р

Ж о ) О 1 О

0 1 1 хы))с хх) о )

8 I Е о ) e х ос))e Н) х

cd

1 I

О lg 1

6) Cd 9. Ж о к а>

Ф Х Ь

:Т о ы х х

Ж > I cd о.В I

Е I Е" ок)э о о 1 к,, (х) =.Y (õ„) + л;, (x ) ,)

Y.. (X) т Y (Х, .) + )т;;(Х„„,) +К.

-J1 ст ) 31 МЛ!1

0 1 К,, (Х) = Y. (Х,„.) + ;;(Х„,,.)

11107..(Х)=71(Х.)+aY-,.(Х„..)+К1+ЭЬУ р мл; з 14447 ю шийся тем, что, с целью расширения области применения за счет дополнительного воспроизведения монотонно возрастающих четных и нечетных функций,,в него введены два элемента

ИСКЛЮЧАКИ1ЕЕ ИЛИ, два элемента И и второй сумматор, причем вход задания четной-нечетной функции устройства соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с прямым выходом триггера знака, инверсный выход которого соединен с первым входом первого элемента ИСКЛ10ЧАЮЩЕЕ КЧИ,. второй вход которого соединен с входом задания убывающе-возрастающей функции устройства, третьим входом первого элемента И и первым входом второго элемента ИСКЛЮЧАКЩЕЕ ИЛИ, второй вход которого соединен с прямым входом триггера знака, выход первого

58

4 элемента ИСКЛЮЧАКЩЕЕ ИЛИ соединен с управляющим входом второго коммутатора, выход второго. элемента ИСКЛЮЧАНЦЕЕ ИЛИ соединен с входом разрешения выдачи третьего коммутатора, управляющий вход которого соединен с выходом первого элемента И, выход второго элемента И соединен с управляющимк входами четвертого и пятого коммутаторов, выходы первого и второго элементов И соединены с входом третьего слагаемого первого сумматора, выход которого соединен с входом первого слагаемого второго сумматора, вход -второго слагаемого которого соединен с выходом пятого коммутатора, выход второго сумматора соединен с выходом значения функции устройства, выход знака функции которого соединен с выходом второго элемента И.

Y..(X)=7 „(Х,т )+ JI YJ (Х„,л.;)+К) Y1, (X) Y1 i(Хст ° )+ d Yji (Х л")+KI (Х) YJ 1(X ст ° )+ I1YyI (ХМл )+h у

1444758

Составитель А. Зорин

Техред М.Ходанич Корректор М. Демчик Редактор А. Ревин

Заказ 6506/47

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4