Устройство поклеточного умножения матриц

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для ум11ожега1я матриц и подматриц. Целью изобрете шя является расширение функциональных возможностей за счет возможности вычисления произведений клеточных подматриц . Устройство содержит сдвиговые регистры 1, блоки 2 вычисления скалярного произведения векторов, блок 3 управления, информационные вxo.vы 4, 5, 6 устройства, выходы 7, 8, 9 блока управления, вход 10 начальной установки устройства, Поставленггая цель достигается введением новых элементов и связей. 2 ил. Ё

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 G 06 F 15/347

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР . ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 4167114/24-24 (22) 22.12.86 (46) 15.12.88. Бюп. У 46 (71) Институт кибернетики йм. В.М.Глушкова (72) В.А.Вышинский, З.Л.Рабинович, Б.N.Òèõîíîâ и Н.Б.Фесенко (53) 681.32(088.8) (56) Авторское свидетельство СССР

Р 647687, кл. 0 06 Г 15/347, 1976.

Прангишвили И.В. и др. Микропроцессорные системы. — M. Наука, 1980, рис.11.35. (54) УСТРОЙСТВО ПОИ1ЕТОЧНОГО УМНОЖЕИИИ МАТРИЦ (57) Изобретение относится к области вычислительной техники и может быть использовано для умножения матриц и подматриц. Цельи изобретения является расширение функциональных возможностей за счет возможности вычисления произведений клеточных подматриц. Устройство содержит сдвпговые регистры 1, блоки 2 вычисления скалярного произведения векторов, блок

3 управления, информационные входы

4, 5, 6 устройства, выходы 7, 8, 9 блока управления, вход 10 начальной установки устройства. Поставленная C цель достигается введением новых элементов и связей. 2 ил.

1444819

Изобретение относится к вычислиельной технике и может быть использовано для умножения матриц и подматриц.

Целью изобретения является расширение функциональных возможностей за счет возможности вычисления нроизведения клеточных подматриц.

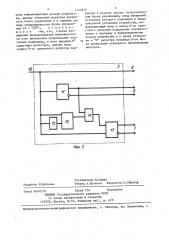

На фиг.l изображена функциональ- 10 ная схема устройства; на фиг.2— функциональная схема блока управления.

Устройство содержит сдвиговые регистры 1, блоки 2 вычисления скалярного произведения векторов, блок

3 управления, информационные входы

4-6 устройства, выходы 7-9 блока управления, вход 10 начальной уста-,, новки устройства, генератор 11 син- 2О хроимпульсов, триггер 12, элемент HE

13, элемент И 14, счетчик 15 по модулю М.

Устройство в процессе работы умножает матрицы с различными размерами 25 клеток. Каждому размеру клеток соответствует своя управляющая числовая матрица, которая перед началом работы устройства записывается через вход 4 устройства в регистры 1. 30

Для обычного умножения матриц значение числовой управляющей матрицы равно нулю. В данном случае раз-. мер клетки равен размерности матрицы

M. В соответствии с числовой управ-. .ляющей матрицей, во все разряды сдви35 говых регистров 1 записываются нулевые значения.

Для случая, отличного от обычного умножения матриц, числовая управляю- 4 щая матрица содержит информацию, соответствукпцую предстоящему вычислительному процессу. Каждая числовая управляющая матрица соответствует заданному размеру .клеток-сомножите- 45 лей. При этом информация числовой управляющей матрицы указывает, в каком такте в ходе вычислительного про-, цесса какой блок 2 необходимо отключить. При этом такт работы предлагаемого устройства соответствует времени накопления в блоке 2 очередного частичного произведения.

Предлагаемое устройство выполняет поклеточное умножение матриц за M тактов работы.

Б исходном состоянии в сдвиговые регистры 1 записана управляющая информация в виде числовой матрицы, соответствующей предстоящему вычислительному процессу умножения клеточных матриц требуемой размерности.

Устройство поклеточного умножения матриц работает следующим образом.

С входа 10 устройства в блок 3 управления поступает сигнал "Начало работы", который запускает генератор

11 синхронмпульсов, устанавливает в единичное состояние триггер 12 и устанавливает в нулевое состояние счетчик 15.

Сигнал "Начало работы" поступает также на выход 8 блока 3 управления, откуда передается для обнуления результата блоков 2. Генератор ll синхроимпульсов вырабатывает управляющие синхроимпульсы, которые с выхода

9 блока 3 управления подаются на сннхровходы блоков 2.

Сдвиговые регистры 1 под действием синхросигналов с выхода счетчика

15 осуществляют сдвиг записанной: в них управляющей информации на один разряд в сторону старших разрядов.

Прн наличии единицы в старшем разряде сдвигового регистра 1.1 единичный сигнал поступает на вход обнуления операнда соответствующего К-го блока 2. Под действием этого сигнала производится отключение К-го блока 2 из процесса обработки исходной информации. В этом такте, например, происходит установка в нуль регистра одного из операндов.

При наличии в старшем разряде сдвигового регистра 1 на вход соответствующего бл ка 2 сигнал отключения не поступает. При этом К-й блок обрабатывает исходную информацию, поступающую на ее первый и второй информационный входы.

По окончании M тактов работы устройства в блоках 2 находится результат операции поклеточного умножения матриц.

Формула изобретения

Устройство поклеточного умножения матриц, содержащее M блоков вычис2 ления скалярного произведения векторов, где M — размерность матрицы, причем первый и второй информационные входы, вход установки в "0" регистра результата и синхровход К го блока вычисления сумм произведений подключены соответственно к первому и втоСоставитель М,Силин

Техред А. Кравчук Корректор А.Обручар

Редактор М;Циткина

Заказ 6508/50 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

i13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

l44481 рому информационным входам устройства, выходу обнуления регистра результата блока управления и к первому выходу синхроимпульсов блока управле5 ния(К=1M)отличаю— щ е е с я тем, что, с целью расширения функциональных возможностей за счет вычисления произведения клеа точных подматриц, в него введены M 10 сдвиговых регистров, причем вход сдвига К-го сдвигового регистра под"

4 ключен к второму выходу сннхронмпульсов блока управления, вход начальной установки которого подключен к входу начальной установки устройства, информационный вход и выход К-ro сдвигового регистра подключены соответственно к третьему и информационному входам устройства и к входу установки в "0" регистра операнда К-ro блока вычисления скалярного произведения векторов.