Устройство для записи информации в полупроводниковые блоки постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для записи (программирования) информации в полупроводниковые Злоки постоянной памяти (микросхемы ППЗУ) и контроля этих блоков в динамических режимах и при изменении импульсного питания. Целью изобретения является повьшение достоверности контроля . Устройство содержит блок 1 внешних носителей, блок 2 управления блоком 1, блок 3 синхронизации, пульт 4 управления, пять мультиплексоров 5, 9, 10, 12 и 13, регистр 6 информации , регистр 7 адреса, блок 8 оперативной памяти, регистр 11 разрядов, блок 14 сравнения, адресный формирователь 16, формирователь 17 импульсной записи, амплитудный дискриминатор 18, формирователь 20 управляющих импульсов, счетчик 21 режимов контроля , дешифратор 22 режимов контроля, три формирователя 23-25 одиночного импульса, три источника 26-28 питания , три ключевых элемента 29-31, элемент ИЛИ 32 и буферный регистр 33 числа. Повьшение достоверности контроля достигается путем обеспечения дополнительно девяти динамических режимов контроля, т.е. контроля при минимальных, номинальных и максималь - ных значениях времени обращения и импульсного питания ППЗУ. 2 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 11 С 7/00, 29/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ -И ДBTOPCHOMV СВИДЕТЕЛЬСТВУ

f (61) 826416 (21) 4196204/24-24 (22) 16.02.87 (46) 15.12.88, Бюл. N- 46 72) А.В.Изюмов, Л.А.Лямина, С.E.Íèêîëàåâ, О.В.Росницкий и Д.В.Чабров (53) 681.327(088.8) (56) Авторское свидетельство СССР

11- 826416, кл. G 11 С 7/00, С 11 С 29/00, 1981. (54) УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В ПОЛУПРОВОДНИКОВЫЕ БЛОКИ ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для записи (программирования) информации в полупроводниковые блоки постоянной памяти (микросхемы

ППЗУ) и контроля этих блоков в динамических режимах и при изменении импульсного питания. Целью изобретения является повышение достоверности кон„„SU„„1444882 А 2 троля. Устройство содержит блок 1 внешних носителей, блок 2 управления блоком 1, блок 3 синхронизации, пульт

4 управления, пять мультиплексоров

5, 9, 10, 12 и 13, регистр 6 информации, регистр 7 адреса, блок 8 оперативной памяти, регистр 11 разрядов, блок 14 сравнения, адресный формирователь 16, формирователь 17 импульсной записи, амплитудный дискриминатор !8, формирователь 20 управляющих импульсов, счетчик 21 режимов контроля, дешифратор 22 режимов контроля, три формирователя 23-25 одиночного импульса, три источника 26-28 питания, три ключевых элемента 29-31, элемент ИЛИ 32 и буферный регистр 33 числа. Повышение достоверности контроля достигается путем обеспечения дополнительно девяти динамических режимов контроля, т.е. контроля при минимальных, номинальных и максималь ных значениях времени обращения и импульсного питания ППЗУ. 2 ил.

1444882

0000

0001

0010

0011

Изобретение относится к вычислигел ной технике, может использоваться для записи (программирования) информации в полупроводниковые блоки постоянной памяти (микросхемы ППЗУ) и контроля этих блоков и является усовершенствованием устройства по авт.св. Ф 826416.

Целью изобретения является повышение достоверности контроля.

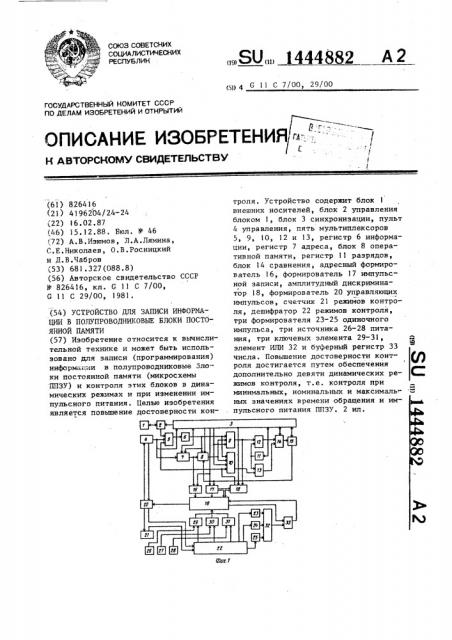

На фиг.! представлена функциональная схема предлагаемого устройства; на фиг.2 — временные диаграммы, поясняющие работу устройства. 15

Устройство содержит блок 1 внешних носителей, блок 2 управления блоком внешних носителей, блок 3 синхро-, низации, пульт 4 управления, первый мультиплексор 5, регистр 6 информа- 20 цин, регистр 7 адреса, блок 8 оперативной памяти, четвертый 9 и пятый

10 мультиплексоры, регистр !1 разрядов,,второй 12 и третий 13 мультиплексоры, блок 14 сравнения, програм- 25 мируемый генератор 15, адресный формирователь 16, формирователь 17 импульсов записи, амплитудный дискриминатор 18, узел 19 фиксации положения контролируемого блока памяти, фор-30 мирователь 20 управляющих импульсов, счетчик 21 режимов контроля, дешифратор 22 режимов контроля, с первого по третий формирователи 23-25 одиночных импульсов, с первого по третий источники 26-28 питания, с первого по третий управляемые ключевые элементы

29-31, элемент ИЛИ 32 и буферный регистр 33 числа.

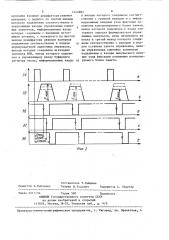

На фиг.2 показаны импульсы 34 запуска формирователя 20, импульсы 35 напряжения E„ „ñ E нам и Eìì ния, импульсы 36, 37, 38 динамического контроля соответственно на выходах4 формирователей 23, 24, 25 и обозначены соответственно минимальная г. „н, номинальная t « и максимальная мц кс длительность времени выборки в режиме динамического контроля.

Формирователь 20 может быть выполнен на микросхеме К583ВГ1, счетчик

21 — на микросхеме К155ИЕ7, дешифратор 22 — на микросхеме К155ИЕ7, формирователи 23, 24, 25 — на микросхемах К155АГ1, источники 26, 27, 28 . -55 тания — на микросхемах К142ЕН5Б.

Устройство работает следующим образом.

В устройстве предусмотрены следующие режимы работы: входной контроль, при котором проверяется отсутствие дефектов в неэапрограммированных или информационное содержимое ранее запрограммированных блоков постоянной памяти (микросхем ППЗУ); ввод информации, при котором исходная информация, подлежащая записи в микросхему

ППЗУ, может вводиться в блок 8, например через клавиатуру пульта 4 с перфоленты, с магнитной ленты, иэ ЭВМ или иэ эталонной микросхемы ППЗУ, устанавливаемой в узел 19, программирование, т.е.запись информации в кон" тролируемый блок постоянной памяти; выходной контроль, при котором проверяется информация, записанная в микросхему ППЗУ, на соответствие исходной информации (в режимах с первого по четвертый устройство работает аналогично известному устройству); динамические режимы контроля, при которых проверяется информация, считан-" ная из контролируемой микросхемь!ППЗУ при трех режимах выборки (с минимальным, номинальным и максимальным spe менем выборки, задаваемым формирователями 23, 24, 25) и при трех режимах импульсного питания, задаваемых ис-, точниками ° 26-28, — минимальном, номинальном и максимальном значениях напряжения питания, т.е. в девяти режимах динамического контроля;

Код счетчика Режим контроля

Контроль при минималь" ном значении питающего напряжения и минимальном времени выборки ин формации

Контроль при минимальном значении питающего, напряжения и номинальном времени выборки информации

Контроль при минимальном значении питающего напряжения и максималь. ном времени выборки ин" формации

Контроль при номиналь" ном значении питающего напряжения и минимальном времени выбрки информации з, 144

Контроль при номинальном значении питающего напряжения и номинальном времени выборки информации

Ol 00

0l О1

0110

0111

1ООО

Устройство для записи информации в полупроводниковые блоки постоянной памяти по авт.св. Р 826416, о т л и" ч а ю щ е е с я тем, что, с целью повышения достоверности контроля за" писи информации в полупроводниковые

46 блоки постоянной памяти, в него введены формирователь управляющих импульсов, счетчик режима контроля, дешифратор режимов контроля, с первого по третий формирователи одиночных импульсов, с первого по третий источники питания, с первого по третий управляемые ключевые элементы, элемент

ИЛИ и буферный регистр числа, причем первый и второй выходы формирователя управляющих импульсов подключены соответственно к управляющему входу дешифратора режимов контроля и к счетному входу счетчика режимов контроля, выходы которого соединены с информаКонтроль при номинальном значении питающего напряжения и максимальном времени выборки информации

Контроль при максимальном значении питающего напряжения и Минималь» ном времени выборки информации

Контроль при максимальном значении питающего напряжения и номинальном времени выборки информации

Контроль при максимальном значении питающего напряжения и максимальном времени выборки информации

Рассмотрим работу устройства в режимах динамического контроля. По сигналу с пульта 4 выбирается режим контроля, запускается счет адресов в регистре 7 и по сигналу с выхода пульта 4, поступающему на вход формирователя 20, обнуляется счетчик 21. Счетчик 21 обеспечивает последовательный перебор всех девяти режимов динамического контроля.

Код адреса с регистра 7 через формирователь 16 подается на проверяемую микросхему ППЗУ, и происходит контроль микросхемы ППЗУ в первом динамическом режиме, при этом работают источник 26 питания, ключевой элемент

29 и формирователь 23, обеспечивающие минимальные значения напряжения питания и времени выборки. Считанная информация с выходов регистра 33 поступает через узел 19 на входы дискриминатора 18, где сравнивается с пороговым значением информации. С выходов дискриминатора 19 считанная информация через мультиплексоры 10 и 13 поступает на входы блока 14, где поразрядно сравнивается с записанной по этому адресу информацией,.поступающей на другие входы блока 14 из блока 8.

Если информация не совпадает, то с

488?

4 выхода блока 14 подаются в блок 3 и на генератор 15 сигналы наличия брака, по которым блок 3 останавливает процесс контроля.

Если считанная и записанная информация в блоке 14 совпадают, то сигнал с выхода блока 14 запускает генератор 15, по сигналу с выхода которо1р го в блоки 3 и 8 поступают сигналы, обеспечивающие продолжение контроля по следующим по порядку адресам.

После контроля данных по всем адресам проверяемой микросхемы, в слу15 чае отсутствия ошибки при считывании, по сигналу переполнения регистра 7, проходящему через формирователь 16, узел 19 и формирователь 20, в счетчике 21 устанавливается код "0001"

2О и происходит повторный обход всех адресов проверяемой микросхемы ППЗУ, при этом работают источник 26 питания, ключевой элемент 29 и формирователь 24, обеспечивающие минимальное значение напряжения питания и номинальное время выборки.

Аналогично организованы семь последующих режимов динамического контроля.

ЗО В случае отсутствия неисправности при всех девяти режимах контроля из формирователя 20 на вход пульта 4 выдается сигнал годности контролируемого блока памяти и индицируется

35 сигнал окончания контроля °

Формула изобретения

Составитель Т, Зайцева

Техред N,Õoäàíè÷ Корректор A. Обручар

Редактор И.Рыбченко

Заказ 6511/54 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предгриятие, r. Ужгород, ул, Проектная, 4

5 14 ционными входами дешифратора режимов контроля, с первого по третий выходы которого подключены соответственно к управляющим входам управляемых ключевых элементов, информационные входы которых соединены с выходами источников питания, с четвертого по шестой выходы дешифратора режимов контроля подключены соответственно к входам формирователей одиночных импульсов, выходы которых соединены о входами элемента ИЛИ, выход которого подключен к управляющему входу буферного регистра числа, информационные входы

44882 6 и выходы которого соединены соответственно с группой выходов и с информационными входами уэла фиксации положения контролируемого блока памяти,. выход которого подключен к входу повторного запуска формирователя управляющих импульсов, вход начального запуска и третий выход которого соеди",0 иены соответственно с выходом и входом останова пульта управления, выходы управляемых ключевых элементов подключены к входам импульсного питания узла фиксации положения контроли15 руемого блока памяти.