Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5п 4 С 11 С 7/00, G 06 F 12/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ .:::,:,(К A8TOPCHOIVIV СВИДЕТЕЛЬСТВУ (21) 4308546/24-24 (22) 08.07.87 (46) 15.12.88. Бюл. N - 46 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) И.Д.Кужольная, А.Э.Солдатенко и В.Е.Чернобылов (53) 681. 325 (088. 8) (56) Заявка Японии У 59-19376, кл. G 06 F 6/06, G 06 F 3/00, 04.05.84.

Заявка Японии У 59-22979, кл. G 06 F 5/06, 3/00, 31.05..84. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙ. СТВО, (57) Изобретение относится к вычислительной технике и может быть применено для подготовки данных в системах обработки потоков данных в реальном

„„80„„1444 А1 масштабе времени. Целью изобретения является увеличение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее блок 3 буферной памяти, счетчик 1 адреса слов, блок 15 управления, дополнительно введены еще два блока 5, 7 буферной памяти, два счетчика 12, 14 адреса, входной регистр 2, три Dтриггера 4,6,8. Параллельная входная информация потока данных преобразуется на входе буферной памяти в последовательную форму, разделение буферной памяти на три последователь— но соединенных блока 3, 5, 7 позволяет одновременно производить считывание из буферной памяти утроенного объема информации в последовательной форме, удобной для дальнейшей обработки. 2 ил.

1444884

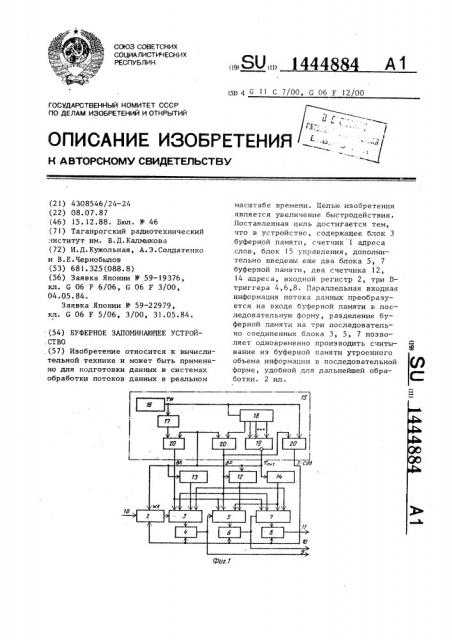

Изобретение относится к вычислительной технике и может быть применено для подготонки данных н устройствах цифровой обработки сигналов в реальном масштабе времени, Целью изобретения является увеличение быстродействия, На фиг.! приведена функциональная схема устройства; на фиг.2 — временная диаграмма работы блока управления.

Устройство содержит параллельный вход 1, входной регистр 2, первые блок 3 буферной памяти и D-триггер 15

4, вторые блок 5 буферной памяти и Втриггер 6, третьи блок 7 буферной памяти и D-триггеров 8, три последовательных выхода 9-11, счетчик 12 адресов разрядон слов, два счетчика ад- 20, ресон слон 13, 14 и блок 15 управления. Блок 15 состоит из генератора

16 тактовых импульсон, элемента 17 задержки ñ, для формирования эадержанных тактовых импульсов ТИ, счетчика

18 на 2 (п+1), дешифратора 19 (в+1)-го такта Т, и трех элементов И 20, формирующих управляющие сигналы: ВК (ныбор кристалла), BP (выбор режима) и 3-Сдн (запись в D-триггеры и сдвиг 30 во входном регистре 2).

Устройство работает следующим образом.

Блоки 3, 5 и 7 памяти магазинного типа реализованы на запоминающих устройствах с произвольной выборкой и предназначены для записи в последовательном коде текущих величин п-разрядных слов а, входного патока данных и выдачи на выход устройства в последовательном коде величин трех задержанных и сдвинутых относительно друг друга слов а; „, а;+ +, а;,1,+ . Объем второго и третьего блоков памяти 5, 7 составляет по 1 и-разрядных .слов, т,е. по 1 s n одноразрядных ячеек. Первый блок 3 памяти объемом 1 г одноразрядных ячеек

50 предназначен для выравнивания во времени выходной информации нескольких параллельных и синхронных потоков данных при использовании такого же числа предлагаемых устройств. Принцип работы блоков 3,5 и 7 буферной памяти основан на циклическом выполнении считывания одного разряда соответственно слов а <,1,, a;+>,p, а;,p, g и записи в оснободиншиеся ячейки того же разряда "соответственно слов а,, а,, а;

Адрес первого блока 3 памяти формируется двумя циклически работающими счетчиками: счетчиком 12 адресов разрядов слон (мпадшая часть адреса, определяющая разряды слов) и первым счетчиком 13 адресов слов (старшая часть адреса, определяющая непосредственно слова). Адреса второго и третьего блоков 4 и 5 памяти формц руются также двумя циклически работающими счетчиками: счетчиком 12 ад» ресов разрядов слов (младшая часть адреса) и вторым счетчиком 14 адресов слов (старшая часть адреса).

Цикл записи-считывания слов состоит иэ и+1 тактов. Каждый такт состоит из двух полутактов, В первом полутакте первого такта цикла по положительному фронту управ ляющего импульса 3-Сдв (с четвертог@ выхода блока 15 управления) происхо дит сдвиг информации во входном регистре 2 с выдачей íà его последовательной выход первого разряда слова а;, по единичному уровню импульса ВР (с второго выхода блока 15 управления) и импульсу ВК (с первого выхода блока 15 управления), считывание и далее запись первых разрядов слов а, а; <, а;+, по отрицательному перепаду импульса 3-Сдв соответ стненно н первый 4, второй 6 и третий 8 выходные D-триггеры и выдача их с выходов D-триггеров на выходы

9, 1О и ll устройства.

Во втором полутакте первого такта цикла по нулевому уровню импульса BP и импульсу ВК происходит запись с последовательного выхода входного регистра 2 и с выходов первого 4 и второго 6 выходных D-триггеров первых разрядов соответственно слов а, а; 1,, а; 1, в освободившиеся в первом полутакте ячейки соответственно первого, второго и третьего блоков памяти

3, 5 и 7, по положительному фронту импульса BP срабатывает счетчик 12 разрядов слов, увеличивая на единицу адрес ячеек всех трех блоков памяти.

Второй и последующие до и-ro включительно такты цикла выполняются аналогично первому такту„ при этом обрабатываются соответстэеннс" =o второго ло и-й разряды тех же слон.

В (и+!)-м такте по отрицательному фронту импульса Т р„ (с -.ретьего ны1444884

l3HHMIIH Заказ 6511/54 Тираж 590 Подписное

Произв.-полигр. пр-тие, r. Ужгород, ул. Проектная, 4 хода блока 15 управления) происходит параллельная запись во входной регистр 2 следующего слова а;+, входного потока данных, по нулевому уровню импульса Т „„ происходит сброс в нулевое состояние счетчика 12 адресов разрядов слов, па положительному фронту импульса Т „+, срабатывают первый и второй счетчики 13 и 14, увели- 10 чивая на единицу свое состояние и подготавливая блоки памяти к обработ ке следующих слов в следующих циклах работы.

Формула иэ обретения

Буферное запоминающее устройство, содержащее первый блок буферной памяти, первый счетчик адреса слов и блок 20 управления, первый и второй выходы которого соединены соответственно с входом выборки и входом управления записью-чтением первого блока буферной памяти, счетный вход первого счетчика адреса слов соединен с третьим выходом блока управления, выход разрядов первого счетчика адреса слов соединен с входами старших разрядов первого блока буферной памяти, о т — З0 л и ч а ю щ е е с я тем, что, с целью расширения функциональных воз.можностей и увеличения быстродействия, в него введены второй и третий блрки буферной памяти, второй счетчик ЗБ адреса слов, счетчик адреса разрядов слов, входной регистр и три триггера, причем параллельный вход устройства соединен с параллельными информационными входами входного регистра, вход 40 управления параллельным занесением данных и вход управления последовательным сдвигом данных входного регистра соединены соответственно с третьим и четвертым выходами блока управления, информационные входы первого, второго и третьего блоков бу ферной памяти соединены соответственно с последовательным выходом входного регистра, выходами первого и второго D-триггеров, выходы первого, второго и третьего блоков буферной памяти соединены соответственно с Dвходами первого, второго и третьего

D-триггеров, входы выборки и входы управления записью-чтением второго и третьего блоков буферной памяти соединены соответственно с первым и вторым выходами блока управления, младшие разряды адреса первого, втсьрого и третьего блоков буферной памяти соединены с разрядами выхода счетчика адреса разрядов слов, старшие разряды адреса второго и третьего блоков буферной памяти соединены с разрядами выхода второго счетчика адреса слов, счетный вход которого соединен с третьим выходом блока управления, счетный вход и вход установки в нулевое состояние счетчика адреса разрядов слов соединены соответственно с вторым и третьим выходами блока управления, входы синхронизации перваго, второго и третьего D-триггеров соединены с четвертым выходом блока управления, выходы первого, второго и третьего D-триггеров соединены соответственно с первым, вторым и третьим выходами устройства.