Запоминающее устройство с сохранением информации при аварийном отключении питания

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в цифровых вычислительных устройствах , где требуется обеспечение сохранности информации при кратковременных отключениях и выходах за допустимые значения питающих напряжений . Цель изобретения - повышение надежности устройства. В устройство,содержащее блоки памяти, основные и резервный источники питания, блок контроля , группу элементов И и ключ, введены элемент задержки, два ключа и элемент И с соответствующими связями, которые позволяют повысить надежность защиты информации от разрушения, т.к. нет необходимости для дублирования записанной информации дополнительным блоком памяти. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (П) Ш 4 G 11 С 29 00 р

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I (21) 4209538/24-24 (22) 11. 03. 87 (46) 15.12.88. Бюл. У 46 (72) С.В.Овчинников (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

У 736178, кл. С 11 С 29/00, 1978.

Авторское свидетельство СССР

У 1176386, кл. С 11 С 29/00, 1986. (54) ЗАПОМИНАКЩЕЕ УСТРОЙСТВО С СОХРАНЕНИЕМ ИНФОРМАЦИИ ПРИ АВАРИЙНОМ ОТКШОЧЕНИИ ПИТАНИЯ (57) Изобретение может быть использовано в цифровых вычислительных устройствах, где требуется обеспечение сохранности информации при кратковреI менных отключениях и выходах за допустимые значения питающих напряжений. Цель изобретения — повышение надежности устройства. В устройство,содержащее блоки памяти, основные и резервный источники питания, блок контроля, группу элементов И и ключ, введены элемент задержки, два ключа и элемент И с соответствующими связями, которые позволяют повысить надежность защиты информации от разрушения, т.к. нет необходимости для дублирования записанной информации дополнительным блоком памяти. 2 ил.

1444897

30 мально и максимально допустимые значения напряжений источников 1, 2 пи ания.

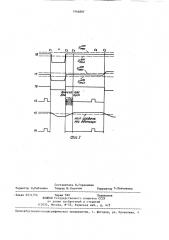

При напряжениях источников 1, 2 питания U „„, и U„„, не удовлетворяющих неравенствам (1), блок 4 контроля выдает сигнал логического нуля.

Прн напряжениях источников 1, 2 питания, удовлетворяющих неравенствам (1), на выходе 18 блока 4 контроля имеется "1", ключи 5, 6 и 7 замкнуты, питание устройства осуществляется от источников 1 и 2 питания, при соответствующих сигналах на управляющих входах 12 и 13 происходит обращение к ячейкам блоков 10 памяти.

Изобретение относится к запоминающим устройствам и может быть применено в цифровых вычислительных устройствах, где требуется обеспечение сох- 5 ранности информации при кратковременном отключении и выходах за допустт мые значения питающих напряжений.

Цель изобретения — повышение надежности устройства. !О

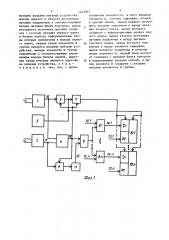

На фиг. 1 приведена функциональная схема запоминающего устройства, на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит основные ис- 15 точники 1 и 2 питания, резервный источник 3 питания (например, емкостный накопитель), блок 4 контроля, ключи 5-7, группу 8 элементов И, элемент И 9, блоки 10 памяти, элемент 20

11 задержки (например интегрирующая

RC-цепь), входы 12 "Выборка", адресные входы 13, выходы 14 группы 8 элементов И, выход 15 элемента 11 задержки, выходы 16, !7 источников 1 и

2 питания, выход 18 блока 4 контроля.

Источник 1 питания через ключи 5 и 7 питает блоки памяти, а источник

2 питания через ключ 6 питает логические элементы, Устройство работает следующим образом.

Блок 4 контроля, который может быть выполнен, например, на основе компараторов, выдает сигнал, равный логической единице, при напряжениях источников 1 и 2 питания, удовлетворящих неравенствам: ипт ттипу т» » - "н»т - »„„s (1) «О ип1 „нп2

U mi n - - Hn l щд у в П с где ипт»»ч и ип» и т2 (!»»» ц щ,» 1 » » в 0»т » мини

При отключении источников 1 и 2 питания (в момент времени t,) на выходе 18 блока 4 контроля формируется

"0". Ключевые элементы 5, 6 и 7 отключают питание от схем управления блоков 10 памяти и логических элементов схемы, при этом питание матрицы запоминаюшИх элементов осуществляется от резервного источника 3 питания.

Сигнал "0" на выходе элемента И 9 запрещает обращение с входов 12 к блокам 10 памяти. Таким образом, обращение к блокам 10 памяти надежно заблокировано как по сигналу "Обращение", так и по питанию схемы управления, что исключает разрушение информации во время переходных процессов.

Аналогично устройство работает при любом невыполнении неравенства (1), в частности в момент времени t< при превышении напряжением U„, на выходе 17 максимально допустимой величиныi

При включении (в момент времени

t ) источников 1 и 2 питания на выхо2 де 18 блока 4 контроля появляется

"1" ключи 5, 6; и 7 подключают основные источники 1 и 2 питания к устройству. При включении источников 1 и 2 питания на входы 12 группы 8 элементов И действует помеха в интервале времени t < — t» однако помехи на входы 14 блоков 10 памяти не проходят, так как напряжением на выходе элемента 11 задержки (интегрирующая

РС-цепь) не достигнут уровень "1".

Если постоянная времени интегрирующей цепи больше, чем интервал време-. ни t z — з, то устройство надежно защищено от разрушения информации во время включения питания. Обращение к . блокам 10 памяти происходит после окончания помех включения питания и достижения уровня "т" на выходе элемента 11 задержки по приходу сигнала "Обращение" в момент времени t4 °

Формула изобретения

Запоминающее устройство с сохранением информации при аварийном отключении питания, содержащее блоки памяти, первый, второй v..резервный источники питания., блок контроля, группу элементов И и первьый ключ, входы первого и второго источников ттитания являются первьм ч вторым. ос3 144 новными входами питания устройства, выходы первого и второго источников питания подключены к соответствующим входам питания блока контроля, выход резервного источника питания соединен с входами питания первого ключа и блоков памяти, информационные входы которых подключены к выходу первого ключа, первые входы элементов И группы являются входами выборки устройства, выходы элементов И группы подключены к соответствующим управляющим входам блоков памяти, адресные входы которых являются адресными входами устройства, о т л и— ч а ю щ е е с я тем, что, с целью

489 7 повышения надежности, в него введены элементы 11, элемент задержки, второй и третий ключи, выход первого источника питания подключен к входу пита5 ния второго ключа, выход которого соединен с информационным входом первого ключа, выход второго источника питания подключен к входу питания

1О третьего ключа, выход которого подключен к входу элемента задержки, выход которого подключен к второму входу элемента И, первый вход которого соединен с выходом блока контроля

15 и управляющими входами ключей, а выход элемента И соединен с вторыми входами элементов И группы.

1444897

12

Составитель В,Гордонова

Техред М.Ходанич

Корректор Э.Лончакова

P едакт ор И, Ры 6ч е нко

Заказ 65 11/54 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, 11осква, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. ужгород, ул. Проектная, 4