Синхронный делитель частоты на 9 на jk-триггерах

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике, может быть использовано в цифровых синтезаторахчастоты, в вычислительной технике о Достижение поставленной цели - увеличение длительности выходных импульсов - позволяет абоненту использовать более низкочастотную элементную базу. Устройство содержит JK-триггеры 1...4, элемент И 5, входную шину 7, тину 6 сброса, шину 8 логической единицы и выходную шину 9. В описании имеются логические уравнения для J- и К-входов ЛК-триггеров 1...4. Устройство обеспечивает синхронный режим работы и построено на безвентильной схеме при одиночных Л-, К-входах всех ЛК- триггеров. 2 ил. с

СОЮЗ СОВЕТСКИХ

СО14ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) 01) А1 (51)4 Н 03 К 23 40 ю:/, Е

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4222543/24-21 (22) 06.04.87 (46) 15.1?.88. Бюл. У 46 (72) 10.À.Базалев и В,И. Мяснов (53) 621.374(088.8) (56) Авторское свидетельство СССР

У 1148118, кл. Н 03 К 23/40, 28,09.83.

Авторское свидетельство СССР

У 1307584, кл. Н 03 К 23/40, 17.06.86. (54) СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ .

НА 9 НА JK-ТРИГГЕРАХ (57) Изобретение относится к импульсной технике, может быть использовано в цифровых синтезаторах частоты, в вычислительной технике. Достижение поставленной цели — увеличение длительности выходных импульсов — позволяет абоненту использовать более низкочастотную элементную базу, Устройство содержит ЛК-триггеры 1...4, элемент И 5, входную шину 7, шину 6 сброса, шину 8 логической единицы и выходную шину 9. В описании имеются логические уравнения для J- и К-входов ЛК-триггеров 1...4, Устройство обеспечивает синхронный режим работы и построено на безвентильной схеме при одиночных Л-, К-входах всех ЛКтриггеров. 2 ил.

1444938

Изобретение относится к импульсной технике и может быть использовано в цифровой аппаратуре, например, в цифровьтх синтезаторах частоты.

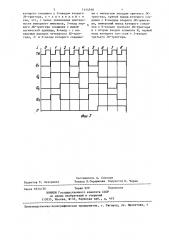

Цель изобретения — увеличение длительности выходных импульсов, что позволяет абоненту использовать более низкочастотную элементную базу, На фиг. 1 приведена электрическая функциональная схема синхронного делителя частоты на 9 на TK-триггерах; на фиг. 2 — временные диаграммы его работы, где обозначено: i — номера состояний устройства; ТИ вЂ” тактовые им- 15 пульсы на тактовой шине; О <, О, О., Q — диаграммы сигналов на прямых выходах соответственно первого, второго, третьего и четвертого ЛК-триггеров; П вЂ” импульс переноса на выхо- 20 де элемента И.

Устройство содержит первый 1, второй 2, третий 3 и четвертый 4 JKтриггеры, элемент И 5, первый вход которого соединен с прямым выходом 25 первого JK-триггера 1 и с J-входом третьего JK — триггера 3, К-вход кото— рого соединен с вторым входом элемента И 5 и с инверсным выходом второго

ЛК-триггера 2, J-вход которого сое- 30 динен. с инверсным выходом первого

JK-триггера 1, K-вход — с прямым выходом третьего JK-триггера 3 инверс.— ный выход которого соединен с 3- и

К-входами четвертого JK-триггера инверсный выход которого соединен с

К-входом первого JK-триггера 1, шину б сброса, шину 7 тактовую, которые соединены соответственно с R- и Свходами первого 1, второго 2, третье- 40 го 3 и четвертого 4 TK-триггеров, шину 8 логической единицы, которая соединена с 3-входом первого ЛК-триггера 1, и выходную шину 9, которая соединена с выходом элемента И 5, Указанное соединение элементов соответствует следующим логическим уравнениям для J- и К-входов первого 1, второго 2, третьего 3 и четвертого 4 3К-триггеров и для сигнала П

50 (перенос) на выходной шине 9: Л = 1, ю 1 ° 1 4 ° Уз Чав

К,=,, К,=Ю„К,=6„= Q, Работа сийхронного делителя .частоты на 9 на TK-триггерах полностью опи55 сывается этими .погическими уравнениями. По сигналу с шины 6 все ЛК-триггеры устанавливаются в исходное нулевое положение, при этом (фиг. 2 при = О) состояния выходов равны

Q 0 О = О, Q = О, (1 = О и тогда по логическим уравнениям для J- u

К-входов триггеров определяет состояния входов, которые равны: J = 1

Поскольку TK-триггер при J = 0 и

К = О не изменяет своего состояния, при J = 1 и К = О переключается з состояние "1", при 3 = 1 и К = 1 переключается в противоположное состояние и при 3 = 0 и К = 1 переключается в состояние "0" (3K-триггеры реагируют на изменение тактового импульса со значения ТИ = 1 на ТИ = О), то при поступлении по шине 7 первого импульса в состояние "1" перекгючаются JK-триггеры 1,?„4, à 3К-триггер 3 не изменяет своего состояния т.е. состояния выходов равны: Ц »= 1, (= О = О,, Q,, =- 1 (фиг,, 2 при

1).

Состояния в ;адов при этом следующиеЛ 1, 1 О, 3.,=-1

K-ОК=ОК=ОК=1

Ь 9 .> Ь ф °

При поступлении по шине 7 второго импульса изменяют свое состояние

3К-триггеры 3 и 4, JK-триггер 3 переключается в состояние "1", à JKтригrep в состояние "0", 3К-триггеры и 2 остаются в прежнем состоянии (фиг. 2 при i = 2), следовательно, состояния выходов и входов принимают следующие значения: 0„=.1, О = 1, Q = 1 Q = Ов 31= )ь Ля Ое Лз

Рассматривая и далее работу устройства таким же образом, получаем все значения входов и выходов при каждом i (см. фиг, 2), Сигнал переноса появляется при поступлении по шине 7 шестого импульса и снимается при поступлении девятого импульса. Устройство после этого возвращается в исходное состояние.

Формула изобретения

Синхронный делитель частоты на 9 на JK-триггерах, содержащий первый, второй, третий и четвертый ЛК-триггеры, R- и С-входы которых соединены соответственно с шиной сброса и с тактовой шиной, элемент И, выход которого соединен с выходной шиной, первый вход — с прямым выходом первого JK-триггера, инверсный выход

44938

Составитель А. Соколов

Техред Л.Сердюкова Корректор С. Черни

Редактор Т, Лаэоренко

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Заказ 6514/56

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проект ая, ектная 4

3 14 которого соединен с J-входом второго

JK-триггера, отличающийся тем, что, с целью увеличения длительности выходного импульса, J-вход первого JK-триггера соединен с шиной логической единицы, К-вход — с инверсным выходом четвертого JK-триггера, J- и К-входы которого соединены с инверсным выходом третьего JKтриггера, прямой выход которого соединен с К-входом второго JK-тригге5 ра, инверсный выход которого соединен с К-входом третьего JK-триггера и с вторым входом элемента И, первый вход которого сое.. лен с Д-входом третьего JK-триггера.