Дельта-модулятор

Иллюстрации

Показать всеРеферат

Изобретение относит ся к вычислительной технике и технике связи. Его использование в системах передачи речевой информации, работающих при низких скоростях передачи, позволяет повысить точность дельта-модулятора за счет расширения частотного диапазона входного сигнала. Дельта-модулятор содержит компаратор 1, триггер 2, сдвиговые регистры 3, цифроаналоговый преобразователь 6 и сумматор 5.1. Введение полусумматоров 4, сумматоров 5.2-5.(N+1) и блоков 7 инвертирования обеспечивает сверткувходного сигнала с его корреляционной функцией , не ограниченной по спектру, 1 ил., а S (О

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (gg g Н 03 M 3/02

Яг, ОПИСАНИЕ ИЗОБРЕТЕНИ « ".

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblT

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ. (21) 4233606/24-24 (22) 22.04.87 (46) 15 12 88 Бюл У 46 (71) Рюкский политехнический институт им. А.Я. Пельше (72) Г.Н. Котович, И.М. Малашонок и К.C. Комаров (53) 621.376.56(088.8) (56) Авторское свидетельство СССР

Ф 1163477, кл. Н 03 М 3/02, 1983.

Авторское свидетельство СССР

У 1203706, кл. Н 03 И 3/00, l985

Авторское свидетельство СССР

У 1129732, кл. Н 03 И 3/02, 1983.

„.Я0„„1444953 А 1 (54) ДЕЛЬТА-МОДУЙ1ТОР (57) Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи речевой информации, работающих при низких скоростях передачи, позволяет повысить точность дельта-модулятора за счет расширения частотного диапазона входного сигнала. Дельта-модулятор содержит компаратор 1, триггер 2, сдвиговые регистры 3, цифроаналоговый преобразователь 6 и сумматор 5.1.

Введение полусумматоров 4, сумматоров 5.2-5.(N+1) и блоков 7 инвертирования обеспечивает сверткз . входного сигнала с его корреляционной функ- а цней, не ограниченной по спектру.

1 ил.

1444953

Изобретение относится к вычислительной технике и технике связи и мо жет быть использовано в системах передачи речевой информации, работающих

5 при низких скоростях передачи.

Цель изобретения — повышение точности дельта-модулятора за счет расширения частотного диапазона входного сигнала. 1О

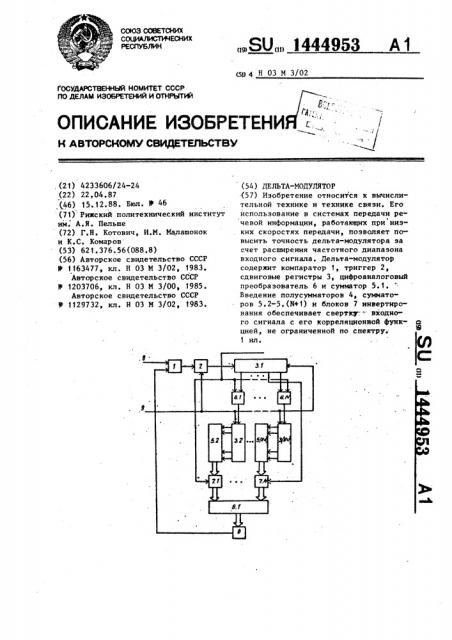

На чертеже приведена функциональная схема дельта-модулятора.

Дельта-модулятор содержит компаратор 1, триггер 2, первый — (N+1)ый сдвиг овые регистры 3, где N — чи- 15 сло тактов на интервале анализа входного сигнала, а также число разрядов регистрбв 3, первый — N-й полусумматоры 4, первый — (N+1)-ый сумматоры

5, цифроаналоговый преобразователь 2р (ЦАП) 6, первый - N-ый блоки 7 инвер" тирования.На чертеже обозначены ин- формационный и тактовый входы 8 и 9 и выход 10.

В основе работы дельта-модулятора 25 лежит алгоритм предсказания последующего отсчета на основе апостериорных данных.

Дельта-модулятор работает следующим образом. 30

Входной аналоговый сигнал S(nT) со входа 8 поступает на первый вход компаратора 1 и сравнивается с аппроксимирующим напряжением Бд(пТ), формируемым на выходе цифроаналогового преобразователя 5. Результаты сравнения с выхода компаратора 1 с приходом импульсов тактовой последова,тельности и со входа 9 записываются в триггер 2, а с его выхода - в 40 сдвиговый регистр 3.1. В каждом такте работы (с каждым тактовым импульсом) текущий отрезок дельта-модулированного (ДМ) сигнала сдвигается в регистре 3.1, а последний полученный бит хранится в триггере 2. В течение каждого тактового интервала последний бит p(nT) при помощи полусумматоров 4 умножается на предыдущее значения р f(n-1)T); p f(n-2)T); р f(n-N)TJ образуя частичные произ50 ведения p (nT) xp f(n-i)T), где i — расстояние между принятым и последующим битом. Полученные частичные произведения поступают на входы сдвиго вых регистров 3.2 — 3.(N+1) в ко55 торых находятся последние N частичных. произведений, после чего все N значений складываютсл сумматором 5 j

<(j = 2, N+1), на выходе которого оби разуется величина R = Qp(n-k)xp(n-1-k), представляющая собой 1 ый корреляционный момент ДМ-сигнала, усредненный на интервале N. Таким образом, каждая цепочка полусумматор 4 — сдви, говый регистр 3 — сумматор 5 представляет собой коррелятор. Для осуществления предсказания в дельтамодуляторе производится свертка

ДМ сигнала с его автокорреляционной функцией. Поскольку ДМ-сигнал имеет два уровня, представленные здесь как

1 и -1, то свертка может производиться лишь при помощи суммирования сумматором 5.1 выборочно проинвертированных отсчетов корреляционной функ1 ции Sa (nT) = p(nT) ° К + p E(n-1) T) R +

М а P ((«-i)T)R;«, что дсстага! ется применением блоков 7 инвертирования с управлением от соответствующих битов ДМ-сигнала. Если соответствующий бит равен 1, то момент корреляции не инвертируется, и наоборот.

Восстановление аппроксимирующего на5 пряжения S (nT) производится при помощи ЦАП 6.

Поскольку все составляющие корреляционной функции сигнала определяются на равном интервале, спект ральный анализ сигнала, производимый в дельта-модуляторе, косвенно происходит в равньм частотных поддиапазонах, что следует из разложения взвешивающей прямоугольной функцией временного окна, определяемого тактами, в ряд Фурье.

Таким образом видно, поскольку корреляционная функция сигнала не подвергается ограничению по спектру, дельта-модулятор реализует максимально возможный частотный диапазон. Следует отметить, что дополнительным достоинством дельта-модуля- тора является отсутствие аналоговых элементов, что делает его стабильйЬЯ и высокотехнологичным.

Формула и з о б р е т е н и я

Дельта-модулятор, содержащий компаратор, первый вход которого является информационным входом дельта1444953

Составитель О. Ревинский

Техред Л.Сердюкова Корректор И. Муска

Редактор И. Сегляник

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изббретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6515/57

Производственно-полиграфическое предприятие r. ужгород ул. Проектная 4 модулятора, выход соединен с информационным входом триггера, выход которого подключен к информационному входу первбго сдвигового регистра и яв5 ляется выходом дельта-модулятора, тактовые входы триггера и первого.. сдвигового регистра объединены с тактовыми входами второго — (И+1)ro сдвиговых регистров (N - число та- 10 ктов на интервале усреднения) и являются тактовым входом дельта-модулятора, первый сумматор и цифроаналоговыйпреобразователь,отличающийся тем, что, с целью повышения точности 15 дельта-модулятора за счет расширения частотного диапазона входного сигнала, в него введены второй - (N+1)-й сумматоры, первый — N-й блоки инвертирования и первый — N-й полусуммато- 2О ры, первые входы которых объединены с управляющим входом первого блока инвертирования и подключены к выходу триггера, -й выход первого сдвигового регистра (j = N), кроме N ro, подключен к второму входу j-го полусумматора и управляющему входу (j+1)го блока инвертирования, N-й выход первого сдвигового регистра соединен с вторым входом N"го полусумматора, выход j-ro полусумматора соединен с информационным входом (j+1)-ro сдвиго": вого регистра, выходы которого подключены к входам (j+1)-ro сумматора, выходы которого соединены с .информационными входами j-ro блока инвертирования, выходы всех блоков инвертирования подключены к соответствующим входам первого сумматора, выходы которого соединены с входами цифроаналогового преобразователя, выход которого подключен к второму входу компаратора.