Преобразователь позиционного кода в код с большим основанием

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и автоматики и предназначено для перевода кодов чисел из системы счисления с любым основанием в коды чисел с любым большин .основанием в цифровых системах управления и в устройствах обработки информации. Целью изобретения является повышение скорости преобразования . Поставленная цель достигается тем, что в преобразователь позиционного кода, содержащий треугольную матрицу, введена группа треугольных матриц, группа блоков умножения и многовходовый сумматор, причем каждый элемент треугольных матриц содержит умножитель и сумматор. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (!9) (11) 4 59 А1 (59 4 Н 03 М 7/12

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

;-.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, . /

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4251305/24-24 (22) 27.05.87 (46) 15.12.88. Бюл. В 46 (71) Институт кибернетики им. В.М.Глушкова (72) Е.И.Брюхович и А.Ф.Шкитин (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 526884, кл. Н 03 М 7/00, 1973.

Авторское свидетельство СССР

9 1332537, кл. Н 03 М 7/00, 1985. (54) ПРЕОБРАЗОВАТЕЛЬ ПОЗИЦИОННОГО

КОДА В КОД С БОЛЬШИМ ОСНОВАНИЕМ (57) Изобретение относится к области ., вычислительной техники и автоматики и предназначено для перевода кодов чисел из системы счисления с любым основанием в коды чисел с любым большим .основанием в цифровых системах управления и в устройствах обработки информации. Целью изобретения является повышение скорости преобразования. Поставленная цель достигается тем, что в преобразователь позиционного кода, содержащий треугольную матрицу, введена группа треугольных матриц, группа блоков умножения и многовходовый сумматор, причем каждый злемент треугольных матриц содержит умножитель и сумматор. 2 ил.

14449

Изобретение относится к вычислительной технике и автоматике и может быть использовано в устройствах обработки информации, функционирующих в различных системах счисления, для перевода позиционного кода из системы счисления с любым основанием в коды чисел с любым большим основанием. 10

Цель изобретения — повышение скорости преобразования.

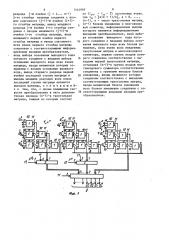

На фиг.1 представлена блок-схема преобразователя кодов на фиг.2— схема ячейки преобразования. 15

Преобразователь кодов (фиг.1) состоит из однотипных ячеек 1, содержит (и-1) блок умножения 2, многовходо- вый сумматор 3. Однотипные ячейки 1 в совокупности образуют и треугольных 20 матриц 4, с выходами старших разря- дов 5 и выходами младших разрядов 6.

Информационные входы 7 преобразователя поступают на входы последних столбцов треугольных матриц 4. Выходы треугольных матриц 8 поступают на входы блоков умножения 2 и входы многовходового сумматора 3, выходы которого являются выходом 9 преобразователя. 30

Вход 10 основания входного кода преобразователя и вход 11 выбора основания выходного кода поступают на все ячейки треугольных матриц. Весовые входы 12 преобразователя поступа-35 ют на входы блоков умножения 2.

Каждая ячейка 1 содержит (фиг.2) умножитель 13 и сумматор 14. Множимое поступает на вход 15, а слагаемое на вход 16, множитель (основание входного кода) поступает на вход 17.

На вход 18 поступает основание выход" ного кода, что обеспечивает выбор системы счисления, блоков 13 и 14.

В основу работы преобразователя кодов, лри переводе числа А из системы счисления с меньшим основанием Р в счисление с большим основанием q, положен алгоритм распараллеливания исходного числа А (р) íà и параллельных ветвей. При этом, каждая из ветвей обрабатывается независимо друг от друга по алгоритму последовательного умножения старшей цифры части числа А (р) на основании исходной

55 системы счисления р с последующим прибавлением к полученному произведению следующей по порядку цифры части числа А (р). Операции проиэвоФ

59 2

4 дятся в q-ичной системе счисления и процесс умножения и сложения повторяется до тех пор, пока не будет добавлена младшая цифра части числа

А (р).

Преобразователь кодов работает следующим образом.

На информационные входы 7 преобразователя подается преобразуемое число А в системе счисления с основанием Р, причем исходное число разбивается на и частей, каждая нз которых содержит (1< „ -1)-1з-разрядов (S=О, 1, 2, ... (и1); 1

= .1 S(m + 1) /и(, знак 1х — ближайшее меньшее целое число, m — максимальная разрядность входного кода; и— целое число, 2 и(т. Старший разряд кода а <, -1, каждой группы поступает на треугольные матрицы через входы 15 ячейки преобразователя 1 первой строки на входы 1 умножителя 13, на выходе которого появляется число, умноженное на константу Р исходной системы счисления. На сумматоре 14 ячейки 1 первой строки происходит суммирование результата умножения и цифры предыдущего разряда à (,) -2 преобразуемой части числа, поступаю щего на входы 16 ячейки преобразования 1. Младший разряд результата, полученный на выходах 6 ячейки 1 первой строки, поступает на входы 15 первой ячейки второй строки, а старший разряд этого результата, полученный на выходах 5 ячейки, поступает на входы 15 второй ячейки второй строки и т.д-. В результате параллельного перевода каждой из и частей на выходах 8 каждой матрицы получаем и частей исходного числа А в счислении q, Результаты перевода, полученные на выходах 8 каждой матрицы, кроме первой, поступают параллельно на входы 15 соответствующих блоков умножения 2, на вторые входы которых подаются соответственно константы Р з в счислении q. Результат с выходов 8 первой матрицы и произведения, полученные на выходах каждого иэ блоков умножения 2, поступают соответственно на и группу входов многовходового сумматора 3. В результате суммирования на выходах 9 получается код преобразованного числа А в системе счисления с основанием q, Операции умножения на блоках умножения 2 и суммирования на многовходонам

1444959

1 1х3

О О

Ох300

1 О

l Ох 300

0 (00

0 ++55

1 3 4

5 х 6561 = 295245

2 24 с4 х 3

О 2 2 х 81 3402

298715

68 сумматоре 3 производится в q-нчной системе счисления.

Таким образом, за один такт рабо-, ты на, выходах 9 преобразователя кодов появляется код преобразованного числа в системе счисления с основанием q, Исходя из этого, максимальная задержка процесса перевода составляет:

TA(p) (l(+,1 — 1 — 2)рекс 4 +

+

Преобразователь позиционного кода в код с большим основанием, выполненный в виде треугольной матрицы одно- тинных ячеек, каждая из которых созадержка сигнала блоком ум9 ноже ния, - задержка сигнала многовходос вым сумматором, а время перевода числа А из счисления р в счисление q в известном преобразователе кодов, равно

Та(Р) = (m 1) ЕЛ

Пример. Перевести число А (120011202112) из троичной в деся» тичную систему счисления. При п Зр з равны 3 81,, 3 6561 а ° держит умножитель и сумматор, причем выход старшего разряда первой ячейки

i-ro столбца матрицы (i = 1... ш-2, m — разрядность входного кода) соеди» нен с входом множимого первой ячейки (1+1)-ro столбца, выход старшего

5 14449 разряда j-й ячейки (j 2... m-1)

g-ro столбца матрицы соединен с входом слагаемого (j-1)-й ячейки (i+1)ro столбца матрицы, выход младшего разряда j-й ячейки i-го столбца соединен с входом множимого (j+1)-й ячейки i-ro столбца матрицы, вход множимого первой ячейки первого столбца матрицы и входы слагаемого 10 всех ячеек первого столбца матрицы соединены с соответствующими информационными входами преобразователя, вход выбора основания выходного кода которого соединен с .входами выбора 15 основания выходного кода всех ячеек матрицы, входы множителя которых соединены с входом основания входного кода, выход старшего разряда первой ячейки последней строки матрицы и 20 выходы младших разрядов всех ячеек последней строки матрицы являются выходом матрицы, о т л и ч а ю щ и йс я тем, что, с целью повышения скорости преобразования в него дополнительно введены (п-1)-я треугольная матрица, каждая из которых состоит

59 6 из (1s 1 в Й) ОднОтипных Ячеек, где 1 = )з(тп + 1)/n(, s = О, (п-1), n - число треугольных матриц, (и-1) блоков умножения и многовходо вой сумматор, информационные выходы которого являются информационными выходами преобразователя, вход выбора основания выходного кода которого соединен с входами выбора основания выходного кода всех блоков умножения, всех ячеек всех введенных треугольных матриц и,многовходового сумматора, первая группа входов которого соединена соответственно с выходами первой треугольной матрицы, остальная (n-1)-я группа входов многовходового сумматора соответственно соединена с группами выходов блоков умножения, входы множимого которых соединены соответственно с выходами соответствующих треугольных матриц, входы множителей блоков умножения всех блоков умножения соединены с со" ответствующими ведовыми вхОдами преобразователя.

1444959

Составитель М. Аршавский

Техред Л.Сердюкова Корректор N.Ìàêñèìèøèíåö, Редактор И.Сегляник

Заказ 6515/57 Тираж 929 Подписное

ЬНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4