Преобразователь числа в модулярный код

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения устройств, функционирующих в фибоначчиевых кодах , например высокочастотных аналого-цифровых преобразователей, с устройствами, функционирующими в модулярном коде, например, высокопроизводительными процессорами. Цель изобретения - расширение области применения за счет возможности преобразования фибоначчиевого кода в модулярный код. Поставленная, цель достигается тем, что преобразователь чис ла в модулярный код, содержащий бло1 1 элементов И, сумматор 2 по модулю, накапливающий сумматор 3 по модулю, регистр 4 сдвига, блок 6 синхронизации, содержит регистр 5 сдвига с соответствующими связями. 2 ил. с S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5y) 4 Н 03 И 7/18

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ll0 ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTHA Р----ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTGPCHOIVIV СВИДЕТЕЛЬСТВУ (21) 4235497/24-24 (22) 27.04.87 (46) 15.22.88. Бюл. К 46 (72) В.И. Ключко, А.В. Ткаченко и О.А. Финько (53) 681. 3. 1 (088. 8) (56) Авторское свидетельство СССР

N 662932, кл. Н 03 И 7/18, 1976, Авторское свидетельство СССР

И 1012237, кл. Н 03 М 7/18, 1981.

Авторское свидетельство СССР

Ф 374596, кл. Н 03 И 7/18, 1970. (54) ПРЕОБРАЗОВАТЕЛЬ ЧИСЛА В ИОДУГГРНЫЙ КОД (57) Изобретение относится к области вычислительной техники и может быть использовано для сопряжения устройств, „„SU» 1444961 А 1 функционирующих в фибоначчиевых кодах, например высокочастотных аналого-цифровых преобразователей, с устройствами, функционирующими в мо дулярном коде, например, высокопроизводительными процессорами. Цель изобретения — расширение области применения за счет возможности преобразования фибоначчиевого кода в модулярный код. Поставленная. цель достигается тем, что преобразователь числа в модулярный код, содержащий блок"

1 элементов И, сумматор 2 по модулю, накапливающий сумматор 3 по модулю, регистр 4 сдвига, блок 6 синхронизации, содержит регистр 5 сдвига с соответствующими связямн. 2 ил.

1444961

Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств, функционирующих в "фибоначчиевом" коде, например, высокоточных аналогоцифровых преобразователей, с устройствами функционирующими в модулярных кодах, например, высокопроизводительными и высоконадежными процессорами.

Цель изобретения - расширение области применения за счет возможности преобразования "фибоначчиевого" кода в модулярный код.

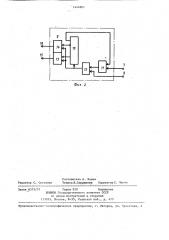

На фиг. 1 представлена схема преобразователя числа в модулярный код, на фиг. 2 — схема блока синхронизации. . Преобразователь (фиг. 1) содержит блок 1 элементов И, сумматор 2 по модулю, накапливающий сумматор 3 по мо- 20 дулю, регистры 4 и 5 сдвига, блок 6 синхронизации, вход 7 запуска преобразователя, тактовый вход 8.преобразователя, вьиод 9 преобразователя.

Блок 6 синхронизации (фиг. 2) со- 25 держит счетчик 10 по модулю, триггер 11, элементы И 12-14, выходы 15 и 16 блока 6 синхронизации, причем вход 7 запуска преобразователя соединен со входом установки в единицу 30 триггера 11, выход которого соединен с первым входом элемента И 12, выход которого соединен со счетным входом счетчика 10 по модулю и с первыми входами элементов И 13 и 14, вьиоды которых являются соответственно выходами 15 и 16 блока 6 синхронизации, прямой и инверсный выходы младшего разряда и импульсный выход обнуления счетчика 10 по модулю сое- 40 динен соответственно со вторыми входами элементов И 13 и 14 и со входом установки в нуль триггера 11. Сумматор

2 и накапливающий сумматор 3 являются сумматорами по модулю pt (P(- 45 модуль системы остаточных классов).

Разрядность регистра 4 сдвига и модуль счетчика 10 равны и (и — разрядность кода Фибоначчи).

Регистр 5 сдвига состоит из (р+1) параллельных регистров разрядности

J log< p<(— параметр кода Фибоначчи)., Преобразование кода А Фибоначчи в модулярный код А выполняется согласно следующему уравнению:

Ф

А = а„р„+ а„, „,+ ... + а,,»

P; =- Cg (i) (mod Pg ) — наименьший неотрицательный вычет от i-ro веса "фибоначчиевого" кода где

Ф Ф

otal и А (А и оЕ;-A =A(modpg)» (,.), 0 при i c. 1; г при =1; ((д-1 )+((з.-р;1) при i ) 1 а, — двоичная цифра;

Ы; - наименьший неотрицательный вычет.

Первые р+1 весов "фибоначчиевого" кода всегда равны единице и, следовательно, не превышают величины

Это позволяет использовать их в качестве исходных условий для получения вычетов Pp,g, ..., P „ с помощью рекурентного соотношения:

P P -,+ ; р, (m«Pg ) В момент времени, соответствующий началу преобразования по входу

7, поступает импульс, в результате чего, на выходах блока 6 синхронизации начинают поочередно вырабатываться единичные импульсы. Первый импульс поступает на вход записи сумматора 3 и записывает в него произведение а, Р, Второй импульс поступает на входы сдвига регистров 4 и 5, производит s них сдвиг информации на один разряд влево. При этом в (р+1)-й разряд регистра 5 записывается значение Р»> а на выходе сумматора

2 образуется значение P p» q . На выходе блока i элементов И образуетса произведение а 3

Принцип преобразования для всех модулей системы остаточных классов аналогичен.

Преобразователь (фиг. 1) работает следующим образом.

В исходном состоянии в регистр 4 записан код преобразуемого числа А в "фибоначчиевом" коде, а в регистр

5 — единицы, накапливающий сумматор

3 по модулю обнулен, состояние блока б синхронизации соответствует исходному. Так как на входы сумматора 2 по модулю поступают единицы, то на . вход записи (р+1)-го разряда регистра

5 поступает величины / . На выходе блока 1 элементов И устанавливается величина а, 144496 1

После паступленйя третьего импульса в накапливающем сумматоре 3 образуется значение

4 тояние, после чего блок 6 готов к новому циклу работы. ! I

Формула изобретения а,P, + а,/3 mo" Pp и так далее.

Таким образом, в процессе преобразования на выходе (р+1) разряда 10 регистра 5 образуются значения j3 на выходе блока 1 элементов И вЂ” значения а, Р,, а„ P . В конце преобразования в накапливающем сумматоре 3 образуется сумма Ж., t5 являющаяся результатом преобразования„

Блок 6 синхронизации работает следующим образом. В исходном состоянии счетчик 10 по модулю и триггер 11 обнулены. 20

В момент времени, соответствующий началу преобразования по входу 7 поступает импульс и устанавливает триггер 11 в единичное состояние. В результате этого на счетный вход счетчика 10 по модулю поступают тактовые импульсы. Так как вторые входы элементов 11 и 14 соединены с прямым и инверсным выходами счетчика 10, соот- 30 ветствующими его младшему разряду, то иа выход 15 блока поступают импульсы с нечетными номерами, а на выход 16 - с четными. Так как модуль .пересчета счетчика 10 равен п, то при поступлении на информационный вход накапливающего сумматора 3 по модулю последнего слагаемого à, Р счетчик 10 обнуляется и на его импульсном выходе обнуления вырабаты- 40 вается единичный импульс, который сбрасывает триггер 11 в нулевое сосПреобразователь числа в модулярный код, содержащий блок элементов

И, сумматор по модулю, накапливающий сумма тор по модулю, пер вый ре гистр сдвига и блок синхронизации, причем. вход запуска и тактовый вход преобразователя соединены соответственно со входом запуска и тактовым входом бло* ка синхронизации, первый выход которого соединен с входом разрешения сдвига первого регистра сдвига, выход младшего разряда которого соеди-. нен с первым входом блока элементов

И, выход которого соединен с информационным входом накапливающего сумматора по модулю, о т л и ч а юшийся тем, что, с целью расши-. рения области применения путем обес" печения воэможности преобразования фибоначчиевого кода в модулярный код, он содержит второй регистр сдвига, причем выход младшего разряда второго регистра сдвига соединен с вторым входом блока элементов И и с входом первого слагаемого сумматора по модулю, вход второго слагаемого которого соединен с выходом старшего разряда второго регистра сдвига, вход старшего разряда которого соединен с выходом сумматора по модулю, первый и второй выходы блока синхронизации соединены соответственно с входом разрешения сдвига второго регистра сдвига и с входой разрешения записи накапливающего сумматора по модулю, выход которого является выходом преобразователя.

1444961

Составитель А. Клюев

Техред Jf.Ñåðäþêoâà Корректор С. Черни

Редактор С. Сегляник

Заказ 6515/57

Тираж 929 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4