Устройство для отладки многопроцессорных систем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет восстановцть реальную последовательность взаимодействия процессоров отлаживаемого устройства после окончания прогона отлаживаемых программ. Цель изобретения - расширение функциональных возможностей за счет фиксации циклов шины межпроцессорной магистрали . Устройство содержит однозарядный блок 1 оперативной памяти, триггер 2, счетчик 3 импульсов, мультиплексор 4, элемент НЕ 13 и блок 5 оперативной памяти. Устройство дополнительно содержит элемент ИЛИ 8, элемент 7 сравнения и счетчик 6 импуЛьсов, позволяющие определить момент вьшолнения каждого цикла шины любого процессора по отношению к моменту прекращения занесения информации в блок трассировки устройства. Цель достигается за счет того, что в каждом цикле шины процессора в трассе запоминается длительность этого цикла в периодах сигнала синхронизации процессора, 2 ил. S

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„1446624 А1 (51)4 G Об F 11/28

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

-ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР

С ОПИСАНИЕ ИЗОБРЕТЕНИ

Н А BTQPCKOMY СВИДЕТЕЛЬСТВУ

3, з и

° э Я

Ф еалажа3аенону уетрааст3у

4Ьаl (21) 4248421/24-24 (22) 07.04.87 (46) 23.12.88. Бюл. У 47 (71) Институт кибернетики им,В.М.Глушкова (72) О.В.Цвелодуб (53) 681,3 (088,8) (56) Микропроцессоры, системы программирования и отладки./ Под ред.

В.А.Юсникова.М.: Энергоиздат, 1985, с. 148., ЩЛ,ТТ.-ICE software — multiple in

circuit emulator // Intel System

Data Catalog. Santa Clara. Intel

Corp., 1980, р. 12-54. (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ МНОГОПРОЦЕССОРНЫХ СИСТЕМ (57) Изобретение относится к вычислительной технике и позволяет восстановить реальную последовательность взаимодействия процессоров отлаживаемого устройства после окончания прогона отлаживаемых программ. Цель изобретения — расширение функциональных возможностей за счет фиксации циклов шины межпроцессорной магистрали. Устройство содержит однозарядный блок 1 оперативной памяти, триггер 2, счетчик 3 импульсов, мультиплексор 4, элемент НЕ 13 и блок 5 оперативной памяти. Устройство дополнительно содержит элемент ИЛИ 8, элемент 7 сравнения и счетчик 6 импуль" сов, позволяющие определить момент выполнения каждого цикла шины любого процессора по отношению к моменту прекращения занесения информации в блок трассировки устройства. Цель достигается за счет того, что в каждом цикле шины процессора в трассе запоминается длительность этого цикла в периодах сигнала синхронизации процессора, 2 ил.

1446624

Изобретение относится к вычисли- . тельной технике и может быть исполь зовано при создании микроЭВМ, микроконтроллеров и других устройств на основе микропроцессоров.

Целью изобретения является расши рение функциональных возможностей устройства за счет фиксации длительф ности циклов шины межпроцессорьай магистрали.

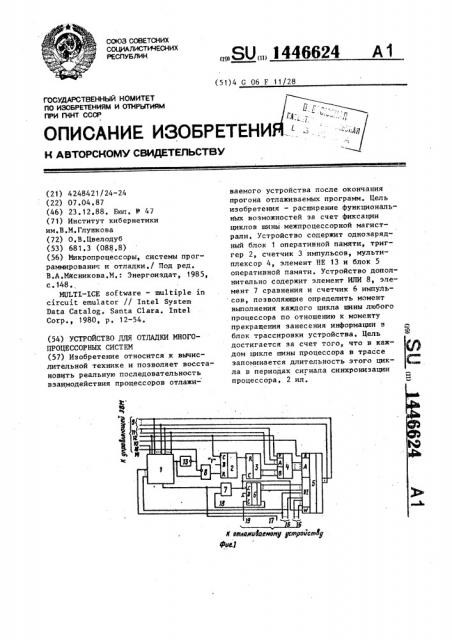

На фиг,1 приведена схема устройства для отпадки многопроцессорных систем, на фиг.2 — схема одноразрядного блока оперативной памяти. 1э

Устройство состоит из одноразрядного блока 1 оперативной памяти, триггера 2, .счетчика 3 импульсов, мультиплексора 4, блока 5 оперативной памяти, счетч.ика 6 импульсов, схемы 7 20 сравнения и элемента ИЛИ 8, вьгходы блока 5 оперативной памяти подключены к двунаправленной информационной .магистрали 9. На Фиг.1 также обозначены вход 10 признака чтения, первая 25 группа 11 адресных входов устройства, вход 12 установки режима устройства, элемент НЕ 13, выход 14 запроса прерывания, вторая группа 15 адресных входов устройства, шины устройства, Зц группа 16 информационных входов устройства, вход 17 цикла, выход 18 переполнения счетчиков, вход 19 тактовый и вход 20 записи устройства.

Устройство работает следующим об-. разом

Цикл отладки состоит из этапов управления и трассировки., На этапе управления сигнал на входе 12 имеет уровень лог."0", Этот сигнал поступает в блок 1.и разрешает запись в блок 1 а,дреса, при появлении которого на вторых адресных входах 15 усг-. ройства на этапе трассировки прекращается запись информации в блок 5 .оперативной памяти. Аналогично программируется второе устройство для отладки многопроцессорных систем.

Затем управляющая ЭВМ запускает выполнение праграмм в атлаживаемам устройстве и выставляет сигнал уров,ня лог,.".1" на входе 12 режима уст-. ройства? что. означает переход к эта« пу трассировки. Па переходу сигнала на входе 12 режима в состояние лог. ,"1" т иггер 2 устанавливается в единичное. состояние и разрешает счет в счетчике.З импульсов..

На этапе трассировки сигнал на

Н 11 входе 17 имеет уровень лог. 1 в течение времени, пока длится цикл шины первого процессора отлаживаемого и ч устройства, и уровень лог„ О в течение остального времени.. Если циклы шины. идут непрерывно один за другим, та на входе 17 присутствуют короткие импульсы уровня.лог. О . По положил тельному перепаду (переходу из низкого уровня.в высокий) ;игнала на входе 17 значение на выходе счетчика 3 импульсов увеличивается на единицу, присутствующий на управляющем входе мультиплексора 4 сигнал уров« ня лог".1" разрешает передачу информации,на выходы мультиплексора 4 с его второй. группы информационных входов. Код- "a выходе счетчика 3 импульсов является. адресом занесения инФормации в.,блок 5 оперативной памяти, информация. заносится по отрицательному перепаду.(переходу из высокого уровня в низкий) сигнала на входе 17 с информационной и адресной магистралей первого процессора отлаживаемого устройства и является трассой выполнения программы этим процессором. Одновременно в блок 5 оперативной памяти заносится информация с информационных выходов счетчика 6 импульсов, который подсчитывает число импульсов синхронизации первого.процессора атлаживаемого устройства на входе 19, поступившее с момента последней записи в блок 5 оперативной памяти, При переполнении счетчика 6 импульсов на его выходе переполнения н появляется импульс уровня лог. 1 который, пройдя через схему 7 сравнения, поступает на тактовый вход счетчика 3 импульсов и увеличивает эначе?п?е числа Hà его выходах на единицу, адресуя тем самым следующее слово блока 5 оперативной памяти.

Если длительность текущего цикла шины превышает два периода появления импульсов на выходе переполнения счетчика 6 импульсов, процесс адресации нового слова блока 5 оперативной памяти повторяется.

На этапе трассировки коды с магистрали адреса первого процессора отлаживаемого устройства поступают также в блок ; и сравниваются с записанным там адресом останова; при совпадении адресов на выходе блока 1 появляется импульс уровня лаг,"1", который уста-.

1446624 навливает триггер 2 в нулевое состояние, запрещая счет счетчику 3 импульсов, и через элемент НЕ 13 поступает на выход 14 прерывания устройства.

Аналогично работает второе устройство для отладки многопроцессорных систем. Входы прерываний устройств объе" динены по схеме "монтажное ИЛИ", причем нагрузочное сопротивление распо- 10 ложено в управляющей ЭВМ. Импульс прерывания, появившийся на выходе 14 прерывания устройства, пройдя через элемент ИЛИ 8 каждого устройства, устанавливает в нулевое состояние в каж-15 дом устройстве триггер 2 и запись информации в блок 5 оперативной памяти одновременно прекращается во всех устройствах. Число одновременно работающих устройств для отладки много20 процессорных систем не ограничено двумя и может быть любым.

Реагируя на полученное прерывание, управляющая ЭВМ останавливает выполнение программ процессорами отлаживаемо-2б

ro устройства и переходит к этапу управления. устанавливая на входе режима 12 сигнал уровня лог."О". При этом Hp выходы мультиплексора 4 поступают коды с его первой группы инфор" Э0 мационных входов, Управляющая ЭВМ, выставляя соответствуншще коды на первых адресных входах, может прочитать трассировочную информацию из блока 5 оперативной памяти. Цикл отладки завершен.

Таким образом, зная величину периода импульса синхронизации каждого процессора отлаживаемого устройства и принимая во внимание, что длитель" ность цикла шины процессора всегда кратна целому числу периодов синхросигнала этого процессора, можно указать момент выполнения любого цикла шины по отношению к моменту прекращения записи информации в блок 5 оперативной памяти, Поскольку запись информации в блок 5 оперативной памяти прекращается одновременно во всех устройствах, можно восстановить реальную последовательность выполнения различными процессорами отлаживаемого устройства циклов шины.

Возможный вариант реализации блока

1 представлен на фиг.2 ° В его состав входят мультиплексор 21, выходы которого подключены к адресным входам блока 22 оперативной памяти,. выход которого подключен к выходу блока, вход чтения — к входу чтения блока, вход записи " к входу записи блока, а информационный вход — к информационному входу блока, первая группа информационных входов мультиплексора

21 соединена с первыми адресными входами блока, вторая группа информационных входов — с вторыми адресньяи входами блока, а управляющий вход— с управляющим входом блока.

Блок 1 работает следующим образом.

На этапе управления сигнал на управляющем входе мультиплексора 21 имеет уровень лог."О", разрешая прохождение кодов на выход мультиплексора с его первой группы входов, эти коды являются адресами, по которым управляющая ЭВМ записывает в блок 22 оперативной памяти информацию, сопровождая ее управляющим сигналом по входу.20 записи. В.блок 22 оперативной памяти записывается единица по адресу прекращения трассировки и ноль †.по остальным. адресам.

На этапе трассировки сигнал на управляющем входе мультиплексора 21 принимает уровень лог."1" и на адресные входы блока 22 оперативной памяти поступают коды с вторых адресных входов узла сравнения. При появлении на этих адресных входах адреса, совпадающего с. заданным.в качестве условия прекращения трассировки,на выходе блока 22.оперативной памяти появляется сигнал уровня лог."1.". Чтение иэ блока 22 оперативной памяти производится при.напииии сигнала уровня лог,."1" на входе чтения узла сравнения.

Формула изобретения

Устройство для отладки многопроцессорных систем, содержащее одноразрядный блок оперативной памяти, элемент

НЕ, первый триггер, первый счетчик импульсов, мультиплексор и блок оперативной памяти, причем первая группа адресных входов устройства соединена с первой группой адресных вхо» дов одноразрядного блока оперативной памяти и с первой группой информационных входов мультиплексора, группа выходов которого соединена с группой адресных входов блока оперативной памяти, информационные выходы блока оперативной памяти через двунаправленную информационную магистраль сае

1446624

Составитель Сигалов

Техред Л.Олийнык

Редактор А,Воронич

Корректор В.Гирняк

Заказ 6748/53 Тираж 704 Подписное

ВЦИИПИ Государственного комитета по изобретениям и открытиям при ГК!!Т СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. ужгород, ул . Проектная, 4

5 динены с группой информационных входов одноразрядного блока оперативной памяти и с информационными входамивыходами устройства выход одноразУ

5 рядного блока оперативной памяти через элемент НЕ соединен с выходом запроса прерывания устройства, информационный вход триггера соединен с шиной единичного потенциала устройст- 10 на, а выход триггера соединен с входом установки в "О" первого счетчика импульсов, группа информационных выходов которого соединена с второй группой информационных входов мульти- 15 плексора, нход установки режима устройства соединен с тактовым входом триггера, с входом обращения одноразрядного блока оперативной памяти и управляющим входом мультиплексора, нход признака чтения устройства соединен с входом чтения блока оперативной памяти, вторая группа адресных входов устройства соединена со второй группой адресных входов одноразрядно- рб го блока оперативной памяти и с первой группой информационных входов блока оперативной памяти, группа ин" формационных входов устройства соединена с второй группой информационных входов блока оперативной памяти, вход признака записи устройства соединен

6 с входом записи одноразрядного блока оперативной памяти, о т л и ч а ю— щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет фиксации длительности циклов шины межпроцессорной магистрали, в устройство нведены элемент ИЛИ, схема сравнения и второй счетчик импульсов, причем выход одноразрядного блока оперативной памяти и выход элемента НЕ соединены соответственно с прямым и инверсным входами элемента

ИЛИ, выход которого соединен с входом установки нуля триггера, вход цикла шины устройства соединен с первым входом схемы сравнения и с входом чтения одноразрядного блока оперативной памяти, выход равенства схемы сравнения соединен со счетным входом первого счетчика импульсов, входом записи второго счетчика импульсов и с входом записи блока оперативной памяти, информационные выходы и выход переполнения второго счетчика импульсов соединены соответственно с третьей группой информационных входов блока оперативной памяти и с вторым нходом схемы сравнения, синхровход устройства соединен со счетным входом второго счетчика импульсов.