Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам с коррекцией ошибок, и может быть использовано при создании устройств памяти в интегральном исполнении. Цель изобретения - повьшение надежности. Устройство содержит основной 1 и дополнительный 2 блоки памяти, блок 3 кодирования , блок 4 управления, блок 5 декодирования, мажоритарные элементы 7 6, информагтионные входы 7, икформационные выходы 8, входы 9 обращения, - коммутаторы 10 и вход 11 контроля. При записи данных в блок 1 памяти одновременно форьтнруются блоком 3 контрольные коды, записываемые в блок 2 памяти. При считывании кодов из блоков 1 и 2 памяти в блоке 5 вычисляетсяпо двум различным формулам два значения каждого разряда информационного слова, которые поступают через соответствующие коммутаторы 10 на входы соответствующих мажоритарных элементов 6, на третьи входы которых поступает непосредственно считанный из блока 1 разряд слова На выходах 8 элементов 6 формируется информационное слово. В режиме контроля блока 1 на вход 11 подается разрешающий сигнал, блокирующий ра боту коммутаторов. На выходы элементов 6 поступает информационное слово, непосредственно считанное из блока 1, 2 ил. to

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!) ф G 1 ) С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ ССОР (2)) 4247932/24-24 (22) 22.05.87 (46) 23,12,88. Бюл. N - 47 (72) С,А.Фастов, С.В.Сушко и А.И.Березенко (53) 681.327.6 (088 ° 8) (56) Хан О, Быстродействующие ЗУПВ со встроенными схемами исправления ошибок. — Злектроника, 1984, У 18.

Авторское свидетельство СССР

У 1073799, кл . С 11 С 29/00, 1984. (54) ЗАПОМИНАИЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ О)1)ИБОК (57) Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам с коррекцией ошибок, и может быть использовано при создании устройств памяти в интегральном исполнении. Цель изобретения — повышение надежности. Устройство содержит основной 1 и дополнительный 2 блоки памяти, блок 3 кодирования, блок 4 управления, блок 5 декодирования, мажоритарные элементы

ÄÄSUÄÄ 1446656 А1

6, информационные входы 7, информа— ционные выходы 8, входы 9 обращения,коммутаторы 10 и вход 11 контроля, При записи данных в блок 1 памяти одновременна формируются блоком 3 контрольные кодЫ, записываемые в блок 2 памяти. При считывании кодов из блоков 1 и 2 памяти в блоке 5 вычисляется по двум различным формулам два значения каждого разряда информационного слова, которые поступают через соответствующие коммутаторы

10 на входы соответствующих мажоритарных элементов 6, на третьи входы которых поступает непосредственно считанный из блока 1 разряд слова.

На выходах 8 элементов 6 формируется информационное слово. В реяиме контроля блока 1 на вход !1 подается разрешающий сигнал, блокирующий работу коммутаторов. На выходы элементов

6 поступает информационное слово, непосредственно считанное из блока 1.

2 ил.

1446656

Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам с коррекцией ошибок и может быть использовано при

5 создании устройств памяти в интегральном исполнении.

Целью изобретения является повышение надежности запоминающего устройства, 10

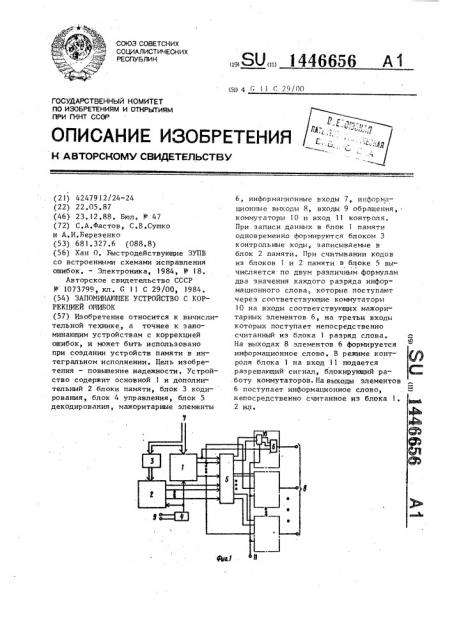

На фиг.1 показана структурная схема запоминающего устройства с коррекцией ошибок; на фиг.2 — пример реализации коммутатора.

Устройство содержит основной 1 и дополнительный 2 блоки памяти, блок

3 кодирования, блок 4 управления, блок 5 декодирования, мажоритарные . элементы 6, информационные входы 7 и выходы 8, входы 9 обращения, коммутаторы 1 0 и вход 1 1 контроля .

Коммутатор 10 содержит элемент

И 12, элемент HE 13 и элемент ИЛИ 14.

Устройство работает следующим об; разом. 25

Запоминающее устройство содержит средства коррекции однократных ошибок в словах данных, считываемых из основного блока 1 памяти. Дпя этого в режимах записи по входным данным, 30 поступающим на вход 7 устройства, блок 3 кодирования формирует конт— рольные разряды, которые записывают— . ся в дополнительный блок 2 памяти.

В качестве корректирующего кода в предложенном устройстве используется код Хэмминга. Работой основного 1 и дополнительного 2 блоков памяти управляет блок 4 управления. Помимо формирования сигналов разрешения gp записи и считывания этот блок обес— печивает также необходимую задержку сигнала записи, учитывающую задержку срабатывания блока 3 кодирования.

В режимах считывания блок 5 декодирования обеспечивает расчет по уравнениям кодирующей,матрицы двух независимых значений каждого информационного бита данных, а каждый мажоритарный элемент 6 по этим. двум значениям и значению бита, полученному при непосредственном считывании из блока 1 памяти, пропускает на выход 8 сигнал, соответствующий истинному значению бита данных, 55

Для .сохранения высокой надежности работы запоминающих устройств со встроенной коррекцией ошибок необходимо как на этапе их изготовления, так и при последующей эксплуатации выявлять и заменять устройства, содержащие неисправные элементы памяти.

В рабочих режимах считывания на входе 11 контроля поддерживается

1! 11 состояние логического 0 и элементы

l 2 и ИЛИ 1 4 коммутаторов 1 0 пр опускают на входы мажоритарных эл ементов 6 сигналы с выходов блока 5 декодирования, т, е . на инфо рм ацион— ны е выходы 8 устройства поступают данные основного блока 1 чамя ти с и спр авл ен ными одиночными ош иб к ами .

В режиме контроля, когда вводитс я запрет коррекции ошибок, на входе

1 1 поддерживается состояние л о гич е ск ой " 1 . Зто означает, ч т о на вторых и тр е тьи х входах мажоритарных элементов 6 у ст ан авлив ают ся состояния, соответственно, логических " 1 " и 0 независимо о т состояний сигналов на выходах блока 5 декодирования .

В таких случаях состояния выходных сигналов: м ажоритарных элементов 6 определяются сигналами с третьих вх одов „ т . е . сигналами основного блока

1 памяти . Следовательно, информация с выходо в блока 1 памяти проходит на информационные выходы 8 у с тр ойс тва б е з изменения, ч т о позволяет о сущес т вить контроль р аб о то спо соб но с ти основного блока 1 памяти . формулаизобретения

Запоминающее устройство с коррекцией ошибок, содержащее основной и дополнительный блоки памяти, блок кодирования, блок декодирования, мажоритарные элементы и блок управления, входы которого являются входами обращения устройства, выход блока управления подключен к входам обращения основного и дополнительного блоков памяти, информационные входы основного блока памяти являются информационными входами устройства и подключены к входам блока кодирования, выходы которого подключены к информационным входам дополнительного блока памяти, выходы которого подключены к входам первой группы блока декодирования, входы второй группы которого подключены к выходам основного блока памяти и к одним из входов соответствующих мажоритарных элементов, выходы которых являются информа з )446656 4 ционными выходами устройства, о т— дирования, управляющие входы коммутал и ч а ю щ е е с я тем, что, с торов объединены и являются входом целью повьппения надежности устройства, контроля устройства, выходы коммутаоно содержит коммутаторы, информа- торов подключены к другим входам ционные входы которых подключены к соответствующих мажоритарных элеменсоответствующим выходам блока деко- тов, Составитель С.Шустенко

Редактор В.Данко Техред М. Ходанич Корректор Л.Патай

Заказ 6752/55 Тираж 590 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при Г1ЯТ СССР

133035, Москва, Ж-35, Раущская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4