Устройство кодирования блоковых кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технике связи. Его использование в системах хранения. обработки и передачи информации позволяет упростить устройство и расширить область его применения за счет тэбеспечения возможности кодирования нелинейных кодов. Устройство содержит буферные регистры 1, группу 3 блоков полусумматоров. группу 5 умножителей в поле Галуа и блок 7 ключей. Благодаря введению буферных регистров 2, группы 4 блоков полусумматоров, группы 6 умножителей в поле Галуа, блока 8 ключей, блоков 9 и 10 коммутаторов блока 1 управления и преобразователя 12 кодов в устройстве обеспечивается упрощение структуры и появляется возможность кодирования не только линейных, но и нелинейных кодов. 1 з.п. ф-лы, 2 ил. о U (Л

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„» 144841

А1 с5о 4 Н 03 М 13/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1Яf

1Х2

:Ь

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4238056/24-24 (22) 04. 05. 87 (46) 30.12.88. Бюл, У 48 (72) В.А. Тузиков, Ю.П, Нятошин, В.Г. Ивочкин, С.Л. Портной,В.,А, Зиновьев и А.М. Барг (53) 681,325(088.8) (56) Авторское свидетельство СССР

Ф 1390801, кл, Н 03 M 13/02, 1985.

Питерсон У., Уэлдон К. Коды, исправляющие ошибки. М.: Мир, 1976, с. 254, рис ° 8.2. (54} УСТРОИСТВО КОДИРОВАНИЯ БЛОКОВЫХ

КОДОВ (57) Изобретение относится к вычислительной технике и технике связи. его использование в системах хранения, обработки и передачи информации позволяет упростить устройство и расширить область его применения за счет обеспечения возможности кодирования нелинейных кодов. Устройство содержит буферные регистры !, группу 3 блоков полусумматоров. группу 5 умножителей в поле Галуа и блок 7 ключей. Благодаря введению буферных регистров 2, группы 4 блоков полусумматоров, группы 6 умножителей в поле Галуа, блока

8 ключей, блоков 9 и 10 коммутаторов блока ll управления и преобразователя

12 кодов в устройстве обеспечивается упрощение структуры и появляется возможность кодирования не только линейных, но и нелинейньгх кодов.

1 з.п, ф-лы, 2 ил.

14484!4

Изобретение относится к вычислительной технике и технике связи и может использоваться в системах хранения,обработки и передачи цифровой ин- 5 формации, в том числе по линиям связи с многопозиционной модуляцией. .Цель изобретения — упрощение устройства и расширение области его применения за счет обеспечения воэмож- 10 ности кодирования нелинейных кодов.

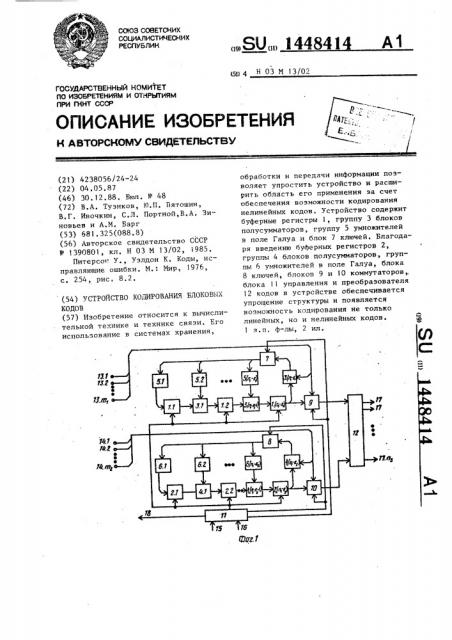

На фиг. I изображена блок-схема предлагаемого устройства кодирования блоковых кодов, нафиг. 2 — функциональная схема блока управления. 15

Устройство кодирования блоковых кодов (фиг. 1) содержит первый— (п1-К „)-ый m1-разрядные буферные регистры 1 (m 1 -разрядность символов первого входного (и „, 1(„ d,)-кода), 20 первый — (и <-К )-ый m<-разрядные буферные регистры 2 (m -разрядность символов второго входного (и„, К, d<)-кода), первую и вторую группы 3 и 4 блоков полусумматоров, первую и вторую группы 5 и б умножителей в поле Галуа, первый и второй блоки 7 и

8 ключей, первый и второй блоки 9 и

10 коммутаторов, блок 11 управления и преобразователь 12 кодов, На фгвг. 1 обозначены первые и вторые информационные входы 13 и 14, тактовый вход

15, вход 16 импульса начала информа ции, информационные выходы 1?, выход

18 импульса запроса. 35

Блоки полусумматоров групп 3 и. 4 содержат каждый соответственно m, и ш полусумматоров.

Умножитель в поле Галуа групп 5 40 и 6 представляют собой преобразователи кодов на основе ПЗУ с жестким программированием, на выходе которых формируются коды, равные произведению входного входа на собтветствующий элемент поля GF(2 " ) - для группы

5 или поля GF(2 ) — для группы 6.

Блок 11 управления (фиг. 2) содержит триггер 19, элемент И 20, первый— третий счетчики 21-23. На фиг. 2 обозначены первый и второй входы 24

50 и 25 и первый — четвертый выходы 2629. Преобразователь !2 кодов может быть реализован на ПЗУ с жестким программированием. Счетчики 21-23

55 имеют коэффициенты пересчета соответственно К, К < и и„, причем после переполнения счетчика счет в нем останавливается.

Работу устройства кодирования блоковых кодов рассмотрим на примере конструкции, состоящей из блоков, кодирующих информацию следующими кодами: код Рида-Соломона РС, (15, 11, 5) над полем Галуа СР(2 "), т.е. n„=

=15, К„=ll, d, 5, m =4 (первый входной код); код Рида-Соломона РС (15, 13, 3) над полем Галуа GF(24), т.е. п,=15, К =13, d<=3, m<=4 (второй входной код); нелинейный код Нордстрома-Робинсона Н-Р (16, 8, 6), т.е. п =16, Кд=ш1+та =8, 6 =6 (выходной код); ортогональный код, вложенный в код Н-P (16, 4, 8), т.е. пв=16, К -òï =4, dä=8 (выходной код).

Представление ноля Галуа GF(2 ) в виде двоичных г инейных комбинаций по нормальному базису ъ выглядит следующим образом:

Устройство кодирования блоков кодов работает следующим образом.

Поступающий на вход 16 устройства импульс начала информации подается на второй вход 19 блока 11 управления, где обнуляет счетчики 21-23 и перебрасывает триггер 19 в состояние логической единицы. Сигнал логической единицы с выхода триггера 19 поступает на вход элемента И 20 и дает разрешение прохождению тактовых импульсов, поступающих с входа 15 устройст. ва на первый вход 18 блока ll управления.

С выхода элемента И 20 пятнадцать тактовых импульсов поступают на входы обнуления счетчиков 21-23. С выхо„о

@2 з

o( (6 (7, в (9 со (11 (1В (13, и 1В с/

1 1

I 0

О 1

1 1

О 0 ! О

G О

0 0

1 О

0 1

О 1

О 1 ! 1 !

О О 4 (В

1 1

О 0

О О

О 1 ! О ! О

I 0

l 1

О

1 1

О I

1 О

I 1

О О

О I

О О

25

0101

001

0110

1 1 1 1

1 1 00

1001

Приведем вспомогательные последовательности h;; i=(l, 8)

0000 0000 0000 0000

1 110111011010010

h,-101111100100

101010011100

110 г

111

h =

h4=

5

1 6

1110110110111000

h = т

011101111110

h=000

3 14484 да счетчика 21 импульс длигельностью в одиннадцать периодов тактовой частоты поступает на входы управления блоков 7 и 9. С выхода счетчика 22

5 импульс длительностью в тринадцать периодов тактовой частоты поступает на входы управления блоков 8 и 10.

С выхода счетчика 23 импульс запроса возвращает триггер 19 в нулевое состояние, прекращая прохождение тактовых импульсов через элемент И 20, при этом импульс запроса поступает на выход 29 блока 11 управления и на выход 18 устройства. 15

С поступлением импульса начала информации на входы 13 и 14 поступает двоичная информация по четырем разрядам в параллельном виде с частотой тактовых импульсов, причем на входы 13 двоичная информация поступает в течение одиннадцати тактов, а на входы 14 — в течение тринадцати тактов, Для рассматриваемого случая блоки

3, 5, 7 и 9 соединены в соответствии с порождающим полиномом кода РС,:.

8, (х}=х4+ х +J х +8 х+ i 30 и осуществляют формирование четырех избыточных символов кода РС1.

В течение первых одиннадцати тактов входная информация с входов 13 поступает через замкнутые ключи блока

7 на входы умножителей группы 5 и одновременно через блок 9 на соответствующие входы преобразователя 12 кодов. Сформированные четыре избыточных символа кода РС„ выдаются на соответствующие входы преобразователя 12 кодов через блок 9 следом за информационными символами, при этом ключи блока 7 разомкнуты.

14

Блоки 2, 4-, 6, 8 и 10 в этом случае соединены в соответствии с порождающим полиномом кода РС : а1(х) +Ы" + Ы и осуществляют формирование двух избыточных символов кода РС .

В течение первых тринадцати тактов входная информация со входов 14 поступает через замкнутые ключи блока

9 на входы умножителей группы 6 и одновременно через блок 10 на соответствующие входы преобразователя 12 кодов. Сформированные два избыточных символа кода PC выдаются на соответствующие входы преобразователя 12 кодов через блок 10 следом за информационными символами, при этом ключи

1 блока 9 разомкнуты.

Преобразователь !2 кодов представ" ляет собой для данного случая преобразователь восьмиразрядной двоичной информации в шестнадцатиразрядные кодовые слова нелинейного кода Н-P (16, 8, 6) и вложенного в него ортогонального кода (16, 4, 8).

Кодовые последовательности кода . (16, 4, 8) представляются следующей матрицей Н Н,Н„Н Н

Н„Н,Н„Н1.

Н,Н,Н,Н „

1448414

Кодовые слова нелинейного кода с вложенным ортогональным кодом образуются таким образом:

8 ф 5

h;® H или,> h;0 H

i=i. 3 14

i-в1

rgb h — инверсные последователь1 ности h l, t0

9 — суммирование строк матрицы

Н с последовательностью h; или h..

Прономеруем разряды двоичных последовательностей h h; и столбцы матрицы Н слева направо с первого 15 по шестнадцатый, Тогда выбор одной из строк матрицы Н, определяется двоичным набором на соответствующих входах преобразователя 12 кодов, совпадаюшим с од- 20 ним из двоичных наборов во втором, третьем, пятом и тринадцатом столбцах матрицы Н

Выбор одной из последовательностей

h; или h; определяется двоичным на бором на соответствующих входах преобразователя 12 кодов, совпадающим с одним из двоичных наборов в девя— том, десятом, одиннадцатом и двенадцатом разрядах последовательностей 30

h; или h;.

Так с каждым тактом поступления информации на входы 13 и 14 устройства с выходов 17 снимается шестнадцать разрядов практически без задержки, если не учитывать задержки элементов.

Весь двоичный массив информации из 96 разрядов, поступающий на входы устройства, кодируется за пятнадцать тактов и получается (и, k, Й) код (240, 9б, 24).

Таким образом обеспечивается упрощение устройства и расширение области его применения за счет многокаскадного построения устройства с использованием коротких линейных и нелинейных кодов. Кроме того, предлагаемое устройство позволяет кодировать информацию, поступающую íà его входы, 50 как в старт-стопном, так и в циклическом режимах и обеспечивает более высокую кодовую скорость К-k/n передачи при одинаковом числе информа55 ционных символов и расстоянии Хемминга.

Предлагаемое устройство обеспечивает также выдачу выходной кодированной информации практически без задержки по отношению к входной, что дает дополнительное преимущество при использовании устройства в многопозиционных системах связи. формулаизобретения

1, Устройство кодирования блоковых кодов, содержащее первый — (п -К „)-й m „-разрядные буферные регистры (и,, К „ — соответственно общее число символов и число информационных символов первого входного кода; m разрядность Символов первого входного кода, выходы которых соединены с первыми входами одноименных блоков полусумматоров первой группы, первый блок ключей, выходы которого через первый - (п,-К „)-й умножители в поле

Галуа первой группы подключены соответственно к информационным входам первого m „-разрядного буферного регистра и вторым входам первого— (n Ê,-l)-ro блоков полусумматоров первой группы, выходы которых соединены с информационными входами соответственно второго — (и -K,)-го m— разрядных буферных регистров, вторые входы (n,-1,)-ro блока полусумматоров первой группы являются первыми информационными входами устройства, о т л и ч а ю щ е е. с я тем, что, с целью упрощения устройства и расширения области его применения за счет обеспечения возможности кодирования нелинейных кодов, в устройство введены первый — (n -К Д-" m -разрядйые буферные регистры (К вЂ” число информационных символов второго входного кода; m<, — размерность символов второго входного кода, первый — (n„-К )-й блоки полусумматоров второй группы, первый — (и „-K )-й умножители в поле Галуа второй группы, второй блок ключей, первый и второй блоки коммутаторов, преобразователь кодов и блок управления, выходы (n.,— -К,) — го блока полусумматоров первой группы соединены с информационными входами первого блока ключей, первые и вторые информационные входы первого блока коммутаторов подключены соответственно к выходам (и „-K,)-ro

m ðàçðÿäíîão буферного регистра и первым информационным входам устройства, выходы первого — (n, — Ê -1)-го

m <-разрядных буферных регистров соеУиг. 2

Составитель О. Ревинский

Редактор Т. Парфенова Техред М.Дидык Корректор М. Максимищинец

Заказ 6852/56 Тираж 929 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

14484 динены с первыми входами одноименных блоков полусумматоров второй группы, выходы которых подключены к информационным входам соответственно второго (п -К )-rom -разрядных буферных регистров, выходы (n,-K )-ro ш -разрядного буферного регистра соединены с первыми входами одноименного блока полусумматоров второй группы и первы- rð ми информационными входами второго блока коммутаторов, вторые информационные входы которого объединены с соответствующими вторыми входами (n„ K<)-го блока полусумматоров второй группы и являются вторыми информационными входами устройства, выходы (п -К )"го блока полусумматоров второй группы соединены с информационными входами второго блока ключей, вы- 2р ходы которого через первый — (и,—

-К )-й умножители в поле Галуа второй группы подключены соответственно к первым информационным входам первого

m -разрядного буферного регистра и 25 первого - (и „-K l)-го блоков полусумматоров второй группы, первый и второй входы блока управления являются соответственно тактовым входом и входом импульса начала информации 3р устройства, первый выход блока управ-ъ ления подключен к тактовым входам

l4 8 всех буферных регистров, второй и третий выходы блока управления соединены с управляющими входами соответственно первых и вторых блоков ключей и коммутаторов, выходы первого и второго блоков коммутаторов соединены с первыми и вторыми входами преобразователя кодов, выходы которого являются информационными выходами устройства, четвертый выход блока управления является выходом импульса запроса устройства.

2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления содержит триггер, первыйтретий счетчики и элемент И, первый вход которого является первым входом блока, входы обнчления первого - третьего счетчиков и триггера объединены и являются вторым входом блока, выход триггера соединен с вторым входом элемента И, выход которого подключен к счетным входам первого— третьего счетчиков и является первым выходом блока, выходы переполнения первого и второго счетчиков являются соответственно вторым и третьим выходами блока, выход переполнения третьего счетчика соединен с установочным входом триггера и является четвертым выходом блока.