Устройство для формирования сигналов управления приемного факсимильного аппарата

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам факсимильной связи и может быть использовано для приемопередачи полутонового изображения. Цель изобретения - расширение функциональных возможностей путем обеспечения работы в режиме дистанционного управления приемным факсимильным аппаратом и повышение надежности. Устройство для формирования сигналов управления приемного факсимильного аппарата содержит соединенные соответствующим образом детектор 1, компаратор 2, блок 3 для вьделения частоты, формирователь 4 импульса, блок 5 для определения окончания передачиj два элемента И 6 и 7, элемент ИЛИ 8, первый 9 и второй 12-счетчики, первый 10 и второй 11 дешифраторы, делитель 13 частоты , задающий генератор 14, блок 15 для фазирования, коммутатор 16 и модулятор 17. При этом обеспечиваются снижение влияния на работу устройства постороннего корреспондента и формирование на выходе устройства амплитудно-модулированного сигнала, который может быть передан, например, по стандартному каналу тональной частоты для управления одновременно группы приемных факсимильных аппаратов . 3 ил. 2 (Л

СОЮЗ СОВЕТСКИХ . СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„14501 (51) 4 " 04 М 1 36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСЧОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 3936501/24-09 (22) 26.07.85 (46) 07.01.89. Бюп. Р 1. (71) Научно-производственное объединение космических исследований АН

АЗССР (72) Т.К.Исмаилов, Т.И.Низамов, P.À.ÌàêàðÿH, P.À.Øåéõoâ, P.К.Кули— заде и Б.М.Султанов (53) 621.397.3 (088.8) (56) Авторское свидетельство СССР

У 995370, кл. Н 01 N 1/36, 1981. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ УПРАВЛЕНИЯ ПРИЕМНОГО ФАКСИМИЛЬНОГО АППАРАТА (57) Изобретение относится к устройствам факсимильной связи и может быть использовано для приемопередачи полутонового изображения. Цель изобретения — расширение функциональных воэможностей путем обеспечения работы в режиме дистанционного управления приемным факсимильным аппаратом и повышение надежности. Устройство для формирования сигналов управления приемного факсимильного аппарата содержит соединенные соответствующим образам детектор 1, компаратор 2, блок 3 для выделения частоты, формирователь

4 импульса, блок 5 для определения окончания передачи, два элемента

И 6 и 7, элемент ИЛИ 8, первый 9 и второй 12 счетчики, первый 10 и второй 11 дешифраторы, делитель 13 частоты, задающий генератор 14, блок

15 для фазирования, коммутатор 16 и модулятор 17. При этом обеспечиваются снижение влияния на работу устройства постороннего корреспондента и формирование на выходе устройства амплитудно-модулированного сигнала, который может быть передан, например, по стандартному каналу тональной частоты для управления одновременно группы приемных факсимильных аппаратов, 3 ил, 1450133

Изобретение относится к устройст,вам факсимильной связи и может быть использовано для приемопередачи полутонового изображения.

Цель изобретения — расширение функциональных возможностей путем обеспечения работы в режиме дистанционного управления приемным факсимильным аппаратом и повышение надежности. 10

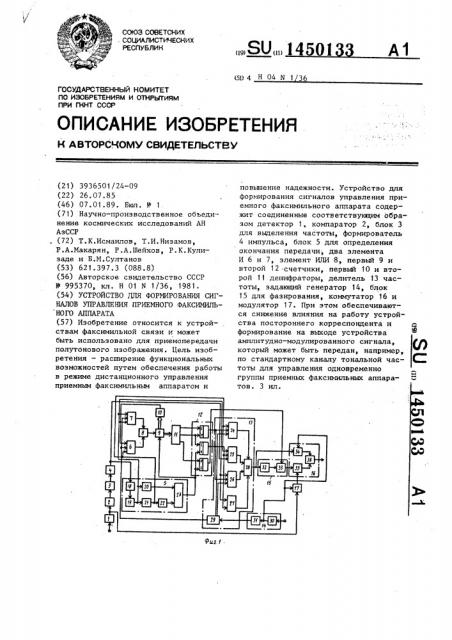

На фиг. 1 изображена функциональная электрическая схема устройства для формирования сигналов управления приемного факсимильного аппарата; на фиг. 2 и 3 — временные диаграммь, по- 15 ясняющие работу устройства.

Устройство для формирования сигналов управления приемного факсимильно, го аппарата (фиг. 1) содержит последовательно соединенные детектор 1, ком- 20 !

;паратор 2, блок 3 для выделения частоты, формирователь 4 импульса и блок

: 5 для определения окончания передачи, второй и третий выходы которого соот:, ветственно через первый элемент И 6, и через второй элемент И 7 подключены к входам элемента KIH 8, выход которого соединен с первым входом первого счетчика 9, первый выход которого через первый дешифратор 10 сое- 30 динен со вторыми входами первого и . второго элементов И б и 7, а второй выход соединен с входом второго дешифратора 11, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам второго счетчика 12, первый и второй выходы которого подключены соответственно к первому и второму входам делителя 13 частоты, первый 40 выход которого соединен с третьими входами первого и второго элементов

И 6 и 7, третий вход делителя 13 частоты соединен с первым выходом задающего генератора 14, блок 15 для фа- 45 зирования, выход которого подключен к второму входу коммутатора 16, третий вход которого соединен с выходом модулятора 17, первый вход которого соединен с выходом детектора 1, а второй вход соединен с четвертым входом коммутатора 16 и со вторым вьмодом задающего генератора 14, причем выход блока 5 для определения окончания передачи соединен с четвертым входом второго счетчика 12 и со вторым входом первого счетчика 9, а первый вход блока 15 для фазирования соединен с первым входом коммутатора 16 и со вторым выходом делителя

13 частоты, четвертый вход, которого соединен со вторым выходом блока 5 для определения окончания передачи, третий выход которого подключен к пятому входу делителя 13 частоты, шестой вход которого соединен с выходом формирователя 4 импульса, а третий выход второго счетчика 12 подключен к второму входу блока 15 для фазирования.

Блок 5 для определения окончания передачи содержит последовательно включенные формирователь 18 линейно изменяющегося напряжения, вход сброса которого является входом блока, и компаратор 19, выход которого соединен с входом первого формирователя

20 короткого импульса и через первый элемент НЕ 21 соединен с входом второго формирователя 22 короткого импульса, выходы первого 20 и второго

22 формирователей короткого импульса соединены соответственно с входами первого дополнительного элемента

ИЛИ 23, выход которого, а также выход первого элемента НЕ 21 и выход компаратора 19 являются соответственно первым, вторым и третьим выходами блока.

Второй счетчик 12 содержит три

RS-триггера, причем R-вход первого триггера соединен с S-входом второго, R-вход которого соединен c R-входом третьего RS-триггера, S-входы первого, второго и третьего RS-триггеров являются соответственно первым, вторым и третьим входами второго счетчика 12, четвертым входом которого является R-вход третьего RS-триггера, а прямые выходы RS-триггеров являются первым, вторым и третьим выходами второго счетчика 12.

Делитель 13 частоты содержит четыре дополнительных элемента И 24-27, второй дополнительный элемент ИЛИ 28 и преобразователь 29 частоты, причем первые входы первого и второго дополнительных элементов И 24 и 25 соединены между собой, вторые входы первого и третьего дополнительных элементов И 24 и 26 соединены между собой, вторые входы второго и четвертого дополнительных элементов И 25 и 27 также соединены между собой, первые входы третьего и четвертого дополнительных элементов И 26 и 27 соединены между собой, третьи входы первого и третьего дополнительных элемен3 14501 тон И 24 и 26 соединены соответственно со вторым и третьим выходами преобразователя 29 частоты, первый выход которого является первым выходом де5 лителя 13 частоты, вторым выходом которого является выход второго дополнительного элемента ИЛИ 28, вторые входы первого и второго дополнительных элементов И 24 и 25 являются пер- р вым и вторым входами делителя 13 частоты, третьим входом которого является вход преобразователя 29 частоты, четвертым и пятым входом делителя 13 частоты являются первые входы соответственно второго и четвертого дополнительных элементов И 25 и 27, а шестым входом — третий вход второго дополнительного элемента И 25.

Задающий генератор 14 содержит по- 2р следовательно включенные умножитель

30 частоты и дополнительный компаратор 31, вход и выход которого являются соответственно вторым и первым выходом задающего генератора 14, а 25 входом умножителя 30 частоты является выход синхронизации приемного факсимильного аппарата. Блох 15 для фазирования содержит второй элемент

НЕ 32, выход которого соединен с пер- 30 вым входом пятого дополнительного элемента И 33, второй вход которого является вторым входом блока 15 для фазирования, первым входом которого является вход второго элемента HE 32.

Коммутатор 16 содержит два аналоговых ключа 34 и 35, выходы которых через сумматор 36 соединены с выходом коммутатора 16. Первым и.вторым входами коммутатора являются первые вхо- 4р ды первого 34 и второго 35 аналоговых ключей. Второй вход первого аналогового ключа 34 является третьим входом коммутатора 16, четвертым входом которого является второй вход 4б второго аналогового ключа 35.

Устройство работает следующим образом.

В исходном состоянии до поступления входного сигнала напряжение на выходе формирователя 18 линейно изменяющегося напряжения (фиг.1) блока 5 для определения окончания передачи превышает порог срабатывания компаратора 19, на выходе которого напряжение при этом соответствует уровню логической "1", а на выходе первого элемента НЕ 21 — уровню логического

"0". Такое состояние выходов компара33

4 тора 19 и первого элемента HE 21 соответствует режиму Автоматический останов".

Синусоидальный сигнал с выхода

"Синхронизация приемного факсимильного аппарата поступает на вход задающего генератора 14, где, он удваивается умножителем 30 частоты, обеспечивая несущую частоту, которая подается на вторые входы первого аналогового ключа 34 и модулятора 17, и, преобразовавшись дополнительным компаратором 31 в импульсы прямоугольной формы, подается на вход преобразователя 29 частоты, обеспечивая на его первом выходе импульсы с частотой

1 Гц, на втором выходе частоту, соответствующую выбору шага, а на третьем выходе частоту, соответствующую режиму "Автоматический останов".

При поступлении на вход устройства входного сигнала (фиг. 2а) на выходе детектора 1 выделяется видеосигнал (фиг.2б), состоящий из кодового участка с определенной частотой изображения, который в модуляторе 17 модулирует несущую частоту, и одновременно, пройдя через компаратор 2, преобразуется в импульсы прямоугольной формы (фиг.2в) .

При соответствии частоты кодового участка видеосигнала закодированной частоте в блоке 3 для выделения частоты на выходе его формируются импульсы низкого активного уровня (фиг.2г), которые формирователем 4 импульса преобразуются в импульс фазовой длительности (фиг. 2д и фиг. За), частота повторения кодового участка входного сигнала определяет скорость приемного факсимильного аппарата.При этом напряжение на выходе формирователя

18 линейно изменяющегося напряжения блока 5 для определения окончания передачи станет ниже уровня срабатывания компаратора 19, на выходе которого устанавливается уровень логического "0", а на выходе первого элемента HE 21 — уровень логической "1" (фиг. Зб). Такое состояние выходов соответствует режиму "Автоматический пуск". При этом обеспечивается первое разрешение (фиг. Зд) на первый элемент И 6, первый и второй дополнительные элементы И 24 и 25 и запрещается прохождение через второй элемент И 7, третий и четвертый дополнительные элементы И 26, 27. На выходе второ5 14501 го формирователя 22 короткого импульса формируется короткий импульс, который через первый дополнительный элемент ИЛИ 23 сбрасывает первый счет5 чик 9, а также устанавливает в нуле— вое состояние второй и третий RS-триггеры второго счетчика 12 (фиг. 3е, ж), первый RS-триггер которого к моменту начала каждого режима находится в нулевом состоянии. При этом запрещается прохождение через первый, второй и пятый дополнительные элементы И 24, 25, 33. На выходе первого дешифратора !

10 устанавливается уровень логической "1", обеспечивающий второе разрешение на первом элементе И 6, которое позволяет прохождение импульсов с частотой 1 Гц с первого выхода преобразователя 29 частоты через первый эле- 2р мент И 6, элемент ИЛИ 8 на первый вход первого счетчика 9.

По первому импульсу, поступившему на вход первого счетчика 9, на первом выходе второго дешифратора 11 уста- 25 навливается уровень логической "1",который записывается в первый К$-триг. гер второго счетчика 12, обеспечивая второе разрешение (фиг. Зд) на первом дополнительном элементе И 24. Зр

При этом импульсы с частотой, соответствующей выбору шага (фиг.Зб), со второго выхода преобразователя

29 частоты через первый дополнительньй элемент И 24 и второй дополни35 тельный элемент ИЛИ 28 (фиг.Зз) поступают .на первый вход первого аналогового ключа 34, обеспечивая на его выходе чередование наличия и отсутствия несущей с частотой выбора шага, которая через сумматор 36 подается на выход устройства (фиг,Зи), связанного с входом приемного факси" мильного аппарата, обеспечивая автоматический выбор шага.

Через время, необходимое для выбора шага приемного факсимильного аппарата, первый счетчик 9 устанавливается в такое состояние,,при котором логическая "1" появляется на втором выходе второго дешифратора 11.

При этом обнуляется первый RS-триггер (фиг.Зд) второго счетчика 12, запрещая прохождение через первый дополнительный элемент И 24 импульсов выбора шага со второго выхода преобразователя 29 частоты, и записывается логическая "1" во второй RS-триггер (фиг. 3e) второго счетчика 12, 33 6 обеспечивая второе разрешение на втором дополнительном элементе И 25.

Импульсы фазовой длительности (фиг.3a), частота повторения которых определяет скорость приемного факсимильного аппарата, с выхода формирователя 4 импульса через открытый второй дополнительный элемент И 25, второй дополнительный элемент ИЛИ 28 (фиг. Зз) поступают на первый вход первого аналогового ключа 34, обеспечивая на его выходе чередование наличия и отсутствия несущей с частотой выбора скорости, которая через сумматор 36 подается на выход устройства (фиг. Зи), обеспечивая включение, автоматический выбор скорости и фазирование приемного факсимильного аппарата.

Через время, необходимое для автоматическогб выбора скорости и фазирования приемного факсимильного аппарата, первый счетчик 9 устанавливается в такое состояние, при котором логическая "1" появляется на третьем выходе второго дешифратора 11 и записывается в третий RS-триггер (фиг.Зж) второго счетчика 12. При этом разрешается прохождение через пятый дополнительный элемент И 33, а так как второй RS-триггер второго счетчика

12 не изменяет своего состояния (фиг. 3e), то импульсы фазовой длительности с выхода второго дополнительного элемента ИЛИ 28 (фиг. Зз) продолжают поступать на первьй аналоговый ключ 34, обеспечивая передачу фазовых импульсов, а через второй элемент НЕ 32, открытый пятый дополнительный элемент И 33 поступает на первый вход второго аналогового ключа 35 запрещая вывод изображения на время прохождения фазовых импульсов, обеспечивая фазированньй вывод изображения.

С момента записи изображения очередным импульсом, поступающим на первый счетчик 9, на выходе первого дешифратора 10 устанавливается уровень логического "0", запрещающий прохождение через первый элемент И 6 импульсов с частотой 1 Гц.

При прекращении подачи на вход устройства сигнала или при отличии частоты кодового участка входного сигнала от закодированной частоты в блоке 3 для выделения частоты на выходе последнего короткие импульсы

7 14501 будут отсутствовать, а на выходе формирователя 4 импульса устанавливается логический "0" (фиг.За). При этом напряжение на выходе формирователя 18 линейно изменяющегося напряжения блока 5 для определения окончания передачи превышает порог срабатывания компаратора 19, на выходе которого устанавливается уровень логической "1", 10 а на выходе первого элемента НЕ 21 уровень логического "0" (фиг. Зб).

Такое состояние выходов соответствует режиму "Автоматический останов" ° При этом обеспечивается первое разрешение 15 на второй элемент И 7, третий и четвертый дополнительные элементы И 26 и 27 и запрещается прохождение через первый элемент И 6, первый, второй дополнительные элементы И 24 и 25. 2р

На выходе первого формирователя 20 короткого импульса формируется короткий импульс, который через первый дополнительный элемент ИЛИ 23 сбрасывает первый счетчик 9, второй и тре- 25 тий RS-триггеры (фиг.Зе,ж) второго счетчика 12, первый RS-триггер которого также сброшен (фиг.Зд). При этом запрещается прохождение через третий, четвертый и пятый дополни- 30 тельные элементы И 26, 27 и 33.

На выходе первого дешифратора 10 устанавливается уровень логической

"1", обеспечивающий второе разрешение на втором элементе И 7, которое позволяет прохождение импульсов с частотой 1 Гц с первого выхода преобразователя 29 частоты через второй элемент И 7, элемент ИЛИ 8 на первый вход первого счетчика 9. Первый 4р счетчик 9, первый 10 и второй 11 дешифраторы, второй счетчик 12 работают по той же программе, что и в режиме "Автоматический пуск". Режим Автоматический останов" обеспечива- 45 ется в два этапа.

На первом этапе на первый вход первого счетчика 9 поступает первый импульс, на выходе первого RS-триггера.второго счетчика 12 устанавлива- 5О ется уровень логической "1" (фиг.Зд), обеспечивая второе разрешение на третьем дополнительном элементе И

26. При этом импульсы с частотой, соответствующей режиму автоматического останова, с третьего выхода преобразователя 29 частоты (фиг.3r) через третий дополнительный элемент И 26, элемент ИЛИ 28 (фиг.Зз) поступают на

33 8 первый вход первого аналогового ключа 34, обеспечивая на его выходе чередование наличия и отсутствия несущей с частотой, соответствующей режиму автоматического останова, которая через сумматор 36 подается ка выход устройства (фиг.Зи) .

На втором этапе, когда первый

RS-триггер второго счетчика 12 обнуляется (фиг.Зд), запрещая прохождение через третий дополнительный элемент

И 26, а второй RS-триггер второго счетчика 12 устанавливается в единич- ное состояние (фиг.Зе), на первый вход аналогового ключа 34 с выхода четвертого дополнительного элемента

И 27 через второй дополнительньп элемент ИЛИ 28 (фиг. Çз) поступает уровень логической "1", обеспечивая на его выходе непрерывный сигнал несущей, который через сумматор 36 выводится на выход устройства (фиг. Зи). Вторым этапом обеспечивается полный останов приемного факсимильного аппарата.

Цикл работы устройства завершается при появлении на выходе первого дешифратора 10 уровня логического "0", запрещающего прохождение импульсов через второй элемент И 7, При этом устройство переходит в ждущий режим.

Ф о р м у л а изобретения

Устройство для формирования сигналов управления приемного факсимильного аппарата, содержащее компаратор, формирователь импульса, блок для определения окончания передачи, первый элемент И, элемент ИЛИ, первый и второй счетчики, а также подключенные к выходам первого счетчика первый дешифратор, выход которого соединен с вторым входом первого элемента И, и второй дешифратор, первый, второй и третий выходы которого соединены соответственно с одноименными входами второго счетчика, четвертый вход которого подключен к первому выходу блока для определения окончания передачи, первый и второй выходы второго счетчика подключены соответственно к первому и второму входам делителя частоты, блок для фазирования и задающий генератор, первый выход которого соединен с третьим входом делителя частоты, о т л и— ч а ю щ е е с я тем, что, с целью расширения функциональных возможнос9 14501 тей путем обеспечения работы в режиме дистанционного управления приемным факсимильным аппаратом и повышения надежности, оно снабжено детектором, блоком для выделения частоты, вторым элементом И, модулятором и коммутатором, выход которого является выходом устройства, при этом основной од устройства через последователь, а соединенные детектор, компаратор, I ок для выделения частоты и формироатель импульса подключен к входу лока для определения окончания переачи, второй и третий выходы которого 1 оединены соответственно с первым вхоом первого элемента И, соединенного четвертым входом делителя частоты, первым входом второго элемента И, оединенного с пятым входом делителя рд астоты, шестой вход которого саедиен с выходом формирователя импуль33 )О са а первый выход — с третьими входами первого и второго элементов И, вторые входы которых соединены, а выходы через элемент ИЛИ подключены к первому входу первого счетчика, к второму входу которого подключен первый выход блока для определения окончания передачи, второй выход делителя частоты соединен с первыми входами коммутатора и блока для фазирования, второй вход которого соединен с третьим выходом второго счетчика, а выход подключен к второму входу коммутатора, к третьему входу которого подключен выход модулятора, первый вход которого соединен с выходом детектора, второй выход задающего генератора, вход которого является дополнительным входом устройства, соединен с вторым входом модулятора и четвертым входом коммутатора.!!Ц !Ц!!ИИИ

1450133

Тираж 660 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Редактор Г.Волкова

Заказ 6978/56

Составитель Б.Ефанов

ТехредЛ.Сердюкова Корректор М.Самборская