Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в многоканальных информахщонно-измерительных системах сбора информации. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит коммутаторы 2 и 17, счетчики 11 и 12, генератор импульсов 9, делитель частоты 10, элементы И 7,8 и 15, дешифратор 14, ключи 3, блок памяти 16, аналого-цифровой преобразователь АЦП 5, элемент задержки 13, триггер 6. Предлагаемое устройство позволяет автоматически определять частоту опроса информационных входов в зависимости от частотных характеристик входных сигналов. Указанное преимущество достигается тем, что в двухпороговом дискриминаторе 4 происходит сравнение значения вводимого сигнала со значением , которое он принимал в момент предьщущего аналого-цифрового преобразования . В случае равенства оцифровка сигнала не производится и устройство переходит к анализу входного сигнала следующего информационного входа, если же значение вводимого сигнала изменилось, то происходит его оцифровка в АЦП 5. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК дп 4 С 06 Р 3/05

P g, 3P g5g

E.. :.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21 ) 4261391! 24-24 ,(22) 15. 06. 87 (46) 15,01.89. Бюл. Ф 2 г. (71) Московский инженерно-физичес кий институт (72) А.И. Ерыгин, В,М. Рыбин, В.А. Сафоненко и К.В. Филипчук (53) 681.327.11(088.8) (56) Автор".кое свидетельство СССР

М 1290284, кл. G 06 F 3/00, 1985.

Авторское свидетельство СССР

Ф 1062683, кл. С 06 Г 3/05, 1982. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано в многоканальных информационно-измерительных системах сбора информации. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит коммутаторы 2 и 17, счетчики

ÄÄSUÄÄ 1451675 А1

11 и 12, генератор импульсов 9, делитель частоты 10, элементы И 7,8 и 15, дешифратор 14, ключи 3, блок памяти

16, аналого-цифровой преобразователь

АЦП 5, элемент задержки 13, триггер

6. Предлагаемое устройство позволяет автоматически определять частоту опроса информационных входов в зависимости от частотных характеристик входных сигналов. Указанное преимущество достигается тем, что в двухпороговом дискриминаторе 4 происходит сравнение значения вводимого сигнала со значением, которое он принимал в момент предыдущего аналого-цифрового преобразования. В случае равенства оцифровка сигнала не производится и устройство переходит к анализу входного сигнала следующего информационного входа, если же значение вводимого сигнала изменилось, то происходит его оцифровка в АЦП 5. 1 ил °

1451675

Изобретение относится к вычислительной технике и автдматике и может быть использовано в многоканальных информационно-измерительных системах,, входные аналоговые сигналы которых имеют нестационарно импульсную форму или требуют существенно различных частот опроса.

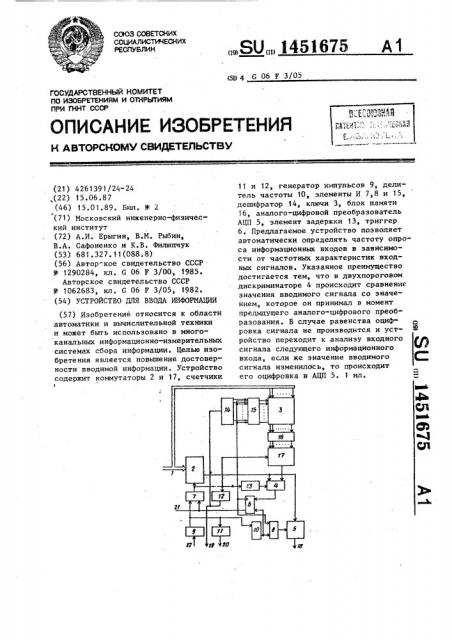

Цель изобретения — повышение достоверности вводимой информации за счет определения частоты опроса информационных входов, На чертеже изображена структурная схема устройства, 15

Устройство содержит входные информационные шины 1, первый коммутатор

2, ICJINMH 3, pB HOporOBbIA pHCKpHMHHB. тор 4, АЦП 5, триггер 6, первый 7 и второй 8 элементы И, генератор 9 импульсов, делитель 10 частоты, первый 11 и второй 12 счетчики, элемент

13 задержки, дешифратор 14, элементы

И группы 15, блок 16 памяти, второй коммутатор 17, а также входы и выходы 18-22 устройства.

Устройство работает следующим образом.

В исходном состоянии на входе 22, на выходах t8 вывода информации, вы- З0 ходах 19 адреса и выходах 20 информация отсутствует. На входах 1 присутствует. аналоговая информация. Ключи

3 находятся в разомкнутом состоянии, На прямом выходе триггера 6 присутствует высокий уровень { 1").

По входу 22 подается импульс на запуск устройства, который запускает генератор 9 импульсов. После этого на выходах генератора 9 импульсов и 40 делителя 10 частоты формируется последовательность импульсов соответственно высокой и низкой частоты.

С выхода генератора 9 импульсов первый импульс поступает на вход

45 первого элемента И 7, проходит через него (поскольку на другом входе первого элемента И. 7 высокий уровень поддерживает триггер 6) и поступает на управляющие входы первого 2 и второго 17 коммутаторов, вызывая. их сра5О батывание: первый из входов 1 подключается к первому входу дискриминатора 4, а первый элемент из блока 16 памяти — к второму входу двухпорогового дискримичатора 4. Импульс, вызвавший переключение коммутаторов, поступает также на вход второго счетчика 12 и через элемент задержки 13 на управляющий вход дискриминатора

4. По строб-импульсу дискриминатор 4 сравнивает значения сигналов, в данном случае он сравнивает значение на первом входе 1 и значение, хранящееся в первой ячейке блока 16 памяти (которое разряжено) . В .случае несовпадения сравниваемых сигналов (т.е. если сигнал на первом входе 1 отличен от нуля) на выходе двухпорогового дискриминатора 4 появляется высокий уровень ("1"), который опрокидывает триггер 6 (на прямом выходе триггера низкий уровень). Второй счетчик 12, который считает импульсы, поступающие с выхода первого элемента И 7, определяет номер коммутируемого информационного канала и выдает эту информацию на выходы 19 и на входы дешифратора 14. Первый счетчик 11, который считает импульсы, поступаюе щие с выхода генератора импульсов

9,, определяет время подключения информационного канала к АЦП 5 и выдает эту информацию на выходы 20.

Триггер 6 запирает первый элемент

И 7 и запрещает прохождение импульсов от генератора импульсов 9 на управляющие входы коммутаторов 2 и 17 и двухпороговorо дискриминатора 4, .На инверсном выходе триггера 6, который соединен. с входом второго элемента И 8, в это время поддерживается высокий уровень, благодаря чему второй элемент И 8 пропускает импульсы с, делителя 10 частоты. На первом выходе дешифратора 14 в это время поддерживается высокий уровень, поскольку второй счетчик 12 подает на дешифратор 14 информацию о том, что опрашивается первый информационный вход. Поскольку на инверсном выходе триггера 6 имеется высокий уровень, то и на выходе первой И группы 15 также присутствует высокий уровень, первый ключ 3 замыкается, первый элемент блока 16 памяти подключается к первому входу

1 и запоминает значение этого сигнала. Импульсы с генератора 9 импульсов попадают только на вход делителя

10 частоты и на вход первого счетчика

11. Это продолжается до появления на выходе делителя 10 частоты первого импульса, который проходит через второй элемент И 8 и запускает АЦП 5.

К входу АЦП 5 в этот момент подключен первый информационный вход, по

14516

50 синхроимпульсу с делителя 10 частоты начинается оцифровка информации.

После того, как АЦП 5 завершит работу, преобразованная информация с выхода АЦП 5 поступает на выходы 18 информации. Импульс с делителя 10 частоты попадает также на вход триггера 6, после чего на прямом выходе триггера 6 устанавливается сигнал вы-1О сокого уровня ("1") и импульсы с генератора 9 импульсов снова могут проходить через первый элемент И 7. На инверсном выходе триггера 6 устанавливается сигнал низкого уровня ("0"), 15 вследствие чего на выходе первого из элементов И группы 15 также устанавливается "0", первый ключ 3 размыкается, отключая первую ячейку блока памяти 16 от первого входа 1.

Очередной импульс с генератора 9 импульсов (первый после импульса с делителя 10 частоты) проходит через первый элемент И 7 и переключает каналы первого 2 и второго 17 комму- 25 татаров (к выходу первого коммутатора подключен второй вход 1). На выходе второго коммутатора появляется значение выходного сигнала во второй ячейке блока 16 памяти (этот элемент пока еще не заряжен). Этот же импульс с генератора 9 импульсов проходит через элемент 13 задержки на управляющий вход двухпорогового дискриминатора 4. По строб-импульсу двух35 пороговый дискриминатор 4 сравнивает значения сигналов на выходах аналоговых коммутаторов. При совпадении сравниваемых значений (если на втором входе 1 сигнал отсутствует) на выходе двухпарогавого дискриминатора

4 остается сигнал низкого уровня ("0"), на прямом выходе триггера б сохраняется сигнал высокого уровня (1 ), (на инверсном выходе триггера 6 присутствует сигнал низкого .уровня, поэтому вторая ячейка из блока памяти 16 не подключается к второму входу 1). Следующий импульс с генератора 9 импульсов проходит через первый элемент И 7 и подключает очередные (третьи) каналы первого и второго аналоговых коммутаторов, попадает на второй 12 счетчик, а также через элемент 13 задержки запус55 кает двухпорагавый дискриминатор 4.

Аналогичным образом устройство работает да тех пар, пока не будут одвашены все входы 1, после чего в

75 4 блоке 16 памяти хранятся значения сигналов, полученные при первом опросе.

После опроса всех входов 1 следующий импульс с генератора 9 импульсов снова подключает к выходам аналоговых коммутаторов первые каналы.

Далее устройство работает так же, как и в первом цикле, за исключением того, что в двухпороговом дискриминаторе 4 значения сигналов с входов

1 сравниваются со значениями, полученными в предыдущем цикле работы.

Аналогичные процессы в устройстве происходят до поступления по входу

22 сйгнала на окончание работы.

Путем сравнения настоящих и предыдущих значений вводимых сигналов устройство для ввода информации обеспечивает сжатие поступающей информации.

Кроме того, устройство позволяет с большей частотой проводить ввод более высокочастотных сигналов, что повышает достоверность экспериментальных данных автоматически выбирать частоту опроса входов аналоговой информации в зависимости от частотных характеристик аналоговых сигналов, а также снизить требования к внешним регистрируемьм устройствам па объему памяти, используемой для хранения результатов измерений.

Формула изобретения

Устройство для ввода информации, содержащее первый и второй коммутаторы, генератор импульсов, делитель частоты, дешифратор, аналого-цифровой преобразователь, элемент задержки, первый счетчик, триггер, выход генератора импульсов соединен с входам делителя частоты, информационные входы первого коммутатора являются информационными входами устройства, выход первого коммутатора соединен с информационным входом аналого-цифравага преобразователя, выходы которого являются информационными выходами первой группы устройства, о т л ич а ю .щ е е с я тем, что, с целью по.вышения достоверности вводимой информации за счет определения частоты опроса информационных входов, в него введены блок памяти, ключи, группа элементов И, первый и второй элементы И, второй счетчик; дискриминатор, вход. генератора импульсов является

675

Составитель И. Карнова

Техред А. Кравчук Корректор Э. Лончакова

Редактор А. Огар

Заказ ?080/46 Тираж 667 Подписное

ВИИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. ужгород, ул. Проектная, 4

5 1451 входом запуска устройства, выход генератора импульсов соединен с первым входом первого элемента И и счетным входом первого счетчика, выходы которого являются информационными выходами второй группы устройства, выход первого элемента И соединен с тактовыми входами коммутаторов, счетным входом второго счетчика н через элемент задержки с управляющим входом дискриминатора, выход которого соединен с входом установки в "0" триггера, прямой выход которого соединен с вторым входом первого элемента И и является управляющим выходом устройства, инверсный выход триггера аоединен с первым входом второго элемента И и входами первой группы элементов И группы, выходы которых соединены с соответствующими управляющими входами ключей, выходы которых соединены с входами блока памяти, выходы которого соединены с информационными входами второго коммутатора, выходы коммутаторов соединены с соответствующими информационными входами дискриминатора, выходы второго счетчика соединены с входами дешифратора и являются адресными выходами устройства, выходы дешифратора соединены с входами второй группы элементов И группы, информационные входы ключей обьединены с информационными входами первого коммутатора, выход делителя частоты соединен с. входом установки в "1" триггера и вторым входом второго элемента И, выход которого соединен с входом запуска аналого-цифрового преобразова,теля.