Параллельный сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многоразрядных цифровых схемах методом сигнатурного анализа. Целью изобретения является повышение достоверности контроля при произвольном количестве информационных входов. Параллельный сигнатурный анализатор содержит группу сумматоров по модулю два , блок 2 параллельного сдвига, RS-триггер 3 и элемент И4. Блок 2 параллельного сдвига, в свою очередь, содержит регистр, группу коммутаторов и дешифратор. Сущность изобретения заключается в том, что с помощью дешифратора и коммутатора осуществляется реконфигурация структуры анализатора в зависимости от количества требуемых информационных входов. Таким образом , при контроле мноноразрядйых цифровых схем в анализаторе отсутствуют неиспользуемые информационные входы , результатом чего является повышение достоверности контроля. 3 ил. а (С (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„1451696 А1 (5114 G 06 F 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

QvP. j

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4163012/24-24 (22) 16.12.86 (46) 15.01.89. Бюл. Ф 2 (71) Минский радиотехнический институт (72) В.С.Жук (53) 681 .3(088.8) (56) Авторское свидетельство СССР

N- 1180896, кл. G 06 F 11/00, 1985.

Ярмолис В.Н., Демиденко С.Н.

Генерирование и применение псевдослучайных сигналов в системах испытаний и контроля. Минск: Наука и техника, 1986, с. 185-192. (54) ПАРАЛЛЕЛЬНЫЙ СИГНАТУРНЫЙ AHAJIHЗАТОР (57) Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многоразрядных цифровых схемах методом сигнатурного анализа. Целью изобретения является повышение достоверности контроля при произвольном количестве информационных входов.

Параллельный сигнатурный анализатор содержит группу сумматоров по модулю два 11, ° .. 1 . блок 2 пар ьного сдвига, RS-триггер 3 и элемент

И4. Блок 2 параллельного сдвига, в свою очередь, содержит регистр, группу коммутаторов и дешифратор.

Сущность изобретения заключается в том, что с помощью дешифратора и коммутатора осуществляется реконфигурация структуры анализатора в зависимости от количества требуемых информационных входов. Таким обра- с

Ю зом, при контроле мноноразрядйых цифровых схем в анализаторе отсутствуют неиспользуемые информационные вхо-. ды, результатом чего является повышение достоверности контроля. 3 ил.

1451696

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многоразрядных цифровых схемах методом сигнатурного анализа.

Целью изобретения является повышение достоверности контроля при произвольном количестве информационных входов.

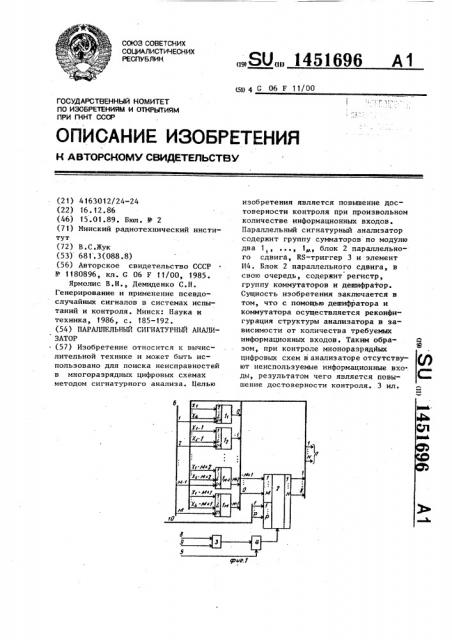

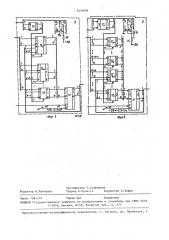

На фиг. 1 представлена блок-схема предлагаемого параллельного сигнатурного анализатора; на фиг. 2— схема блока параллельного сдвига при Mc N, где N — разрядность блока параллельного сдвига; на фиг ° 3 то же, при M N.

Параллельный. сигнатурный анализа-; тор (фиг. 1) содержит M сумматоров

1,, ..., 1„„ по модулю два, где М— максимальное число информационных входов анализатора, блок 2 параллельного сдвига. RS-триггер 3, элемент

И 4, вход 5 синхронизации, группу 6 информационных входов, группу 7 информационных выходов, управляющий вход 8 "Пуск", управляющий вход 9

"Останов", группу 10 входов задания числа используемых информационных входов °

Блок 2 параллельного сдвига содержит регистр 11, группу из M коммутаторов 12„, ..., 12„„, дешифратор

13. В качестве вспомогательных элементов используются резистор 14, кнопка 15 сброса, резистор 16, контактные гнезда 17<, °, 17) 18, 18 „ и 19,, ..., 19, где Р = — log M — количество входов задания

2 числа используемых информационных входов анализатора.

Сумматор. 1, по модулю два сворачивает входную информацию с первого информационного .входа 6 анализатора с соответствующими L разрядами Х,, ..., Хь блока 2 параллельного сдвига на основе коэффициента используемого полинома для сигнатурного анализа х, + + ... + Y

Сумматор 1, где i = 2, ..., М, сворачивает входную информацию с

i-ro информационного входа 6 анализатора с соответствующими L разрядами Х - i + 1, ..., Х, - i + 1 блока

2 параллельного сдвига на основе используемого полинома для сигнатурного анализа с коэффициентами, уменьшенными на (i — 1), х,-1+! Х -i+1 Х -1+ <

5 у 1 + у и + + Y 4

О при В М N, q > (2 — 1) /(2 — 1) при

В M)N, и

2 при В M>)N.

Блок 2 параллельного сдвига по переднему фронту импульса на своем входе записи производит сдвиг в сто35 рону старших разрядов на управляемое количество разрядов i(1 i «< M) в соответствии с кодом (i — 1), поступающим на его входы. Информация, которая должна задвигаться в младшие

40 i разрядов, поступает на 1 информационных входов блока 2 параллельного сдвига.

Каждый из коммутаторов 12 (фиг.2, 3) представляет собой коммутатор с

45 N выходами, N входами и входом управления. При наличии логического нуля на входе управления K-го коммутатора 12 он пропускает информацию со своих входов на выходы, при логической единице на входе управления

К-ro коммутатора 12 на его выходах устанавливается высокоимпедансное третье состояние.

Параллельный сигнатурный анализатор работает следующим образом.

Перед началом работы производится установка в нулевое состояние блока параллельного сдвига путем нажатия кнопки 15 (см. фиг. 2, 3).

Разрядность N блока 2 параллельного сдвига выбирается исходя из трех параметров: M — - требуемой максимальной разрядности цифровых блоков, подлежащих контролю методом сигнатурного анализа:  — максимальной длины контролируемых логических последовательностей (или максимально15 ro количества тактов сигнатурного анализа), q - допустимой вероятности необнаруженных ошибок. сигнатурного анализатора.

Разрядность N блока параллельного

20 сдвига выбирается такой, чтобы выполнялось условие q q д, где q z вероятность необнаруженных ошибок для сигнатурного анализатора, определяемая следующим образом:

25 з 1451696

Контролируемые разряды цифровой схемы (1 < i < M где М вЂ” максимальное количество контролируемых разрядов, — разрядность контролируемой циф5 ровой схемы) подключаются к информационным входам 6 анализатора, начиная с первого входа. На группу входов 10 установки количества контролируемых разрядов подается двоичный код (j -1), соответствующий контролируемым разрядам, причем 1 » в результате чего только один j-й коммутатор 12 пропускает информа3 цию со своих входов на выходы; а на выходах остальных коммутаторов 12— высокоимпедансное третье состояние (см. фиг. 2) . Отметим, что если в проверяемом устройстве не предусмотрено формирование кода количества контролируемых разрядов, то входы 10 анализатора никуда не подключаются и двоичный код (j-1) количества контролируемых разрядов набирается путем

\ установки P коммутационных. проводки-, 25 ков в соответствующие контактные гнезда 17; ... 18; или 18, — 19; (фиг. 2 и 3) .

По сигналу "Пуск" с входа 8 анализатора, определяющему начало интервала контроля входных последовательностей, устанавливается в единичное состояние триггер 3;. "1" с выхода триггера 3 поступает на первый вход элемента И 4, разрешая прохождение через него импульсов с

Входа 5 синхронизации анализатора на вход записи блока 2 параллельного сдвига. Логическое состояние с К-ro разряда информационного входа 6 ана- 4п лизатора, где К = 1, ..., », суммируется по модулю два соответствующим сумматором 1 с соответствующими L разрядами (X — К+1,... Х вЂ” К+1) блока 2 параллельного сдвига и записывается с параллельным сдвигом на j разрядов в блок 2 параллель. ного сдвига по переднему фронту синхроимпульсов, поступающих с выхода элемента И 4, что и приводит к формированию сигнатуры.

По сигналу "Останов", поступающему на вход 9 анализатора, триггер

3 устанавливается в нулевое состояние, запрещающее прохождение синхроимпульсов через элемент И 4. Запись в блок 2 параллельного сдвига прекращается, и в нем образуется сигнатура контролируемой j-разрядной последовательности.

Повышение достоверности предлагаемого анализатора по сравнению с прототипом обеспечивается тем, что при заданном числе информационных входов отсутствуют неиспользуемые входы, на которые подается незначащая информация, в результате чего, например, двойные ошибки выявляются на более длинных контролируемых последовательностях, чем в устройстве-прототипе.

Формула изобретения

Параллельный сигнатурньп» анализатор, содержащий группу сумматоров по модулю два, регистр, RS-триггер и элемент И, причем входы "Пуск" и

"Останов" анализатора подключены соответственно к S- u R-входам RSтриггера, выход которого соединен с первым входом элемента И, второй вход которого является синхровходом анализатора, выход элемента И соединен с входом записи регистра, информационные входы сумматоров по модулю два группы образуют группу информационных входов анализатора, группы информационных входов сумматоров по модулю два грунпы соединены с выход дами регистра в соответствии с видом образующего полинома, группа выходов регистра является группой информационных выходов анализатора, о тл и ч а ю шийся тем, что, с целью повышения достоверности контроля при произвольном количестве информационных входов, анализатор содержит дешифратор и группу коммутаторов, первые группы информационных входов которых соединены с группой выходов регистра, вторые группы информационных входов коммутаторов соединены с группой выходов сумматоров по модулю два группы, группы выходов коммутаторов объедине»ы и подключены к группе информационных входов регистра, управляющие входы коммутаторов подключены.к соответствующим выходам дешифратора, группа входов которого является группой входов задания числа используемых информационных входов анализатора.

1451696

Составитель С.Старчихин

Техред А. Кравчук Корректор С.Черни

Редактор И.Рыбченко

Заказ 7081/47 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4