Ячейка памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении устройств , сохраняющих информацию при перерывах питания. Целью изобретения является повьшение надежности восстановления информации в ячейке памяти при перерьгоах питания. Для достижения этой цели в ячейку памяти введены второй ключевой элемент 7, элемент И 9, источник опорного напряжения 14, пороговый элемент 17, элемент задержки 18, первый 15. и второй 19 формирователи импульсов, элемент ИЛИ 16. Благодаря этому на правильность восстановления информации не оказывают влияния время нарастания; напряжения питания до номинального значения, если оно мень-j ше,чем задержка элемента задержки 1Й, а также непрямоугольность петли гестерезиса сердечника трансформатора 5. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ÄÄSUÄÄ 1451776 А1 (51)4 С 11 С 19 14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4205978/24-24 (22) 12.01.87 (46) 15.01.89. Бюл. ¹ 2 (72) А.M.Ïóæàé (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

¹ 1051584, кл. G 11 С 19/14, 1982.

Авторское свидетельство СССР № 1234883, кл. С 11 С 19/14, 1984. (54) ЯЧЕЙКА ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении устройств, сохраняющих информацию при перерывах питания. Целью изобретения является повьппение надежности восстановления информации в ячейке памяти при перерывах питания. Для до стижения этой цели в ячейку памяти введены второй ключевой элемент 7, элемент И 9, источник опорного напряжения 14, пороговый элемент 17, элемент задержки 18, первый 15 и второй t9 формирователи импульсов, элемент ИЛИ 16. Благодаря этому на правильность восстановления информации не оказывают влияния время нарастания: напряжения питания до номинального значения, если оно мень- ше,чем задержка элемента задержки 18 а также непрямоугольность петли гестерезиса сердечника трансформа тора 5. 1 ил.

1451776

Изобретение относится к вычислительной технике и может быть исполь. зовано при построении устройств, сохраняющих информацию при переры5 вах питания.

Целью изобретения является повышение надежности восстановления ин формации при перерывах питания.

На правильность восстановления информации не оказывает влияния время нарастания напряжения питания до номинального значения, а также непрямоугольность петли гистерезиса сердечника трансформатора ячейки памяти.

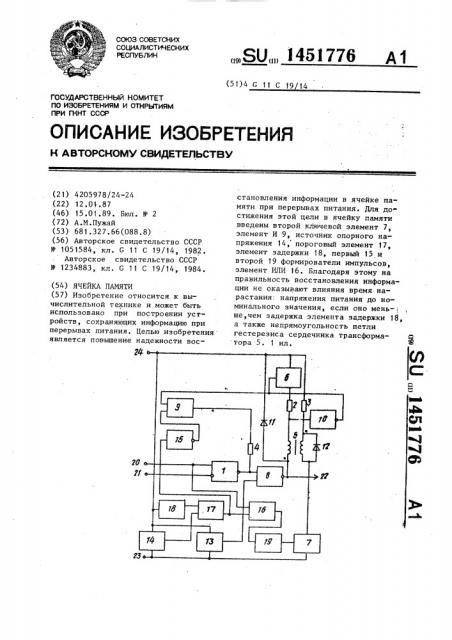

На чертеже. изображена схема ячейки памяти.

Ячейка памяти содержит элемент 1

ЗАПРЕТ, три пассивных элемента на резисторах 2-4, накопительный элемент на трансформаторе 5, два ключевых элемента 6 и 7,и триггер, выполненный на элементе И-НЕ 8, элементе И 9, инверторе 10, два шунтирующих элемен-25 та на .диодах 11 и 12, элемент 13 начальной установки, источник 14 опорного напряжения, первый формирователь 15 импульса, элемент ИЛИ 16, пороговый элемент 173 эл ент 18 за- 30 держки и второй формирователь 19 импульса.

Первый и второй входы элемента 1

ЗАПРЕТ являются соответственно информационным входом 20 и входом 21 запрета ячейки памяти. Выход элемен- З5 та И-НЕ 8 является выходом 22 ячейки памяти, На чертеже показаны также шина 23 нулевого потенциала и шина 24 питания.

Элемент 1 ЗАПРЕТ является элементом с тремя состояниями выхода. Элемент 13 начальной установки выполнен на резисторе,,конденсаторе и ди-. оде. Первый-15 и второй 19 формирователи импульсов выполнены на одновибраторах. Первый формирователь

15 имеет инверсный выход и служит для блокировки обратной связи триггера на время действия помехи при перемагничиванни сердечника трансформатора 5. Второй формирователь

19 обеспечивает перемагничивание сердечника трансформатора.

Ячейка памяти работает следующим образом. 55

При подключении питания выходным сигналом (логическим "0") элемента

13 начальной установки триггер ячейки памяти устанавливается в исходное (единичное) состояние. При этом на выходе элемента И-HE 8 устанавливается уровень логической "1", которая через первую обмотку трансформатора 5 устанавливает на выходе инвертора 10 уровень логического

"0", поступающего на первый вход элемента И 9. На выходе элемента И 9 также устанавливается уровень логического "0", который через третий резистор 4 поступает на вход элемента И-HE 8, замыкая тем самым положительную обратную связь триггера.

Затем через время, определяемое временем нарастания напряжения питания до номинального значения, с помощью элемента 18 задержки, источника 14 опорного напряжения и порогового элемента 17 формируется импульс тока во второй обмотке трансформатора 5 формирователем 19. При действии импульса тока во второй обмотке трансформатора 5 рабочая точка на характеристике намагничивания сердечника начинает смещаться из точки -В в точку +В, Это сопрсчождается изменением индукции на величину 8В что вызывает появление сиг

Р нала в первичной обмотке.

Выделенный в первичной обмотке трансформатора 5 сигнал на начальном участке блокируется с помощью элемента И 9 сигналом, сформированным первым формирователем 15 импульса.

Длительность импульса формирователя 15 должна быть больше или равна времени перемагничивания материала сердечника при изменении состояния намагниченности от остаточной индукции +Br до индукции насыщения -В .

Длительность импульса формирователя 19 должна быть бьльше времени перемагничивания материала сердечника при изменении состояния намагниченности от отрицательной остаточной индукции -В„- до индукции насыщения +В >, При восстановлении логического

"0" происходит изменение состояния намагйичивания от -В 1. до +В . Как только длительноать выделенного в первичной обмотке трансформатора 5 сигнала превысит длительность импульса формирователя 15, на выходе элемента И 9 появится уровень логической "1", который через резистор

14517

4 устанавливает элемент И-НЕ 8 в состояние логического "0". Через открытый первый ключевой элемент 6, резистор 2 и первую обмотку транс5 форматора 5 начинает протекать ток логического "0" элемента И-НЕ 8.

Положительная обратная связь триггера замыкается, и он устанавливает" ся в нулевое состояние. 10

После окончания импульса формирователя 19 второй ключевой элемент

7 размыкается и под действием тока, протекающего через первую обмотку . трансформатора 5 и первый ключевой 15 элемент 6, рабочая точка смещается в точку -В5, соответствующую логическому "0". Диод 12, включенный параллельно второй обмотке трансформатора 5, исключает сбой триг- 20 гера в момент закрывания второго ключевого элемента 7.

При восстановлении логической

II 11

1 происходит изменение состояния намагничивания от +В,. до +В з и дли- 25 т ельнос ть выделенного сигнала меньше длительности импульса формирователя 1 5, поэтому н а выходе элемента

И 9 состояние логической ". 1 " н е изменяется и элемент памяти остается З0 в единичном состоянии . После окончания импульса формирователя 1 9 в торой ключевой элемент 7 размыкается и рабочая точка смещает ся в точку

+B » ч то соответствует хранению в

35 сердечнике логической "1".

Запись логической "1" в запоминающее устройство производится путем подачи на вход 21 запрета разрешающего сигнала, а на информационный

40 вход 20 уровня логической "1". С выхода элемента 1 ЗАПРЕТ уровень логического "0" поступает на вход элемента И-HE 8 и устанавливает триггер ячейки памяти .в состояние логической "1". Одновременно уровнем логической "1" через элемент ИЛИ 16 запускается второй формирователь 19 импульса. Замыкается второй ключевой элемент 7 и по второй обмотке

50 трансформатора 5 протекает ток, обеспечивающий насыщение сердечника до индукции Вз. После окончания импульса записи с выхода формирователя 19 импульса второй ключевой элемент 7 размыкается и рабочая

55 точка на характеристике намагничивания сердечника смещается в точку

+В„.

Запись логического "0 1 в запоминающее устройство производится аналогично. При этом насыщение сердечника до уровня отрицательной индук-, ции насыщения (-Вz) обеспечивается током логического "0" элемента И-НЕ

8 через первый ключевой элемент б.

Второй ключевой элемент 7 разомкнут

После записи информации элемент

1 ЗАПРЕТ. блокируется по входу 21 запрета и на его выходе устанавливается третье состояние, исключакнцее влияние на триггер устройства входных сигналов как в режиме хранения информации, так и в режиме восстановления информации при перерывах питания.

Формула изобретений

Ячейка памяти, содержащая элемент ЗАПРЕТ, первый и второй входы которого являются соответственно уп, равляющим входом и входом запрета ячейки памяти, элемент И-НЕ, первый вход которого соединен с выходом ,элемента ЗАПРЕТ, а выход явля1 ется выходом ячейки памяти, инI вертор, первый и второй пассивные элементы на соответствующих резисторах, первый ключевой элемент, управляющий вход которого соединен с выходом инвертора,а выход — с шиной питания ячейки, элемент начальной установки, выход которого соединен с вторым входом элемента И-НЕ1 первый и второй шунтирующие элементы, накопительный элемент на трансформаторе, начальный вывод первой обмотки которого соединен с выходом элемента И-HE и первым выводом первЬro шунтирующее элемента,а конечный вывод первой обмотки — с входом инвертора и первым выводом первого ре1 зистора, второй вывод которого со.единен с входом первого . ключевого элемента, начальный и конечный выводы второй обмотки трансформатора соединены соответственно с вторым и первым выводами второго шунтирующего элемента, первый вывод второго резистора соединен с шиной питания, ячейки, а второй — с начальным выводом второй обмотки трансформатора, отличающаяся тем, что, с целью повышения надежности восстановления информации при перерывах питания, в нее введены второй ключевой элемент, элемент И, элемент

1451

Составитель А.Дерюгин

Техред Л. Олийнык Корректор В.Бутяга

Редактор E.Êîï÷à

Заказ 7086/51 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, E-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

ИЛИ, элемент задержки, пороговый элемент, источник опорного напряжения, первый и второй формирователи импульсов и третий пассивный элемент на резисторе, выводы которого соединены соответственно с выходом элемента ЗАПРЕТ и с выходом элемента И, первый вход которого соединен с выходом инвертора, а второй - с выходом первого формирователя импульсов, вход которого соединен с выходом порогового элемента и первым входом элемента ИЛИ, второй вход которого соединен с первым входом элемента ЗАПРЕТ, а выход — с входом второго формирователя импульсов, выход

776 6 которого соединен с управляющим входом второго ключевого элемента, вход и выход которого соединены соответственно с шиной нулевого потенциала ячейки памяти и концом второй обмотки трансформатора, вход элемента задержки соединен с шиной питания ячейки памяти, а выход — с первым входом порогового элемента, второй вход которого соединен с выходом источника опорного напряжения, первый и второй выводы питания источника опорного напряжения и элемента начальной установки соединены соответственно с шинами питания и нулевого потенциала ячейки памяти.