Трехканальное мажоритарное резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть применено при построении высоконадежных запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Трехканальное мажоритарно.е резервированное запоминающее устройство содержит три блока 1 памяти с контрольными разрядами 2, С выхода каждого блока 1 памяти информация поступает на свой блок 3 связки, где формируется контрольный разряд, который сравнивается с контрольным разрядом 2 в элементе 4 сравнения. Кроме того, выходная информация каждого блока 1 памяти сравнивается блоком 5 сравнения с выходной информацией другого блока 1 памяти . Выходные сигналы элементов 4 и блоков 5 являются соответственно информационными и управляющими сигналами коммутатора 7, выходные сигналы которого задают режим работы мажоритарного блока 6, на входы которого поступает информация от трех бло ков 1 памяти. 3 ил. с (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1451780 А1 (51)4 С 11 С 29/00 G 06 F 11/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4130952/24-24 (22) 08.10.86 (46) 15.01.89. Бюл. ¹ 2 (72) Ю.А.Кузнецов, А.П.Морозов, Г.П.Поршаков и M.È.ÏoëèòoB (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

¹ 562822, кл. С 06 F 11/18 1975.

Авторское свидетельство СССР

¹ 1035608, кл. С 06 F 11/18, 1985.,(54) ТРЕХКАНАЛЬНОЕ МАЖОРИТАРНОЕ РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВ0 (57) Изобретение относится к цифровой вычислительной технике и может быть применено при построении высоконадежных запоминающих устройств.

Цель изобретения — повышение быстродействия устройства. Трехканальное мажоритарное резервированное запоминающее устройство содержит три блока

1 памяти с контрольными разрядами 2, С выхода каждого блока 1 памяти информация поступает на свой блок 3 связки, где формируется контрольный разряд, который сравнивается с контрольным разрядом 2 в элементе 4 сравнения. Кроме того, выходная информация каждого блока 1 памяти сравнивается блоком 5 сравнения с выход" ной информацией другого блока 1 памяти. Выходные сигналы элементов 4 и блоков 5 являются соответственно информационными и управляющими сигналами коммутатора 7, выходные сигналы которого задают режим работы мажоритарного блока 6, на входы которого поступает информация от трех блоков 1 памяти. 3 ил.

t 45l 780

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении высоконадежных запоминающих устройств.

Цель изобретения — повышение быстродействия устройства.

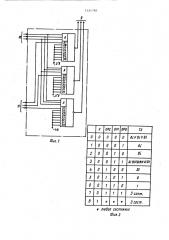

На фиг.1 представлена структурная схема трехканального мажоритарного резервированного запоминающе- 1п го устройства; на фиг.2 — функциональная схема коммутатора;на фиг.3— таблица истинности мажоритарного блока.

Устройство содержит блоки 1 памяти с контрольными разрядами 2, блоки 3 свертки, элементы 4 сравнения, блоки 5 сравнения, мажоритарный блок

6, коммутатор 7, информационные выходы 8, выход 9 коммутатора 7, уп- 20 равляющие входы 10 и информационные входы 11 коммутатора 7.

Трехканальное мажоритарное резервированное запоминающее устройство работает следующим образом. 25

Если информация, считанная из трех блоков 1, одинаковая, то все блоки

5 сравнения вырабатывают на выходах логические "0", которые поступают на вход 10 коммутатора 7, и на выходе 9 коммутатора 7 устанавливается код 110, При этом мажоритарный блок 6 работает как схема голосования два из трех для информации с блоков

В случае возникновения ошибки любой кратности в одном из резервируемых блоков 1, два блока 5 сравнения вырабатывают сигналы несравнения — лог. "1", а третий — сигнал сравнения — лог. "0". Мажоритарный блок 6 работает в этом случае аналогично предыдущему варианту как схема голосования два из трех за счет наличия хотя бы одного логического "0" на входе 10 коммутатора 7.

При возникновении ошибок в. двух резервируемых блока 1 три блока 5 сравнения вырабатывают сигналы неи и сравнения логические 1, которые поступают на вход 10 коммутатора 7, разрешая прохождение сигналов с выходов .. лементов 4 сравнения каждого канала на выход 9 коммутатора 7.

Коммутатор 7 начинает в этом случае работать по входу 11. Информация с резервированных блоков 1 в каждом канале проходит через блок 3 свертки на элемент 4 сравнения для сравнения с контрольным разрядом 2.

Если информация поступила с ошибкой, элемент 4 выдает лог. "1", а если без ошибки — лог."0". При этом на выходе 9 коммутатора 7 устанавливается управляющий код, разрешающий передачу информации с блока 1, элемент 4 сравнения которого имеет на выходе лог. "0", через мажоритарный блок 6.

Формула изобретения

Трехканальное мажоритарное резервированное запоминающее устройство, содержащее три блока памяти, информационные выход каждого из которых подключен к входу соответствующего блока свертки, выход каждого из которых подключен к первому входу соответствующего элемента сравнения, второй вход каждого из которых подключен к контрольному выходу соответствующего блока памяти, коммутатор, выходы которого подключены к управляющим входам мажоритарного блока, выход которого является информационным выходом устройства, о т л и ч аю щ е е с я тем, что, с целью повышения быстродействия устройства,оно содержит три блока сравнения, первый вход каждого из которых подключен к выходу соответствующего блока памяти и к соответствующему информационному входу мажоритарного- блока, второй вход каждого из блоков сравнения подключен к выходу последующего блока памяти, выходы блоков сравнения и выходы элементов. сравнения подключены соответственно к управляющим ч информационным входам коммутатора.

145I 780 у рюппю спстпяное

67va.Л