Многоканальное устройство для ввода аналоговых данных и буферная память

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной и вычислительной технике, а именно к устройствам запоминания, и может быть использовано как при построении высокопроизводительных систем сбора и обработки аналоговых дан

„,Я0„„14533Я7 А1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ш 4 С 06 Р 3/05 () ИСАНИНА ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4267119/24-24 (22) 23.06.87 (46) 23.01.89. Бюл. 9 3 (72) А.В.Апыхтин, Н.В.Третьякова, В.А.Трушин и М.И.фихман (53} 681.32(088.8) (56) Авторское свидетельство СССР

В 450157, кл. G 06 F 3/05, 1974.

Авторское свидетельство СССР

9 1238054, кл. G 06 F 3/05, 1984. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ

ВВОДА АНАЛОГОВЫХ ДАННЫХ И БУФЕРНАЯ

ПАМЯ1 Ь (57) Изобретение относится к измерительной и вычислительной технике, а именно к устройствам запоминания, и может быть использовано как при построении высокопроизводительных систем сбора и обработки аналоговых дан1453397 ных с использованием мультиплицированной структуры и ЭВМ, так и отдельно при построении многоканальных систем и буферных накопителей. Целью изобретения является расширение функциональных возможностей. Устройство содержит N каналов преобразования аналоговых величин, первый блок 2 формирования приоритетного адреса, Изобретение относится к измерительной и вычислительной технике, устройствам запоминания и может быть использовано как совместно при построении высокопроизводительных систем сбора,и обработки аналоговых данных с использованием мультиплицированной структуры и ЭВМ, так и отдельно при построении многоканальных систем и буферных накопителей. 10

Целью изобретения является расширение функциональных воэможностей.

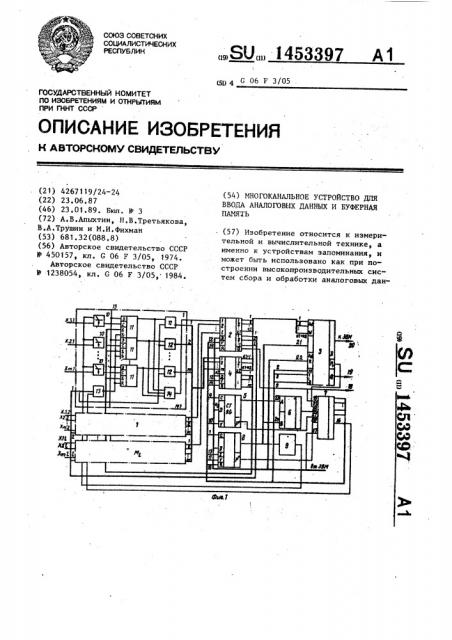

На фиг.1 изображена структурная схема многоканального устройства для ввода аналоговых данных; на фиг.2 — 15 структурная схема блока управления; на фиг.3 — структурная схема буферной памяти.

Многоканальное устройство для ввода аналоговык данных. (фиг. 1) содержит 20

N каналов преобразования аналоговых величин, разделенных на 1 групп (модулей) 1 по m каналов в каждой, первый блок 2 формирования приоритетного адреса, буферную память 3, второй блок 4 формирования приоритетного адреса, второй счетчик 5, блок 6 сравнения, блок 7 управления, первый счетчик 8, цифроаналоговый преобразователь 9. 30

Каждый модуль 1 содержит m компараторов 10, m триггеров 11, m элементов И первой группы 12, элементы И второй группы 13 и элемент ИЛИ 14.

Кроме того, на схеме устройства (фиг. 1) обозначены шина 15 логической, единицы устройства, выход 16 сброса блока 7 управления, управляющий вход

17 устройства, выход 18 запроса устройства, информационные выходы 19 и буферную память 3 второй блок формирования приоритетного адреса 4, счетчики 5, 8, блок 6 сравнения, блок 7 управления, цифроаналоговый преобразователь 9. Каждый канал 1 содержит компараторы 10, триггеры 11, элементы

И первой группы 12, элемент И 13 и элемент ИЛИ 14. 2 с. и 1 з.п. ф-лы, 3 ил.

20 устройства, входы 21 данных буферной памяти 3, входы 22 адреса считывания буферной памяти 3, входы 23 и

24 блока 6 сравнения, вход 25 начала записи ранга блока 7 управления, вход

26 окончания контроля блока 7 управления, вход 27 конца поиска ранга блока 7 управления, вход 28 конца цикла блока 7 управления.

На схеме блока управления (фиг.2) обозначены генератор 29 импульсов, три триггера 30-32, два счетчика 33 и 34, восемь элементов И 35-42, три элемента ИЛИ 43-45, регистр 46 кода операции, мультиплексор 47.

На схеме буферной памяти (фиг.3) обозначены элемент ИЛИ 48, три счет" чика 49-51, два дешифратора 52 и 53, блок 54 управления, блоки 55 памяти.

Модуль (группа из m каналов) обеспечивает сравнение уровней образцового уравновешивающего напряжения и напряжения на входах устройства независимо по каждому каналу, фиксацию момента совпадения уровней и формирование сигнала "Запрос" при срабатывании компаратора.хотя бы в одном из каналов.

Блок 2 обеспечивает формирование кодов номеров модулей либо сформировавших запросы в соответствии с приоритетом, либо в соответствии с кодом, установленным на шине данных и сброс триггеров сработавших каналов, причем на первой группе выходов формируется позиционный двоичный код, на второй группе выкодов — унитарный двоичный код, а на третьем выходе - сигнал наличия запроса хотя бы от одного модуля. Блок 2 представляет собой послез

14533 довательно соединенные приоритетный шифратор и дешифратор, выходы которых являются соответственно первой и второй группой выходов блока 2. Выходы дешифратора соединены также с соответствующими первыми входами двухвходовых схем ИЛИ, вторые входы ксторых объединены и являются R — âõîäîì сброса блока 2. Все линии шины данных D 10 подключены к соответствующим выходам приоритетного шифратора по схеме

МОНТАЖНОГО ИЛИ. Вход приоритетного шифратора является управляющим входом блока 2. 5

Буферная память 3 обеспечивает согласование времени преобразования И аналоговых сигналов в коды и времени ввода данных в ЭВИ с целью максимального использования быстродействия 20 подсистем сбора и обработки данных.

Буферная память 3 позволяет осуществлять запись по произвольно заданному адресу или в последовательно расположенные ячейки памяти, а считывание производить как законченным и упорядоченным сообщением последовательно по одной ячейке, начиная с ячейки с заданным начальным адресом, так и по одному слову с произвольного ЗО адреса, причем запись и считывание могут производиться как в одно и то же, так и в разное время. По логике работы считывание и запись всегда производятся по несовпадающим адресам.

Блок 54 управления представляет собой два устройства сравнения кодов, двухвходовый элемент ИЛИ, выход кото- 40 рого соединен с счетным входом счетного триггера, R-вход которого является R-входом блока 54 управления, V-вход которого соединен с первым выходом элемента ИЛИ, второй вход ко- 45 торого соединен с выходом первого устройства сравнения, причем с первыми и вторыми входами первого устройства сравнения соединены младшие Р1 разрядов соответственно первого и третьего счетчиков, а с первыми и вторыми входами устройства сравнения соединены старшие Р2 разрядов соответственно второго и третьего счетчиков. Выходы элемента ИЛИ и второго устройства сравнения являются соответственно выходами Z1 и Z2 блока управления, выход Z3 которого является выходом счетного триггера.

97

Блок 4 обеспечивает формирование кодов номеров каналов в модулях, сформировавших запросы в соответствии с приоритетом, причем на первой группе выходов формируется позиционный двоичнь.й код, на второй группе выходов — унитарный двоичный код, а также сброс триггеров сработавших канало». Блок 4 реализуется аналогично блоку 2.

Счетчик 5 может быть выполнен на микросхемах К155ТИ7 °

Блок б сравнения может быть реализован, например, на микросхемах

К555СП1.

Блок 7 управления обеспечивает управление и синхронизацию работы всей системы, а также прием команд управления извне, например от ЭВМ.

Устройство может работать в двух режимах: режиме измерения и режиме контроля.

Работа устройства для ввода аналоговых данных и буферная память в режиме измерения осуществляются под управлением ЭВИ, которая формирует yrfравляющее слово соответствующего режима для записи в регистр 46 кода операции, а также команды "Пуск", "Сброс", "Сброс буферной памяти" и

"Импульсы считывания, поступающие на вход 17 блока 7 управления и на входы данных блоков 2 и 4 и счетчиков 5 и 8. В исходном состоянии при включении гитания или начале работы счетчик 8, все триггеры 11 всех модулей 1, триггеры 30-32, счетчики 33 и 34 блока 7 управления, счетчики 4051, буферной памяти 3 установлены в исходное (нулевое) состояние и на выходах 19 буферной памяти 3 сформиро ваны Z1 = О, Z2 = О и Z3 = 1, что соответствует разрешению записи и запрещению считывания иэ буферной памяти 3 иэ-за отсутствия данных в последней. При поступлении сигнала "

"Пуск" в блок 7 управления на его первом выходе формируются импульсы с частотой Еи м †-„ поступающие на и и счетчик 8, выходы которого подключены к входам преобразователя 9. При

9Yом на выходе преобразователя 9 формируется ступенчато изменяющееся обр эцовое напряжение. В момент совпадения уровня образцового напряжения и напряжения на одном или нескольких

1453397 входах устройства Х, где i = 1,m, 1,1, на выходе, соответствующем этому входу (входам), компаратора 10 формируется перепад напряжения (на5 пример, из состояния "0" в "1"), по которому соответствующий триггер 11 переходит в единичное состояние. Уровень логическои единицы с выхода триггера 11 в )-группе через элемент

ИЛИ 14 в качестве запроса q от j-.é

1 группы каналов поступает- на вход блока 2. Блок 2 по одному или нескольким запросам r, формирует,на 1 своих двух группах выходов соответственно унитарный и позиционные коды наиболее приоритетного из сформировавших запрос модулей 1, а на выходе — сигнал "Запрос" — Q, поступающий на выход 18 блока 7 управления. унитарный код с второй группы выхо. дов блока 2 разрешает подключение к входам блока 4 сигналов наиболее приоритетного из выставивших запросы Мо дулей, .так как логическая " 1" в одном 25 из разрядов унитарного кода разрешает прохождение сигналов с выхода сработавшего триггера 11 на вход блока

4. В это время на вьиодах всех остальных элементов И 12 модулей 1 — 30 высокий уровень, что обеспечивает реализацию ИОНТАЖНОГО ИЛИ. Блок 4 формирует,на двух группах выходов позиционный и унитарный коды номера наиболее приоритетного канала в обслуживаемом модуле. Выходы унитарного кода поступают на вторые входы сброса триггеров 11, разрешая прохождение сигнала "Сброс" на триггер 11 наиболее приоритетного из сработавших 40 каналов. Объединенные первые группы выходов блока 2 и блоКа 4 образуют адрес записи буферной памяти 3. 3a" . лись в буферную память 3 осуществля- ется блоком 7 управления при возник- 45 новении сигнала "Запрос" и в соответствии с установленным режимом работы устройства. По окончании записи блок

7 управления формирует на своем выходе 16 импульс "Сброс залроса", ко- 50 торый установит в нулевое состояние триггер, наиболее приоритетный из сработавших триггеров 11. Если сигнал "Запрос" сформирован несколькими каналами в одном модуле 1 или несколькими модулями, то процедура записи повторяется, в противном случае блок 2 снимает "Запрос" и блок 7 управления разрешает формирование ступенчато изменяющегося образцового напряжения до появления очередного сигнала "Запрос".

Рассмртрим брлее подробно работу блока 7 управления.

Регистр 46 кода операции блока 7 управления предказначен для хранения кода режима работы системы. При этом принято следующее кодирование:

1 разряд — режим работы устройства:

"0" — измерение, " 1" — контроль. . 2 разряд — режим считывания: "0"считывание по произвольному адресу, "1" считывание массивом.

3 разряд — режим записи: "0" — запись по произвольному адресу, "1" J запись с последовательной адресацией.

4 и 5 разряды - режим контроля:

"1" — в 4 разряде соответствует режиму "больше", 1 — в 5 разряде соответствует режиму "меньше".

6 разряд - режим измерения по. заданному адресу: "0" — измерение по проиэвольному адресу, "1" — измерение по заданному адресу.

7 разряд - реверс счетчика. 8:."0"соответствует +1, " 1" - соответствует -1.

В блоке управления генератор 29 формирует тактовые импульсы с часто-. той Й „ ъ Й„, которые обеспечивают реализацию принципа синхронного управления всеми блоками устройства, поступают на оба счетчика 33 и 34, Счетчики 33 и 34 используются в качестве делителей частоты и распределителей импульсов,.причем счетчик 34 используется для управления счетчиком 8 преобразователя 9, а счетчик

33 — для управления записью данных в буферную память. Время установления напряжения на выходе преобразователя 9 (c ) с заданной погрешностью существенно больше времени записи в буферную память 3 и поэтому коэффициент деления счетчика 34 больше, чем счетчика 33. Таким образом, за время ьи 1А можно произвести несколько записей в буферную память 3. Импульсы с (i-1)-го выхода счетчика 34 через элемент ИЛИ 43 поступают на

С-вход триггера 30 и в случае наличия запроса q переводят последний в единичное состояние. В этом состоянии триггер 30 запрещает работу счетчика

34 (формирование очередного импульса для счетчика 8), т.е. приостанавливает развертку на время записи в бу1453397 ферную память 3 и разрешает работу счетчика 33. По импульсам с первых двух выходов счетчика 33 (второй, третий и четвертый выходы блока 7 управления) в буферную память 3 осуществляется запись данных в соответствии с выбранным режимом записи буферной памяти 3: запись по произвольному адресу (по номеру сработавшего 10 канала), запись с последовательной адресацией (запись ранжированных по уровню сигнала номеров каналов). Передний фронт импульса с третьего выхода счетчика 33 (выход 16 блока 7 15 управления) через элемент ИЛИ 44 устанавливает триггер 11 обслуженного модуля 1 в нулевое состояние» Задний фронт импульса с третьего выхода счетчика 33 через элемент ИЛИ 43 ус- 20 тановит триггер 30 в состояние, соответствующее уровню сигнала "Запрос" на входе 18 блока 7 управления. При этом процедура записи повторяется до тех пор, пока блок 2 не снимет сиг- нал "Запрос". В этом случае на D-входе триггера 30 блока 7 управления сформируется уровень логического нуля и триггер 30 перейдет в нулевое состояние, при этом возобновится фор- 30 мирование образцового напряжения до появления очередного запроса. По достижению ступенчато изменяющимся образцовым напряжением границы диапазона счетчик 8 формирует импульс "ПереI полнение", который поступает на вход

28 блока 7 управления. Этот импульс через мультиплексор 47 и элемент ИЛИ

45 блоха 7 управления поступает на

R-вход триггеров 30-32, устанавливая 40 их в нулевое состояние. При этом за-. прещается формирование импульсов для счетчика 8 (элемент И 40) и оповещается буферная память 3 об окончании записи информации об И аналоговых 45 сигналах.

После каждого цикла преобразования

Н аналоговых сигналов (цикла измерения) счетчик 8 и все триггеры 11 автоматически устанавливаются в исходное состояние.

Рассмотрим работу устройства в режщме контроля.

В этом случае в регистр 46 кода операции (КОП) из ЭВМ записывается соответствующее управляющее слово.

Режим контроля имеет два подрежима: режим измерения в заданных границах и собственно режим контроля. Режим измерения в заданных границах осуществляется следующим образом. Управля" ющее слово, передаваемое ЭВМ в регистр 46, в этом случае 1111000. При этом в счетчик 8 записывается код нижней уставки. Затем управляющее слово меняется на 1110100 и в счет Ф чик 5 записывается код верхней уставки. Далее ЭВМ формирует сигнал "Пуск" и устройство функционирует аналогично режиму "Измерение" при записи в память 55 ранжированного ряда с пос- ледозательной адресацией. При этом в счетчике 49 буферной памяти 3 накапливается число записываемых в память слов. Сигнал окончания контроля в этом случае формирует блок 6 сравнения в момент равенства верхней уставки и кода ступенчато изменяющегося напряжения. Возможны следующие модификации режима. Измерение упорядоченного по номерам каналов ряда значений (управляющее слово в этом случае

1101000). Измерение упорядоченного по значениям ряда от максимального к минимальному (управляющее слово

11!1001). Режим, ближайший к заданному сверху. Измерение начинается с заданного значения (нижняя уставка) до первого сработавшего канала (управляющее слово 1100100) . Режим, ближайший к заданному снизу. Измерение начинается с заданного значения (верхняя уставка) до первого сработавшего канала при изменении ступенчато изменяющегося образцового напряжения в сторону уменьшения (управляющее слово 1101001) . В режиме собственно контроля границы могут быть заданы верхним и нижним номерами значений в равжированном ряду (ранговыми статистиками). В этом случае осуществляется преобразование только тех .величин, значение которых, лежит между заданными ранговыми статистиками. Реализация данного режима на аппаратном уровне существенно упрощает статистическую обработку сигналов. Запись нижней уставки в дополнительном коде в счетчик 49 буферной памяти 3 осуществляется по управляю- . щему слову 11 10010. Затем записывается верхняя уставка в дополнительном коде в счетчик 5 управляющим словом 1111000. Работа устройства далее о"уществляется так же, как и в режиме измерения при записи с последовательной адресацией. До переполнения счет1453397

l0

20 чика 49 (начало записи ранга) триг"

rep 32 блока 7 управления блокирует сигнал Z1 буферной-памяти 3, что соответствует сигналу отсутствия информации в данной зоне буферной памяти. После переполнения счетчика 49 в буферную память 3 начинают записываться значения с номерами больше за. данного в ранжированном ряду. Сигнал

"Конец поиска ранга" 27 (выход переполнения счетчика 5) действует аналогично сигналу "Конец цикла". К этому моменту в буферную память записан отрезок ранжированного ряда между двумя заданными ранговыми статистиками. Модификациями данного режима являются следующие.

Измерение наперед заданной ранговой статистики (поиск ранга). В этом случае верхняя граница устанавливается равной заданному рангу RN, а нижняя граница - равной (RN - 1). Управляющее слово в этом случае не мес

N няется. При RN = — осуществляется из2 мерение медианы.

При RN N реализуется режим поиска максимального значения.

При RN .= 1 осуществляется режим поиска минимального значения.

В случае, если управляющее слово равно 1110010 и сохраняется неизменным в течение цикла иЪмерения, реализуется режим измерения по. заданному адресу. При этом блоки 2 и. 4 работают в качестве дешифраторов выбора заданного канала. Длительность цикла в режимах измерения в заданных границах с последовательной адресацией блоков

55 памяти в общем случае меньше цик ла измерения с записью по произвольному адресу, так как нет необходимос-. ти в доведении образцового напряже-. ния до границы диапазона измерения.

Режимы контроля характеризуются

1 тем, что контролируемые входные сигналы не преобразуются в код, так как в этих случаях требуется информация только о номерах каналов. Рассмотрим работу устройства в режиме "Зона".

ЭВМ вместе с. кодом нижней уставки задает устройству управляющее слово

1110100. При этом на выходе преобразователя 9 формируется образцовое напряжение, равное нижней уставке.

По сигналу,"Отсутствие запроса" с выхода 19 блока 2 ЭВМ устанавливает

55 управляющее слово 111 1110100 и в счетчик 8 записывается код верхней уставки. Между этими моментами времени триггеры 11 .каналов, в которых измеряемые сигналы меньше нижней устав-. ки, устанавливаются в ноль. Каналы, сработавшие при образцовом напряжении, равном верхней уставке, опрашиваются и их номера записываются в память 55. Таким образом, режим контроля "Зона" осуществляется в два такта. Модификациями данного режима являются: режим "Меньше заданного", реализуется в режиме "Зона" при равенстве 0 нижней уставки, режим

"Больше заданного", реализуется в режиме "Зона" при равенстве верхней уставкн границе диапазона.

Число измеряемых величин, записанных в блоки 55 памяти передается в

ЭВМ из счетчика 49 буферной памяти 3.

Буферная память 3 работает под управлением управляющих сигналов и обеспечивает различные режимы функционирования: режим записи по проиэволь« ному адресу, режим записи с последовательной адресацией в предварительно установленную зону адресного простраиства, режим считывания по произвольному адресу, режим считывания массивом с предварительно установлен-. ной зоной адресного пространства.

Кроме того, в режиме записи с последовательной адресацией обеспечивается подсчет числа импульсов записи и возможность считывания его внешним устройством (ЭВМ) с выходов 20 буферной памяти З..Во всех режимах работы буферной памяти 3 обеспечивается формирование извещающих сигналов на выходе 19, Е 1 - разрешение считывания словом, 2 2 -:разрешение записи, Z 3 — разрешение считывания массивом, которые могут быть использованы ЭВМ при управлении устройством.

Буферная память 3 состоит из модулей двухпортовых блоков 55 памяти, находящихся в режиме считывания по адресным входам считывания при наличии сигнала разрешения на первом управляющем входе..При изменении адреса считывания Ad R изменяется информация на выходе блоков 55 памяти.

Запись данных (вход данных) осуществляется по адресу записи AdW при наличии импульсов записи и сигнала разрешения записи на втором управляющем входе блоков 55 памяти. Адрес записи

1453397

1. Многоканальное устройство для ввода аналоговых данных, содержащее компараторы, триггеры, элементы И первой группы, элементы И второй группы, элементы ИЛИ, первый блок формирования приоритетного адреса, .буферную память, блок управления, цифроаналоговый преобразователь и первый счетчик, С-вход которого соединен с первым выходом блока управления, группа выходов с второго по девятый которогс соединена с управляющими входами буферной памяти, входы данных которого соединены с входами цифроаналогового преобразователя и информационными выходами первого счетчика, выход переполнения которого соединен с входом конца цикла блока управления, вход запроса которого сои адрес считывания буферной, памяти 3 разделены на две части из Р1 и Р2 разрядов. Р! младших разрядов используется для задания произвольного адреса в соответствующем режиме в зоне памяти, устанавливаемой Р2 старшими разрядами.

Сигналы с выхода блока 7 управления, соответствукнцие установленному 10 режиму работы устройства, переводят счетчики 49-51 в заданный режим. В режиме записи по произвольному адресу в начале ЭВМ устанавливает старшие Р2 разряда адреса записи AdM в 15 соответствии с кодом выбранной зоны записи. После этого формируется cur It l1 нал Пуск и при возникновении сигнала "Запрос" на втором и третьем выходах блока 7 управления формиру- 20 ются. импульсы записи адреса в счетчик 49 (мпадшие Р1 разрядов) и в соответствующую ячейку выбранного блока 55 памяти. При этом Р1 = К1 + К2.

При завершении цикла измерения сигнал "Конец цикла" поступает с восьмого выхода блока 7 управления через элемент ИЛИ 48 на С-вход счетчика 5! буферной памяти 3, увеличивая код .номера зоны (Р2 = Р2 + !), и цикл из» 30 мерения (записи) может быть повторен.

Частным случаем описанного режима является запись, начиная с нулевой эоны. Считывание производится аналогичным образом. Вначале ЭВМ устанавливает код AdR который записывается в счетчик 50 сигналом с пятого выхода блока 7 управления. При поступлении импульсов считывания на С- вход счетчика 50 с шестого выхода блока 7 40 управления информация считывается с того модуля блока 55 памяти, номер которого соответствует установленному в старших Р2 разрядах адреса с Фтывания в счетчике 50.

Блок 54 управления обеспечивает непрерывный режим записи и считывания и формирует оповещающие сигналы для предотвращения потерь информации.

Сигналы Е 1 и Z 3 целесообразно В0 использовать для управления вводом информации в ЭВМ, например в качестве запросов на обслуживание в эависимос» ти от требуемого режима работы. Z 1 и Е 3 формируются (устанавливаются в активное состояние) идентичным образом как сигналы неравенства соответственно младших Р! и старших Р2 разрядов записи и считывания. Равенство адресов записи и считывания возможно в двух случаях: в исходном состоянии и всегда, когда буферная память 3 пуста, при заполнении всей памяти 3. Для различения этих ситуаций используется сигнал, формирующийся при переполнении третьего счетчика 51, формирующего старшие Р2 разряда адреса записи и сбрасывающийся при переполнении второго счетчика 50, формирующего адрес считывания ° Совместное появление сигналов 2 2 и Е 3 означает, что в буферной памяти нет свободных зон записи результатов измерения или контроля. Наличие выходов

Z Z 2, 2 3 блока 54 управления позволяет сократить время запаздывания ввода информации в ЭВМ и организовать режим непрерывной записи и считывания в течение нескольких циклов работы устройства, а также производить запись и считывание из (в) заданной soны как упорядоченным сообщением, так и по произвольному адресу отдельными словами, т.е. обладает более широкими функциональными возможностями по сравнению с известным устройством.

Новые функциональные возможности буферной памяти по сравнению с известным устройством позволяют расширить область применения предлагаемого устройства на класс систем, обеспечивающих непрерывную работу, например непрерывное измерение и контроль с необходимостью последукпцего восстановления процессов на входе системы.

Формула изобретения единен с выходом запроса первого блока формирования приоритетного адреса, выходы позиционного кода которого соединены с соответствующими адресными входами записи буферной памяти, выходы первой и второй групп которой являются информационными выходами устройства, выходы унитарного кода первого блока формирования приоритетно- 10

ro адреса соединены с первыми входами соответствующих элементов И первой и второй групп, вторые входы элементов И второй группы соединены .с выходом сброса блока управления, ин- 15 формационный вход которого является управляющим входом устройства, информационными входами которого являются одни входы компараторов, другие входы которых соединены с выходом цифро- 20 аналогового преобразователя, выход каждого компаратора соединен с С-входом соответствующего триггера, выходы которых соединены,с вторыми входами соответствующих элементов И первой 25 группы и входами соответствующих элементов ИЛИ, выход каждого элемента

ИЛИ соединен с соответствующим входом первого блока формирования приоритетного адреса, Э-входы всех триггеров .30 соединены с шиной логической единицы устройства, первые входы сброса соответствующих триггеров соединены с выходом соответствующего элемента И второй группы, о т л и ч а ю щ е ес я тем, что, с целью расширения функциональных возможностей, в устройство дополнительно введены второй блок формирования приоритетного адреса, блок сравнения и второй счетчик, 40

R-входы первого и второго блоков формирования приоритетного адреса соединены с четырнадцатым выходом блока управления, десятый выход блока управления соединен с управляющим вхо- 45 дом второго счетчика, одиннадцатый выход блока управления соединен с управляющим входом первого счетчика, двенадцатый выход блока управления соединен с управляющими входами пер 50 вого и второго блоков формирования приоритетного адреса, тринадцатый выход блока управления соединен с входом управления изменением направления счета первого счетчика, пятнадцатый выход блока управления соединен с входом сброса первого счетчика, информационные выходы первого и второго счетчиков соединены соответственно

13 1453397 14 с первыми и вторыми входами блока сравнения, выход которого соединен с входом окончания контроля блока управления, вход конца поиска ранга которого соединен с выходом переполне- . ния второго счетчика, С-вход которого соединен с четвертым выходом блока управления, вход начала записи ранга которого соединен с выходом переполнения буферной памяти, выходы соответствующих элементов И первой группы объединены и соединены с соответствующими информационными входами второго блока формирования приоритетного адреса, выходы позиционного кода которого соединены с соответствующими адресными входами записи буферной памяти, вторые входы сброса соответствующих триггеров объединены и подключены к выходам унитарного кода второго блока формирования приоритетного адреса, входы адреса считывания буферной памяти, входы данных первого и второго счетчиков, а также входы данных первого и второго блоков формирования приоритетного адреса являются управляющими входами устройства, выход запроса первого блока формирования приоритетного адреса является выходом запроса устройства.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок управления содержит генератор импульсов, три триггера, два счетчика, восемь элементов И, три элемента ИЛИ, регистр кода операции и мультиплексор, D-вход первого триггера является входом запроса блока управления, С-вход соединен с выходом первого элемента

ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ и третьим выходом.первого счетчика, управляющий вход которого соединен с прямым выходом первого триггера, инверсный выход которого соединен с управляющим входом второго счетчика, С-вход которого соединен с С-входом первого счетчика и выходом генератора, первый, второй и третий входы мультиплексора соединены с входами окончания контроля, конца цикла, поиска ранга блока управления, выход мультиплексора соединен с первым входом первого элемента И и с первым входом третьего элемента ИЛИ, выход которого соединен с К-входами триггеров и.является пятнадцатым выходом блока управления; второй вход первого

1453397! 6 элемента И соединен с первым входом второго элемента И с пятым выходом регистра кода операции, первый и четвертый выходы которого соединены с входами управления мультиплексора, а первый выход соединен с первыми входами третьего и четвертого элементов

И, вторые входы которых соединены с первым входом пятого элемента И, вто- 1р рым входом третьего элемента ИЛИ, вы- . ход второго триггера соединен с первым входом шестого элемента И, выход которого является первым выходом блока управления, а второй вход шестого 15 элемента И соединен с i-м выходом второго счетчика, (i-1)-й и первый .выходы которого соединены соответственно с вторым входом первого элемента ИЛИ и третьим входом четверто- gp го элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого является выходом сброса запроса блока управления, вторым выходом которого является 2б второй выход первого счетчика, первый выход которого соединен соответственно с вторым и первым входами второго и седьмого элементов И, выходы которых соответственно являются третьим ЗО и четвертым выходами блока управления, пятым выходом которого является третий выход регистра кода операции, четвертый выход. которого соединен с вторым входом седьмого элемента И, выходы восьмого, пятого, первого элементов И являются соответственно шестым-восьмым выходами блока управле"ния, девятым выходом которого являет" ся инверсный выход третьего триггера

D-вход которого соединен с шиной логического нуля устройства, а S-входс восьмым выходом регистра кода опе-рации, выходы с десятого по тринадцатый блока управления соединены со- 4S ответственно с выходами с шестого по девятый регистра кода операции, второй.и третий выходы которого соединены соответственно с вторыми входами пятого и восьмого элементов И, выход третьего элемента И является четырнадцатым выходом блока управления, вход начала записи ранга которого соединен с -входом третьего триггера, второй вход третьего элемента ИЛИ, S-вход второго триггера, первый вход восьмого элемента И, входы регистра кода операции. являются информационным входом блока.

3. Буферная память, содержащая блоки памяти, первый, второй и третий счетчики, элемент ИЛИ, первый дешифратор и блок управления, причем группа выходов первого счетчика соединена с адресньвах входами записи блоков памяти, первая группа выходов второго счетчика соединена с входами первого дешифратора, первая группа входов данных блоков памяти является входами данных буферной памяти, а входы данных первого счетчика являются адресными входами записи буферной памяти, выходы блоков памяти яв ляются первой группой выходов буферной памяти, выходы блока управления являются второй группой выходов буферной памяти, вход сброса третьего

I счетчика соединен с входом сброса второго счетчика, выход элемента ИЛИ соединен со счетным входом третьего счетчика, о т л,и ч а ю щ а я с я тем, что, с целью расширения области применения за счет обеспечения непрерывной записи и одновременного считывания, в нее введен второй дешифратор, входы которого соединены с группой выходов третьего счетчика, адресные входы считывания блока памяти соединены с второй группой выходов второ о счетчика, группы информационных входов блока управления подключены соответственно к выходам перво- . го второго и третьего счетчиков, группа выходов первого счетчика является первой группой выходов буферной памяти, одноименные выходы первого и второго дешифраторов соединены соответственно с нервымн и вторыми управляющими входами соответствующих блоков памяти, выход переполнения первого счетчика соединен с первым входом элемента ИЛИ и является выходом переполнения буферной памяти, Г входы данных первого счетчика соединены с второй группой входов данных . блоков памяти, выходы переполнения третьего и второго счетчиков соединены соответственно с первым и вторым счетными входами блока управления, входа! записи блоков памяти объединены и являются первым управляющим входом буферной памяти, управляющие входы первого и третьего счетчиков объединены и являются вторым управляющим входом буферной памяти, третьим, четвертым и пятым управляющими входами которой являются соответственно

1453397

Фи@ 2 счетный вход первого счетчика, управляющий и счетный входы второго счетчика, входы сброса первого счетчика и блока управления соединены с входом сброса второго счетчика и являются шестым управляющим входом буферной памяти, седьмым и восьмым управляющими входами которой являются соответственно второй вход элемента ИЛИ и вход разрешения записи блока управления.

1453397

Составитель С.Кулиш

Техред А. Кравчук Корректор С.Черни

Редактор Л.Гратилло

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Заказ 7284/45 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1l3035, Москва, Ж-3$, Раушская наб., д. 4/5