Устройство для сбора информации

Иллюстрации

Показать всеРеферат

Изобретение относится к телеметрии -и предназначено для сбора информации с частотных датчиков. Цель изобретения - снижение энергопотребления путем обеспечения информационной гибкости. Устройство содержит :датчики 1, триггеры 2, коммутаторы 3, 4, блок 5 памяти, генератор 6, триггеры 7-10, компаратор 11, элемент ИЛИ-НЕ 12, элемент ИЛИ 13, элементы И 14-21, счетчик 22, элементы 23, 24 НЕ, В условиях автономной буйковой станции с измерительной аппаратурой на борту целесообразно запретить опрос.блока памяти и узлов, участвующих в суммировашга считанного бита информации и состояния триггера переноса, после установки переноса в нулевое состояние, поскольку дальнейшее обращение к блоку памяти заключается в чтении из калщой ячей- .ки информации и записи этой же информации в ту же ячейку, что является излишним. При этом за счет временного прекращения работы некоторых элементов устройства потребление электроэнергии устройствомуменьшается. 1 ил. а (Л

СООЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„ЯО„„45З4З6 ц1> 4 G 08 С 19/28

ПРИ ГКН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

Т СССР

М АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4289641/24-24 (22) 30.06.87 (46) 23.01.89. Бюл. К - 3 (71) Морской гидрофизический институт АН УССР и Львовский политехнический институт им. Ленинского комсомола. (72) О.А.Губанов, В.Л.Котляров, С.В. Мотыжев и Л.В. Ольшевская (53) 621.388 (088 ° 8) (56) Авторское свидетельство СССР

Ф 404116, кл. G 08 С 19/28, 1973.

Авторское свидетельство СССР

Р 1262554, кл. С 08 С 19/28, 1986. (54) УСТРОЙСТВО ДЛЯ СБОРА ИНФОРМАЦИИ (57) Изобретение относится к телеметрии и предназначено для сбора информации с частотных датчиков. Цель изобретения — снижение энергопотребления путем обеспечения информационной гибкости. Устройство содержит датчики 1, триггеры 2, коммутаторы

3, 4, блок 5 памяти, генератор 6, триггеры 7-10, компаратор 11, элемент ИЛИ-НЕ 12, элемент ИЛИ 13, элементы И 14-21, счетчик 22, элементы

23, 24 НЕ. В условиях автономной буйковой станции с измерительной аппаратурой на борту. целесообразно запретить опрос. блока памяти и узлов, участвующих в суммировании считанного бита информации и состояния триггера переноса, после установки переноса в нулевое. состояние, поскольку дальнейшее обращение к блоку памяти заключается в чтении из каждой ячей.ки информации и записи этой же информации в ту же ячейку, что является излишним. При этом за счет временного прекращения работы некоторых эле" ментов устройства потребление элект" роэнергии устройством уменьшается. ил.

1453436

Изобретение относится к телеметрии и предназначено для использования в океанографических исследованиях для измерения гидрометеорологических полей.

Цель изобретения - снижение энергопотребления путем обеспечения ин.формационной гибкости.

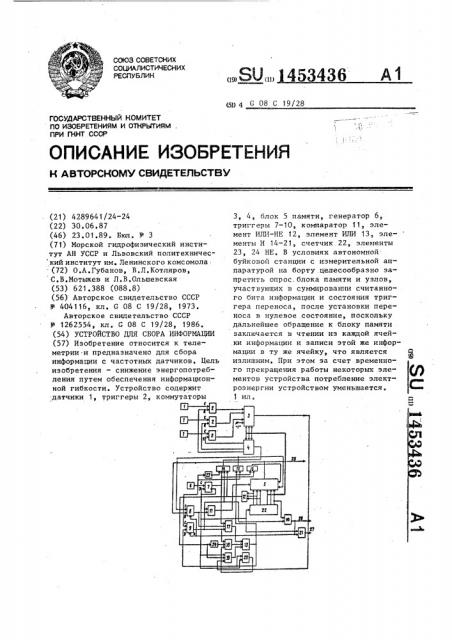

На чертеже представлена структур" 10 ная схема устройства для сбора информации.

Устройство содержит датчики 1, триггеры 2, коммутаторы 3 и 4, блок

5 памяти, генератор 6, триггеры 7-10, 15 компаратор 11, элемент ИЛИ-НЕ 12, элемент ИЛИ 13, элементы И 14-21, счетчик 22, элементы.НЕ .23 и 24 и выходы 25-27 устройства.

Устройство работает следующим образом.

На входы устройства поступают сигналы от датчиков 1 гидрометеорологических параметров с частотным выходом. Каждый импульс от датчика устанавливает один из триггеров 2, на который он поступает, в " 1". При этом максимальная частота от каждого датчика не должна превышать частоты импульсов переполнения счетчика 22 адресов, на вход которого от генератора 6 тактовых импульсов через делитель на 2 (триггер 7 управления) непрерывно поступают импульсы с частотой Ет /2, где Кг — частота генератора 6. Таким образом, частота импульсов переполнения счетчика 22 равна

Е. /2N, где Я - число состояний счетчика. 22, равное числу используемых ячеек блока 5 (ОЗУ). Когда k младших 40 разрядов .счетчика.22.адресов. окажутся.в "О", что соответствует адресу младшего разряда по какому-либо из каналов, то на выходе элемента ИЛИ-НЕ

12 ПОЯвитсЯ -.1 е При этОм триггер 45 управления будет вначале в "О", на выходах элементов И 17 и 18 - "О", на выходах элементов И 19 и ИЛИ 13—

"1" (если при.этом соответствующий триггер. 2 входа находится. в состоянии 1). Сигнал ".1" с выхода элемента

ИЛИ 13 Разрешает работу элементов

И 15, 16 и 20. Ближайший отрицательный тактовь и импульс производит чтение информации иэ ячейки блока 5,, в котором. хранится младший разряд числа по каналу,.номер которого в это время находится, в старших (ш-.k) разрядах. счетчика адресов ОЗУ 5. Задний фронт отрицательного тактового импульса переносит прочитанный из

ОЗУ 5 бит информации В триггер 8 разрядов и состояние входного триггера

2 в триггер, 9 переноса через элементы 19 и 13. После этого на выходе компаратора 10 образуется .разряд суммы в этот же младший разряд ОЗУ 5, а на выходе элемента ИЛИ 13 - единица переноса для следующего разряда.

При.этом, если. триггер 9 переноса установлен в такте чтения из ОЗУ, то соответствующий входной триггер

2 импульсом с выхода элемента И 14 в такте записи будет установлен в. "О" и готов.к приему следующего входного импульса по этому каналу. . После поступления импульса в счетчик 22 адресов в такте чтения снова производится отрицательным тактовым импульсом чтение .бита информации из

ОЗУ 5 в триггер 8 разряда ° Задним фронтом отрицательного тактового импульса этот триггер устанавливается в состояние прочитанного из ОЗУ 5

Разряда. Триггер 9 переноса в это время подтверждается в том состоянии, В котором он находился до сих порр так как в это время его выход через элемент И 18 и элемент ИЛИ 13 подключен к его D-входу. Затем в такте записи результат суммирования в данном разряде, .который образуется на выходе компаратора 11, записывается в

ОЗУ 5, а результат определения пере-. носа для следующего разряда с выхода элемента И 17 через элемент ИЛИ 13 записывается в триггер 9 переноса.

После добавления в счетчик 22 àäðåсов одного импульса снова происходит чтение бита информации В триггер 8 разряда, определение очередного разряда суммы компаратором 11, определение очередного разряда переноса в следующий старший разряд элементом

И 17 и запись результата определения суммы в ОЗУ 5 и результата определения переноса в триггер 9 переноса и т.д.

Таким образом, после каждого чтения бита информации из ОЗУ 5 в триггере 8 разряда появляется прочитанный бит, а триггер 9 переноса (sа исключением такта чтения младшего разряда по каждому из каналов) остается в прежнем состоянии. Затем в

ОЗУ 5 записывается сумма, определенная для данного разряда, а в триггер

36

4 ный, выполненный,. например, на ре гистре сдвига, в который информация заносится отрицательным фронтом тактового импульса с выхода. элемента

И 21, откуда или.непосредственно с выхода. устройства она поступает через радиоканал потребителю.

Изобретение. позволяет ограничить работу блока памяти в динамическом режиме и снизить тем самым энергопотребление. Положительный эффект достигается за счет того, что наличие нуля в разряде переноса обозначает, что состояние последующих бо- . лее старших разрядов части блока памяти, отведенной под хранение информации с опрашиваемого. датчика, не изменится.в данном цикле и опрос этой части блока можно прекратить до следующего цикла опроса датчиков, Исключение опроса старших разрядов части

1 блока памяти, определенной под информацию с одного датчика, приводитк снижению энергопотребления.

Формула,из о бр ет ения

I.

Устройство для сбора информации, содержащее датчики, выходы которых соединены с первыми входами соответствующих триггеров группы, выходы которых подключены к соответствующим входам первой группы первого коммутатора, второй коммутатор, выходы. которого соединены с вторыми входами триггеров группы, счетчик адреса, выходы первой группы которого соеди-.

3 иены с соответствующими входами элемента ИЛИ-НЕ и первыми адресными входами блока памяти, выходы. второй группы счетчика адреса соединены с соответствующими входами первого и второго коммутаторов и вторыми адресными входами блока памяти, выход которого является выходом устройства, генератор, выход которого подключен через инвертор к первому входу первого элемента И и непосредственно к первым входам первого и второго триггеров, инверсный выход первого триггера соединен со своим вторым входом, с входом счетчика адреса, с первыми входами второго и третьего элементов И, прямой выход первого триггера подключен к второму входу первого элемента И и первому входу четвертого элемента И, выход второго триггера соединен с первыми входами третьего триггера, компара3 14534

9 переноса заносится результат определения переноса для следующего разряда, Когда результат определения переноса в следующий разряд ОЗУ 5 станет равным "О" (сигнал на выходе элемента ИЛИ 13, свидетельствующий о том, что следующие разряды ОЗУ 5 останутся без изменения, прекратится опрос ОЗУ 5 и переключение триг- 10 гера 8 разряда, так как при этом на выходе элементов 15, 16 и 20 будут нули.

После добавления импульса, посту-, пившего в один из входных триггеров 15

2, к числу, накопленному в ячейках

ОЗУ, выделенных для одного из каналов, старшие m — k разрядов счетчика 22 адресов увеличивают свое состояние на единицу. При этом переклю- 20 чаются коммутаторы 3 и 4.и опрашивается во время чтения младшего бита информации по .следующему разряду входной триггер 2 следующего канала.

Когда m — k старших разрядов счет- 25 чика 22 адресов станут в состояние

111...11, будет опрашиваться служебный канал, по которому импульс добавляется всегда благодаря подаче ".1" на последний вход коммутатора 3. При 30 этом соответствующий сигнал с выхода коммутатора 4 никуда не поступает, так как входной триггер по служебному каналу отсутствует.

Когда во всех ячейках ОЗУ 5, которые относятся к служебному каналу, будут единицы (при всех состояниях младших к-разрядов счетчика 22 адресов, когда его старшие m — k .ðàçрядов в единицах), триггер 9 пере- . 40 полнения при добавлении очередной единицы в служебный канал будет в (1" и сохраняет свое состояние вплоть до переполнения счетчика 22 адресов

ОЗУ 5. При переполнении в этом слу- 45 чае счетчика 22 триггер 10 выдачи будет установлен в "1" и начнется выдача накопленной информации из блока 5 и его обнуление.

Благодаря установке триггеров 8. 50 и 9 в нулевое состояние в ОЗУ 5 с выхода компаратора 11 будут записаны нули. В то же время информация с выхода "Установка" ОЗУ 5 (выход 25), поступающая в сопровождении тактовых импульсов (выход 27 устройства) и сигнала "Выдача " .(выход 27 устройства), может быть записана в преобразователь последовательного кода в параллель1453436

Составитель 3.Низамутдинова

Техред М.Ходанич Корректор И.Муска

Редактор Н.Тупица

Заказ 7287/47

Тираж 518

Подписное

8HHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 тора, пятого элемента И, третьим входом первого элемента И и вторым входом четвертого элемента И, выход четвертого триггера подключен к вто5 рым входам компаратора и третьему

1 входу четвертого элемента И, выход элемента HJIH-HE соединен с четвертым входом первого элемента И и вторым входом третьего элемента И и через второй элемент НЕ с вторым входом пятого элемента И, выход первого элемента И подключен к входу второго коммутатора, элемент ИЛИ, выход которого соединен с вторым входом второго триггера, последний выход второй группы счетчика адреса соединен с вторым входом третьего триггера, выход которого является вторым выходом устройства и подключен к третьему ! входу второго триггера, первому вхо ду четвертого триггера и второму. входу второго элемента И, выход которого является третьим выходом устройства, выход первого коммутатора подключен к третьему входу третьего элемента И, выход компаратора соединен с информационным входом блока памяти, о т л и ч а ю щ е е с я тем, что, с целью снижения энергопотребления путем обеспечения информационной гибкости, в него введены шестой, седьмой и восьмой элементы И, первые входы которых соединены с выходом элемента ИЛИ, второй вход шестого элемента И подключен к выходу генератора, второй вход седьмого элемента И соединен с.прямым выходом первого триггера, к инверсному выходу которого подключен второй вход восьмого элемента И, выходы шестого и седьмого элементов И подключены соот.ветственно к управляющему и синхронизирующему входам блока памяти, вторОй и третий входы четвертого триггера соединены соответственно с выходом блока памяти и шестого элемента И.