Способ управления стабилизированным выпрямителем

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может бьп-ь использовано . для управления тиристорньй стабилизированньм выпрямителем, предназначенным для стабилизации уровня выходного напряжения при изменяющихся параметрах нагрузки. Целью изобретения является улучшение качества стабилизации выходного напряжения вьррямителя в переходных процессах. С помощью источника эталонных напряжений 1 формируют сигнал задания, из которого на сумматоре 2 вычитают выходное напряжение вьптрямителя 8, сглаженное силовым фильтром 9. Сигнал ошибки усиливают и интегрируют с помощью пропорхщонально-интегрального звена 3 и регулируют фазу импульсов управления . Для повышения качества стабилизации выходного напряжения в переходных режимах определяют максимальное и минимальное значения выходного напряжения на нагрузке 10 выпрямителя 8 в статических режимах, формируют с помощью источников 13, 14 два эталонных сигнала, один из которых больше максимального, а другой меньше минимального измеренных значений выходного напряжения в статических режимахо Выходное напряжение вычитают из первого и второго эталонных сигналов в сумматорах 11, 12 и при больших отклонениях выходного напряжения от номинального значения в динамике выполняют суммирование основного сигнала ошибки сумматора 2 с первым дополнительным сигналом ошибки сумматора 11 при его отрицательном знаке, и суммируют основной сигнал ошибки со вторым дополнительным сигналом ошибки сумматора 12 при его положительном знаке. 3 ил. ш (Л 4: сд 00 ел ел ел (ptie i

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„.80„„цяддд А1

m 4 Н 02 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4260793/24-07 (22) 15 ° 06.87 (46) 23.01.89. Бюл. Н- 3 (71) Новосибирский электротехнический институт (72) В.В. Иванцов, С.Г, Лажинцев, С.В. Стогов и А.В. Шубнов (53) 621.316.727(088.8) (56) Писарев А,Л. и Деткин Л.П. Управление тиристорными преобразователями. — M. Энергия, 1975, с. 73.

Нипилло В.П. Автоматизированный вентильный электропривод. — М.: Энергия, 1969, с. 324. (54) СПОСОБ УПРАВЛЕНИЯ СТАБИЛИЗИРОВАННИМ ВЬП1РЯМИТЕЛЕМ (57) Изобретение относится к электротехнике и может быть использовано для управления тиристорным стабилизированным выпрямителем, предназначенным для стабилизации уровня выходного напряжения при изменяющихся параметрах нагрузки. Целью изобретения является улучшение качества стабилизации выходного напряжения выпрямителя в переходных процессах. С помощью источника эталонных напряжений 1 формируют сигнал задания, из которого на сумматоре 2 вычитают выходное напряжение выпрямителя 8, сглаженное силовым фильтром 9. Сигнал oBIH5KH усиливают и интегрируют с помощью пропорционально-интегрального звена 3 и регулируют фазу импульсов управления. Для повыпеуия качества стабилизации выходного напряжения в переходных режимах определяют максимальное и минимальное значения выходного напряжения на нагрузке 10 выпрямителя

8 в статических режимах, формируют с помощью источников 13, 14 два эталонных сигнала, один из которых больше максимального, а другой меньше минимального измеренных значений выходного напряжения в статических режимах. Выходное напряжение вычитают из первого и второго эталонных сигналов в сумматорах 11, 12 и при больших отклонениях выходного напряжения от номинального значения в динамике выполняют суммирование основного сигнала ошибки сумматора 2 с первым дополнительным сигналом ошибки сумматора 11 при его отрицательном знаке, и суммируют основной сигнал ошибки со вторым дополнительным сигналом ошибки сумматора 12 при его положительном знаке. 3 ил .

1453555

Изобретение относится к электротехнике и может быть использовано лпя управления тиристорным стабилизированным выпрямителем предназнаУ

5 ченным для стабилизации уровня выходного напряжения при изменяющихся параметрах нагрузки °

Цель изобретения — улучшение качества стабилизации выходного напря- 10 жения выпрямителя в переходных режимах.

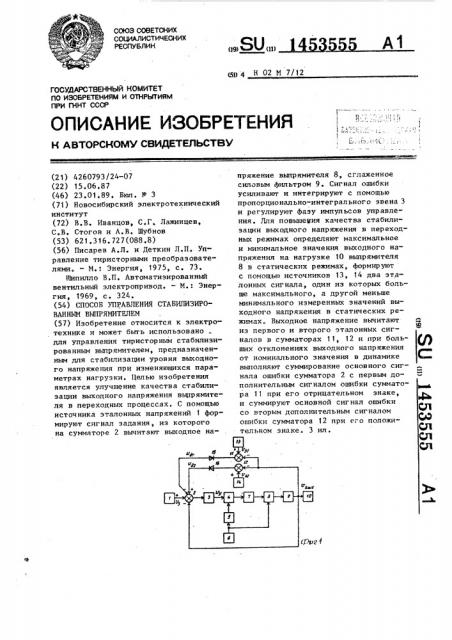

На фиг. 1 приведена структурная схема устройства, реализующего предлагаемый способ; на фиг. 2 — принци-! пиальная электрическая схема части .элементов устройства, с помощью которой формируется управляющий сигнал

Ц„,; на фиг. 3 — диаграммы, поясня ющие способ ° 20

Устройство (фиг. 1) содержит ис точник 1 сигнала задания, выход ко торого через первый вход сумматора 2 подсоединен к входу пропорциональнойнтегрального (ПИ) звена 3. 25

: Выход звена 3 подключен к первому

Входу блока 4 компараторов. Второй

Вход которого 4 соединен с блоком 5

Генераторов опорного напряжения, вход

1 оторого, в свою очередь, подключен ур

К первичному источнику 6 питания. ВыХод блока компараторов через блок 7

1эыходных каскадов соединен с управляющим входом выпрямителя 8. Силовой

Вход управляемого выпрямителя 8 со35 фдинен с выходом первичного источника 6 питания. Выход управляемого выпрямителя 8 через силовой фильтр 9 йодключен к нагрузке 10 и к второму входу сумматора 2, Выход силового фильтра 9, кроме того, соединен с первыми входами сумматоров 11 и 12, вторые входы которых соединены с выходами источников 13 и 14 первого и Второго эталонных сиг налов сооТ 45 ветственно. Выходы сумматоров 11 и

12 соединены соответственно с третьим и четвертым входами сумматора 2 через вентили 15 и 16, которые пропускают соответственно первый дополНительный сигнал отрицательного знака и второй дополнительный сигнал п оложительног о знака.

Устройство содержит также клемму 17 для подключения к источнику 1 сигнала задания, клемму 18 для подключения к выходу силового фильтра 9 управляемого выпрямителя 8, клемму

19 — для подключения к выходу источника 14 второго эталонного сигнала, клемму 20 для подключения к выходу источника 13 первого эталонного сигнала и клемму 21 — выходная клемма для подключения к входу блока 4 компараторов. Второй сумматор 1 t на принципиальной схеме представлен делителем напряжения на резисторах 22 и 23, третий сумматор 12 — на резисторах 24 и 25, выходное напряжение (Б ьы„) вычитается из сигнала задания (П1) эа счет резисторов 26 и 27. Сумматор 2 основного и дополнительного сигналов ошибки и ПИ-звено 3 собраны на операционном усилителе 28, охваченном отрицательной обратной связью с помощью RC-цепочки 29 и 30. Для схемотехнической реализации остальных элементов устройства согласно фиг;1 могут использоваться стандартные элементы преобразовательной техники.

Так, в качестве компараторов блока 4 могут использоваться операционные усилители с большим коэффициентом усиления. Число компараторов равно числу вентилей выпрямителя. Блок 5 генераторов опорного напряжения представляет собой набор генератора напряжения пилообразной формы, синхронизированных с напряжением первичного источника 6 питания, в качестве которого может быть использован автономный синхронный генератор. Управляемый выпрямитель может быть собран по любой известной схеме, например трехфазной мостовой. Силовой фильтр представляет собой, например, одноэвенный Г-образный ?.С-фильтр.

Способ управления стабилизированным выпрямителем осуществляется следующим образом.

Выходное напряжение (V ) источнис ка 1 сигнала задания через первый вход сумматора 2 и ПИ-звено 3 поступает на первый вход блока 4 компараторов. На второй вход блока 4 поступают опорные сигналы из блока 5 генераторов опорных напряжений, которые синхронизированы с напряжением фаз питающей сети первичного источника 6 питания. В блоке 4 компараторов формируются импульсы в моменты равенства опорных сигналов блока 5 и управляющего сигнала с выхода блока 4, которые усиливают по мощности в блоке 7 выходных каскадов и подают на тиристоры управляемого выпрямителя 8, который преобразует переменное

14 .)35 напряжение источника питания 6 в постоянное напряжение. Вькодное напряжение выпрямителя 8 сглаживается фильтром 9 и поступает на нагрузку 10.

Также это напряжение вычитается из сигнала задания с помощью сумматора

2 и поступает на первые входы сумматоров 11 и 12. В результате вычитания выходного напряжения из сигнала задания и интегрирования основного сигнала ошибки с помощью ПИ-звена 3 управляющий сигнал регулируется до тех пор, пока среднее значение выходного напряжения выпрямителя, снимаемое с выхода фильтра 9, не станет равно сигналу задания °

Таким образом, в статических редкимах работы среднее значение выходного напряжения управляемого выпря/ мителя стабилизируется равным сигналу задания за счет астатического характера регулирования управляющего сигнала, придаваемого системе интегральной частью ПИ-звена 3. В стати- 25 ческих режимах возможны лишь небольшие отклонения выходного напряжения от сигнала задания за счет пульсаций выходного напряжения и эа счет температурной нестабильности элементов 30 системы управления. В динамических режимах работы системы, вызванных скачкообразными изменениями нагру- . зок 10 и напряжения первичного источника 6 питания возможны значительные отклонения выходного напряжения от сигнала задания. При появлении таких ч отклонений интегральная часть ПИ-звена 3 не успевает быстро регулировать управляющий сигнал, однако пропорцио- 4р нальная часть ПИ-звена пропускает сигнал ошибки беэ задержки и позволяет быстро регулировать управляющий сигнал. Поэтому в переходных режимах управляющий сигнал пропорционален сумме сигнала ошибки и интеграла от сигнала ошибки, причем такое суммирование осуществляется в самом ПИ-звене 3 за счет последовательного соединения сопротивления 29 и конденсатора 30.

Для повьгпения быстродействия и точности стабилизации выходного напряжения коэффициент усиления ПИ-звена выбирают как можно болыялм, а по55 стоя иную интегрирования flo возможности меньшей. Условия такого выбора ограничены устойчивостью системы регулирования и и". еют т полне спредел н55

4 ные пределы. 3а счет ограниченной устойчивости регулирования в системе могут возникнуть автоколебания, что заставляет ограничивать коэффициент усиления пропорциональной части

ПИ-звена и не позволяет реализовать высокое быстродействие и точность стабилизации выходного напряжения в динамике только за счет одного основного канала регулирования управляющего сигнала. Для устранения этого недостатка осуществляется дополнительное регулирование управляющего сигнала в переходных режимах sa счет двух дополнительных каналов обратной связи, реагирующих порознь на большие увеличения и уменьшения выходного напряжения управляемого выпрямителя.

Дополнительные каналы регулирования (фиг, 1) содержат два сумматора

11 и 12, два источника 13 и 14 эталонных сигналов, вентили 15 и 16. ,Первый эталонный сигнал источника 13 выбирают большим максимального значе ния выходного напряжения (0п,„) в статических режимах работы, а второй эталонный сигнал источника 14 выбирают меньшим минимального значения выходного напряжения в статических режимах (фиг. За). Изменение вькодного напряжения в статических режи" мах определяют заранее расчетным или экспериментальным путем. При небольших изменениях выходного напряжения (U „„ ) в статических режимах первый дополнительный сигнал ошибки на выхо. —, де сумматора 11 .имеет положительньпЪ знак, а второй дополнительный сигнал ошибки на выходе сумматора 12 имеет отрицательный знак, оба вентиля 15 и 16 закрыты и не пропускают выходные сигналы сумматоров 11 и 12 на вход сумматора 2. При этом на входе

ПИ-звена действует сигнал ошибки, пропорциональньп только сигналу разности между сигналом задания и выходным напряжением и формирование управляющего сигнала осуществляется пропорционально сумме сигнала ошибки и интеграла сигнала ошибки. При этом коэффициент усиления и постоянную времени ПИ-звена выбирают предельно возможным по условиям устойчивости системы в статических режимах.

В переходном реп;име эа счет ограниченного коэфф1щиента усиления и быстродействия ПП-эгенл возникают

53555

35

5 14 значительные отклонения выходного напряжения {U „,„ ) от сигнала задания (U ) и в этих режимах осуществляется дополнительное регулирование уп-, равляющего сигнала дополнительными каналами, позволяющее уменьшить от:клонения выходного напряжения по

,сравнению с регулированием сигнала ! ! ,только по основному каналу управления. Так, при сбросе нагрузки {фиг.3, момент времени t ) появляется выброс выходного напряжения, превышающий первый эталонный сигнал (U, ).В результате знак первого дополнительного ,сигнала сумматора 11 изменяется на ! ,отрицательный, вентиль 15 открыва,ется и дополнительный отрицательный

1 сигнал поступает через третий вход ! сумматора 2 на вход ПИ-звена. В реультате входной сигнал ЛИ-звена авен сумме основного сигнала ошиби и первого дополнительного сигнаа и имеет отрицательный знак, а

ыходной сигнал ПИ-звена быстро меньшается и увеличивает углы упавления вентилями преобразователя, что приводит к уменьшению выходного напряжения выпрямителя. Начиная с

Момента времени (фиг. 3), выходное напряжение Б ы„ становится меньше первого эталонного сигнала (U, ), и вентиль 15 снова закрывается, отключая дополнительный канал регули1 ования управляющего сигнала. Аналогично работает второй дополнительный канал регулирования при уменьшении выходного напряжения (Б „„) ниже второго эталонного сигнала (U з ) на интервале времени - „ (фиг. 3), но с той разницей, что сигнал с выхода сумматора 12 в переходном режиме имеет положительный знак, увеличивающий дополнительно входной сигнал ПИ-звена, что сопровождается быстрым увеличением управляющего сигнала на выходе ПИ-звена и быстрым увеличением выходного напряжения выпрямителя.

За счет суммирования основного

Сигнала ошибки и дополнительного сигнала на входе ЛИ-звена в переходных режимах уменьшается отклонение выходного напряжения по величине и по времени по сравнению с регулированием управляющего сигналя только с помощью одного основного канала. Поскольку в статических режимах осуществляется регулирование управляющего сигнала пропорционально сумме основного сигнала ошибки н интеграла от сигнала ошибки с коэффициентом пропор циональности и постоянной интегрирования, выбранным по условиям устойчивости системы регулирования, то в статических режимах система устойчива, автоколебания не возникают и выходное напряжение стабилизируется с высокой точностью. В переходных режимах осуществляется дополнительное суммирование первого либо второго дополнительного сигнала с основным сигналом ошибки, что приводит к повышению быстродействия регулирования.управляющего сигнала. Устойчивая работа системы при этом сохраняется, так как при уменьшении отклонения выходного напряжения дополнительное суммирование и регулирование управляющего сигнала прекращается, что не позволяет возникнуть автоколебаниям в системе. Повьппение быстродействия регулирования управляющего сигнала позволяет уменьшить отклонения выходного напряжения управляемого выпрямителя в переходных режимах и повысить качество его стабилизации.

Таким образом, предлагаемый способ позволяет, повысить качество стабилизации выходного напряжения в переходных режимах. формула изобретения

Способ управления стабилизированным выпрямителем, заключающийся в том, что формируют сигнал задания выходного напряжения выпрямителя, измеряют выходное напряжение выпрямителя, формируют основной сигнал ошибки, пропорциональный разности сигнала задания выходного напряжения вьптрямителя и сигнала, пропорционального выходному напряжению выпрямителя, формируют управляющий сигнал, пропорциональный сумме основного сигнала ошибки и интеграла от основного сигнала ошибки, при этом коэффициент пропорциональности и постоянную времени интегрирования выбирают по условиям устойчивости стабилизаций выходного напряжения выпрямителя, формируют опорные сигналы, синхро- низированные с напряжениями фаз питающей сети, в моменты равенства! !! ! !! !! !

I !

Составитель А. Меркулова

Редактор Н. Яцола Техред М.Ходанич Корректор Г. Решетник

Заказ 7298/53 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

/ 145355 которых управляющему сигналу, формируют импульсы управления тиристорами выпрямителя, о т л и ч. а ю щ и йс я тем, что, с целью повышения качества стабилизации выходного на5 пряжения выпрямителя в переходных режимах, определяют максимальное и минимальное зчачения выходного напряжения выпрямителя в статических 1о режимах, формируют первый эталонный сигнал, значение которого превышает укаэанное максимальное значение выходного напряжения, и второй эталонный сигнал, значение которого не пре- 1g вышает указанное минимальное значение выходного напряжения, формируют первый дополнительный сигнал ошибки, 5

8 пропорциональный разности первого эталонного сигнала и сигнала, пропорционального выходному напряжению выпрямителя, и второй дополнительный сигнал ошибки, пропорциональный pasности второго эталонного сигнала и сигнала, пропорционального выходному напряжению выпрямителя, и в случае, если первый дополнительный сигнал ошибки имеет отрицательное значение, осуществляют суммирование основного и первого дополнительного сигналов ошибки, а в случае, если второй дополнительный сигнал ошибки имеет положительное значение, осуществляют суммирование основного и второго дополнительного сигналов ошибки.