Устройство приема сигналов с относительной фазовой манипуляцией

Иллюстрации

Показать всеРеферат

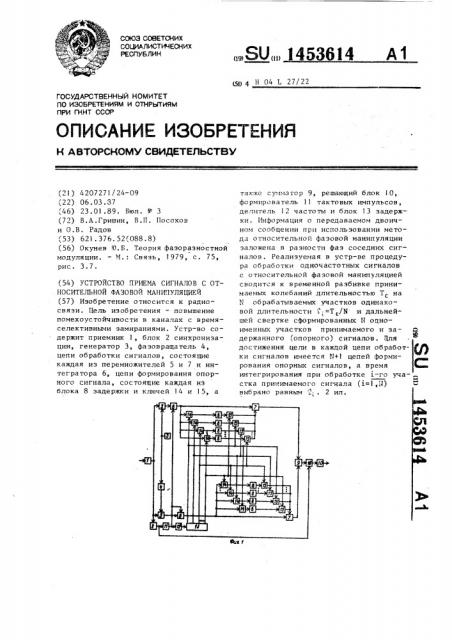

Изобретение относится к радиосвязи . Цель изобретения - повышение помехоустойчивости в каналах с времяселективными замираниями. Устр-во содержит приемник 1, блок 2 синхронизации , генератор 3, фазовращатель 4, цепи обработки сигналов, состоящие каждая из перемножйтелей 5 и 7 и интегратора 6, цепи формирования опорного сигнала, состоящие каждая из блока 8 задержки и ключей 14 и 15, а также сут.1матор 9, решающий блок 10, формирователь 11 тактовых импульсов, делитель 12 частоты и блок 13 задержки . Информация о передаваемом двоичном сообщении при использовании метода относительной фазовой манипуляции заложена в разности фаз соседних сигналов . Реализуемая в устр-ве процедура обработки одночастотных сигналов с относительной фазовой манипуляцией сводится к временной разбивке принимаемых колебаний длительностью Т на К обрабатываемых участков одинаковой длительности и дальнейшей свертке сформированных N одноименных участков принимаемого и задержанного (опорного) сигналов. Цля достижения цели в каждой цепи обработки сигналов имеется N+ цепей формирования опорных сигналов, а время интегрирования при обработке 1-го уча- ,., стка принимаемого сигнала (,Ы) вьйрано равным С- . 2 ил.

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСГ1УБЛИМ

15У 4 Н 04 1. 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ДВТОРСНОЬЛУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬ1ТИЯМ

ПРИ ГКНТ СССР (21) 4207271/24-09 (22) 06.03.37, 46) 23.01.89. Бюл. М 3 (72) В.А.Гришин, В.П. Посохов и O.В. Радов, 53) 621. 376. 52(088.8) (56) Окунев Ю.В. Теория фазоразнастнай модуляции. — 1.: Связь, 1979, с. 75, рис. 3.7. (54) УСТРОЙСТВО !IPHEMA СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ (57) Изобретение относится к радиосвяэи. Цель изобретения — повышение помехоустойчивости в каналах с времяселективными замираниями. Устр-во содержит приемник 1, блок 2 синхронизации, генератор 3, фаэовращатель 4, цепи обработки сигналов, состоящие каждая из перемножителей 5 и 7 и интегратора 6, цепи формирования опорного сигнала, состоящие каждая из блока 8 задержки и ключей 14 и 15, а

„.SU„, 1453614 А1 также сумматор 9, решающий блок 10, формирователь 11 тактовых импульсов, де",èòåëü 12 частоты и блок 13 задержки. Информация а передаваемом двоичном сообщении при использовании метов да относительной фазавой манипуляции заложена в разности фаэ соседних сигналов. Реализуемая в устр-ве процедура обработки одночастотных сигналов с относительной фазовой манипуляцией сводится к временной разбивке принимаемых колебаний длительностью Тс на

N обрабатываемых участков одинако— вой длительности i.=T /N -и дальнейшей свертке сформированных N одноименных участков принимаемого и за— держаннога,îïîðíîãî) сигналов, цля достижения цели в кажцой цепи обрабат ки сигналов имеется N+l цепей формирования опорных сигналов, а время интегрирования при обработке i-га уча стка принимаемого сигнала (i=i,iJ) выбрано равным ; . 2 ил, 14 53614

Изобретение <з тно сит(.л к радио« вязи и может найти пр.-..мен<-=ние при:-.о— строении приемнико з д :(

Цепью изобретения является повь. шение помех«устойчиво rt. з каналах с времяселек тHHHbIM л эам1. рани ями.

На фиг, 1 и!оиведен"= труктурна я эпект оическая схема ус т зойства приема си.-напов с относитепьной фазовой манип упяцией; на фиг. 2 — временные диаграммы.

Устройство поиема си напов с «тно — 15 ситепьной фаз«вой маньг, упяцией содержит п оиемник 1,. бпо к 2 .".инхрониз» ции,, генератор,, фазоврагцат пь 4, пег.вые перем ложитепи 5, лнтег раторы 6, вто— рые перемнсжитепи 7, блоки 8 эадерж- 20 ки, сумматс р 9,, решакщий блок 1О, формироватепь 1 такт! вьгх импупьсов депитепь 2 частоты, бпок 13 задерж—

1 5 допопнитепьный интегpe тор 16. 25

Устройство оабо тае т =педуюшим об— разом.

Информация о перед=в,3емом дво.!тином сообщ нии при .лс:to.чьэовании метода относитепьной фаз«!зой ма t ïóëÿöèÿ 30 запожзна в разности ф;: э соседних сиг-! напов. Двоичная инф!ор ационная последоватепьность в абсопк!т:лом коде име— ет виц,,изображенный I —;t фиг. 2а, в относительном коде —: — а фиг,2б.

Высокоч-.сто т(л!ое ко.г:.е баяне, прошедшее пи ию (.âëç.ë с врем я елективнь MH замираниями, пос тупае т:-ла вход приемника 1 . В г;риемнике 1:> =уществляе тся предваритепьная обраост<а принимаемо-,10 го сигнала, зак.вючаьэш:я=я в сепекции„ усилении 1л преобраэованли частоты входного колебания. С выхода приемника колебание промажу-!очной частоты поступае.т на первы! входы первых пе— ремножиггепей 5 двух в!з т:зей обработки сигналов !- на:зход 0J c,à 2 синхр«ни— зации., B к«тором «сушь с гвпяется выдепение ttç принимаемого к!зпебания информации о грани ах инфо змационных посылок и формиоовани!= синхросигнапов дпите.п иост ю d C, . -

На фиг, 2ж иэоб раже - -1 поспедова— тепьность импупьсов, !сф«рмированная в блоке 2 синхрониэзи.и, которая оп55 редепяет временнь1е гран.лць: передан— ных сигнапов, 0c«áebtë(Iñ тью ус гр«:- с гва является то., что реапизу= гая в и м процедура обработки одночастотных сигналов с о тноси тельной фа зо вой манип упя цией сводится к временной разбивке принимаемых копебаний дпитепьностью Т на с

N обрабатывае 1ых участков одинаковой

Тс

N длительности (— — — — и дапьнейшей с ве р тке сфо рмиро ванных N одно именных участков принимаемого и задержанного (опорного) сигналов. Цпя реапиэации этого в устройстве в каждой ветви обработки сигнапов имеетс (N+1)-вет— вей формирования опорных сигнапов, а время интегрирования интеграторов при обработке i-го участка принимаемого сигнапа,i=1,;1) выбрано равТ иым ! 11

Раба та устройства рассма тривае тся дпя cëó÷àÿ 11 3. При этом в каждой ветви обработки сигналов использует— ся (Я+1) =4 ветви формирования опорных сигнапов, а время интегрирования ( интеграторов 6 равно "(. = — . С це3 пью формирования отсчетов принимаемого сигнала на вьгходах интеграторов

6 в моменты времени, кратные (., на ! управляющие входы интеграторов 6 поступают синхроимпупьсы с вь!хода формироватепя 11 тактовых жлпульсов, фиг.2з). Зходным сигналом дпя формирователя !I тактовых импульсов служит последовательность импульсов с выхода блока 2 синхронизации фиг.2ж).

Поспедоватепьно(ть импульсов (фиг.2з), попученная в формироватепе

11 тактовых импульсов, испопьэуется также дпя формирования управляющих импульсов, с помощью которых в каждой ветви обработки сигнапов осуществпяется управление работой первых ключей

14 и вторых ключей 1 5. Формирование управпяюцих импупь(:ов осуществпяется с помощью оспедоватепьно соединенных делителя 12 частоты и блока 13 задержки.

Делитель 12 частоты предназначен дпя формирования синхроимпупьсов, c:tåäó!(röèê с периодом, равным (N+1) 4,=

7 + 4,, фиг. 2и) . Блок 3 задержки в рассматриваемом случае 11=3 имеет N+1= выходя . Сигналы на е го выходах изображены на фиг. 2в, г,д,е.

С выхода приемника 1 принимаемый сигнал на промежутсчной част«те одно— времени« поступает в две ветви «бра†ботки (игнапов на первые входы пере—! 453614 множителей 5. При этом на второй вход пе ремножителя 5 первой ве тв и об работки сигналов действует опорное колебание промежуточной частоты непосред5 ственно от генератора 3, а на второй вход перемножителя 5 второй ветви обработки сигналов — через фазовращатель 4, обеспечивающий сдвиг по фазе на 1 /2. На выходах интеграторов 6 в п 1с моменты регистрации кратные с

Ф

j 1,у формируются низкочастотные отсчеты принимаемого сигнала. На фиг. 2б условно показано, что кажцый входной 15 сигнал разбивается на три участка обработки длительностью

В каждой ветви обработки сигналов используется N+I ветвей формирования опорных сигналов (в рассматриваемом 20 случае четыре ветви формирования опорных сигналов). Поэтому при приеме конкретного участка сигнала в качестве опорного колебания используется одноименный участок предыдущего 25 сигнала.

Управление работой первых ключей

14, а также коммутация сигналов на выходах блоков 8 задержки вторыми ключами 15 30 (фиг. 2в-е) с выходов блока 13 эадержки.

С помощью сумматора 9, на входы которого поступают сигналы с выходов вторых перемножителей 7 и дополнительного интегратора 16, формируются результирующие отсчеты при» цчаемых сигналов. Синхронизация дополнительного интегратора 16 осуществляется сигналами (фиг . 2ж) с выхоца блока 2 синхронизации. В решающем блоке 1 0 фо рмируется имп уль с положительной или отрицательной полярности, в зависимости от знака входного отсчета) длительностью Тс.

40 ф о р м у л а и э о б р е т е н и я

Устройство приема сигналов с относительной фаэовой манипуляцией, содержащее последовательно соединенные прием- 50 ник и блок синхронизации, последовательно соединенные генератор и фазовращатель, две цепи обработки сигналов, содержащие последовательно соединенные первый перемножи тель, интегратор и второй перемножитель, а также цепь формирования опорного сигнала, состоящую иэ блока эацержки, сумматор и решающий блок, выход которого является выходом устройства, причем вход приемника является входом устройства, а его выход подключен к первым входам первых перемножителей обеих ветвей обработки сигналов, выход генератора соединен с вторым входом первого перемножителя первой цепи обработки сигналов, выход фаэовращателя подключен к второму входу первого перемножителя второй цепи обработки сигналов, а выходы вторых перемножителей соединены с входами сумматора, о т л и ч а ю щ е е с я тем, что, с целью повьппения помехоустойчивости в каналах с Времяселективными замираниями, введены последовательно соединенные формирователь тактовых импульсов, делитель частоты и блок задержки, дополнительные цепи формирования опорного напряжения, содержащие последовательно соединенные первый ключ, блок задержки и второй ключ, дополнительный интегратор, а в первые цепи формирования опорного сигнала — первый и второй ключи, причем выход первого ключа первой цепи формирования опорного сигнала в обеих цепях обработки сигналов подключен к входу блока задержки, выход которого соединен с первым входом второго ключа, выходы интеграторов обеих цепей обработки сигналов подключены к объединенным первым входам соответствующих первых ключей, а объединенные выходы вторых ключей соединены с вторыми входами соответствующих вторых перемножителей, выход сумматора подключен к первому входу дополнительного интегратора, выход которого соединен с входом решающего блока, выход блока синхронизации подключен к второму входу дополнительного интегратора, выход формирователя тактовых импульсов соединен с вторыми входами инте".— раторов, а выходы блока задержки подключены к вторым входам соответствующих первых и вторых ключей.! 453614 (:ос тав ите пь 1!. Котиков

1 ехред П. Олийнык

Редактор Г. Волкова

Корректор С. !!!екмар

Производственно-. оаэи -рафическое предпр ятие, г. У кгород, ул. Проек",ная, Заказ 7303/56 Тираж 627 10дГ! и снов

ВНИИГП1 Государственно с комитета по изобретениям и открытиям при ГКНТ Г(;ГР

1!3035, Москва, Ж-35, Раушская наб,,;. 4/5