Дешифратор на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в ЗУ на МДП-транзисторах в интегральном исполнении. Целью изобрет тения является расширение области применения за счет обеспечения статического режима работы. Поставленная цель достигается введением в каждую ячейку компенсирующего элемента, транзистора обнуления и передаточных транзисторов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 С 11 С 8/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР (21) 3592113/24-24 (22) 17. 05. 83 (46) 30. Ol . 89. Бюл, Р 4 (72) А. М. Копытов, Л. Н. Лисица и А. Г. Солод (53) 681. 327. 66 (088. 8) (56)- Патент США Р 4011549, кл. 340-173 СА, опублик. 1977.

Патент США У 371882.6, кл. 307-251, опублик. 1973.. (54) ДЕШИФРАТОР НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на

ИДП-транзисторах в интегральном исполнении для выработки сигнала на числовой шине накопителя при определенной комбинации входных адресных сигналов..

Цель изобретения — расширение области его применения путем обеспечения статического режима работы.

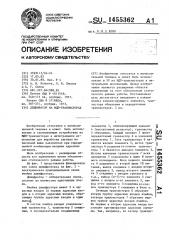

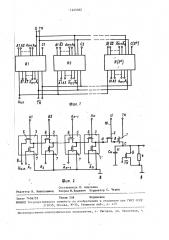

На фиг. 1 представлена функционал ная схема дешифратора; на фиг. 2— электрическая принципиальная схема ячейки дешифратора.

Дешифратор — избирательная схема, состоит из множества однотипных ячеек.

Ячейка дешифратора имеет 2 и адресных входов (n первых адресных входов и и вторых адресных входов, образующих группы адресных входов и один выход

В состав ячейки входит усилительный транзистор 1, транзистор 2 смещения, и последовательно соединенных

„.Я0„„1455362 А1 (57) Изобретение относится к вычислительной технике и может быть использовано в ЗУ на ИДП-транзисторах в интегральном исполнения. Целью изобрел тения является расширение области применения за счет обеспечения статического режима работы. Поставленная цель достигается введением в каждую ячейку компенсирующего элемента, транзистора обнуления и передаточных транзисторов. 2 ил. элементов 3, компенсирующий элемент

4 (высокоомный резистор), транзистор

5 обнуления. Каждый элемент 3 имеет передаточный транзистор 6 и ключевой транзистор 7. Сток транзистора 6 является входом элемента 3, исток транзистора 6 соединен со стоком транзистора 7 и является выходом элемента 3.

Истоки ключевых транзисторов 7 всех элементов 3 подключены к шине 8 нулевого потенциала. Вход первого элемента 9 подключен к второй шине 10 питания, выход соединен с входом второго элемента 3, выход второго элемента 3 соединен с входом третьего и т.д., выход (n-l)-го элемента 3 соединен с входом n-ro элемента 3, выход и-го элемента 3 соединен со стоком транзистора 2 смещения в узле а.

Затворы транзисторов 6 образуют вторую группу адресных входов ячейки, затворы транзисторов 7 образуют первую группу адресных входов ячейки.

На первые и вторые адресные входы поступают противофазные адресные сигналы. Так, например, на затвор транзис! 455362

4 ора 6 первого элемента поступает игнал Al а на затвор транзистора 7 того элемента — сигнал Al Исток транзистора смещения 2 соединен с

5 .затвором усилительного транзистора 1

1 узле Ь. Затвор транзистора 2 смещения соединен с источником напряжения

IJ = U „„- U -, где U — пороговое наряжение MgH-транзистора. На сток !и силительного транзистора 1 подается игнал возбуждения ТК (первый сигнал

ыборки). Исток транзистора l подклюен в узле с к нагрузочному элементу

1 (емкостной нагрузке С„, которой ожет быть строчная шина ПЗУ). На завор транзистора 5 подается сигнал

К (второй сигнал выборки), инверсый сигналу возбуждения ТК. Узел с вляется выходом ячейки. 20

Рассмотрим работу дешифратора. осле поступления определенной комбиации адресных сигналов на входы дератора осуществляется выбор опрееленной ячейки, сигнал на выходе ко- 25

Торой становится равным логической ице, на выходах всех остальных евыбранных ячеек — логическому нулю. ,редположим, s начальный момент вре ени, когда сигнал ТК равен логичес- Зц хому нулю, на дешифратор поступает акая комбинация адресных сигналов, ф которой все прямые адресные сигна . r равны логической единице, соответтвенно все инверсные сигналы равны ,огическому нулю. При указанной ком-! инации только в ячейке, приведенной фа фиг ° 2, оказываются открытыми все

)1ередаточные транзисторы 6 и закрытыЙи все ключевые транзисторы 7, эта 4О ячейка оказывается выбранной, а в

< дик, либо несколько передаточных ранзисторов 6 закрыты, так как на

llm затворы поступают сигналы логичес- 45 кого нуля,и либо один, либо несколько

<соответствующих ключевых.транзисторов 7 открыты сигналами логической единицы, поступившими на их затворы.

Щ результате в выбранной ячейке происходит предзаряд затвора транзисто1 а 1 до напряжения U — 2 U значи! ельно превышающего U от источника !

3„„ через открытые транзисторы 6 и транзистор 2. В остальных ячейках

:происходит обнуление затвора транзисгоров 1 по цепи: затвор, транзистор

2, открытые транзисторы 6, открытые транзисторы 7, шина 8, а также обнуление выходов элементов 3, к которому подключены открытые транзисторы 7.

Емкость С „ (емкость затвор-канал) в выбранной ячейке становится максимальной, в остальных ячейках — минимальной. Транзисторами 5, которые открыты сигналом ТК, равным логической единице, осуществляется обнуление всех нагрузочных элементов 11, т.е. всех строчных шин, подключенных к выходам ячеек дешифратора. При гоступлении сигнала ТК, равного логической единице, соответственно ТК равного логическому нулю, закрываются транзисторы 5, возбуждается выход выбранной ячейки, на нем формируется напряжение логической единицы, на выходах всех остальных ячеек сохраняется нулевой потенциал. Возбуждение выхода выбранной ячейки осуществляется в результате заряда Сн от источника сигнала TK через открытый тран с зис тор 1 Емкости Сэ C 3 С 3 ускО ряют процесс заряда строчных шин путем перекачки заряда на затвор транзистора 1 со стока, истока и канала этого транзистора. В результате в выбранной ячейке на затворе транзистора 1 формируется напряжение, значительно превышающее уровень сигнала ТК, что позволяет большими токами транзистора 1 быстро с малым фронтом нарастания зарядить емкость строчных шин до напряжения, близкого или равного уровню сигнала ТК.

Предлагаемый дешифратор может работать в статике.

Если сигнал ТК в течение длительного времени, т.е. в статике, будет сохранять значение, равное логической единице, будет неизменной комбинация адресных сигналов, поданных на дешифратор, то и на выходе дешифратора будут сохраняться установленные сигналы, т.е. на выходе выбранной ячейки будет сохраняться сигнал логической единицы, а на выходах всех остальных невыбранных ячеек будут сохраняться сигналы логического нуля. Возможность работы дешифратора в статическом режиме обусловлена следующим. Затвор усилительного транзистора I выбранной ячейки жестко соединен через транзистор 2 смещения и последовательно соединенные открытые передаточные транзисторы 6 с источ1455362 ником питания, а все ключевые транзисторы 7 этой ячейки закрыты. Таким образом, на затворе транзистора 1 выбранной ячейки будет поддерживаться .5 сигнал логической единицы, величина которого не менее U — 2 UT, сток этого транзистора соединен с источником сигнала ТК,соответственно на истоке этого транзистора, т.е. на выходе выбранной ячейки, будет поддерживаться сигнал логической единицы, уровень которого не менее U — 3 U . Затворы транзисторов всех невыбранных ячеек жестко соединены с шиной нулевого потенциала через открытые транзисторы 2 и открытые транзисторы 6 и

7, поэтому на затворах этих транзисторов будет поддерживаться сигнал логического нуля, транзисторы будут закрыты, соответственно на выходах невыбранных ячеек будет сохраняться сигнал логического нуля. Из-за наличия паразитных токов по выходам невыбранных ячеек в узлы с этих ячеек возмож- 25 но натекание заряда из-за паразитных токов, что может привести к появлению ложных сигналов логической единицы на выходах этих невыбранных ячеек. Для исключения этих ложных сигналов в де- дб шифратор введены компенсирующий элемент, соединяющий узел с с шиной нулевого потенциала, создавая путь для стекания заряда от узла с к шине нулевого потенциала, компенсируя таким образом паразитный заряд.

Дешифратор имеет низкую потребляемую мощность. Мощность таким дешифратором потребляется от источника U» 4g только в короткие промежутки времени переключения входных адресных .сигналов .

Формула из обретения

Дешифратор на МДП-транзисторах, содержащий ячейки, каждая из которых состоит из ключевых транзисторов, затворы которых являются первой группой адресных входов дешифратора, истоки подключены к шине нулевого потен-. циала дешифратора, усилительного транзистора, сток которого является первым входом выборки дешифратора, тран-: зистора смещения, затвор которого подключен к первой шине питания, а исток — к затвору усилительного транзистора, исток которого является выходом дешифратора, отличающийся тем, что, с целью расширения области применения путем обеспечения статического режима работы дешифратора, в каждую ячейку дешифратора введены компенсирующий элемент, выполненный на высокоомном резисторе, транзистор обнуления и последовательно соединенные передаточные транзисторы, затворы которых являются второй группой адресных входов дешифратора, сток первого передаточного транзистора подключен к второй шине питания, истоки каждого из передаточных транзисторов подключены к стокам соответствующих ключевых транзисторов, сток транзистора смещения подключен к истоку:последнего передаточного транзистора, затворы транзисторов обнуления являются вторым входом выборки дешифратора, истоки подключены к шине нулевого потенциала дешифратора и первому выводу соответствующего высокоомного резистора, второй вывод которого соединен с истоком усилительного транзистора, сток транзистора обнуления соединен с первым инверсным входом выборки дешифратора. — 1455362

0 ТК

ТИ

Составитель Л. Амусьева

Редактор Н. Киштулинец Техред М. Ходанич Корректор С- Черни

Заказ 7456/55 Тираж 558 Подписно е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4