Входное устройство схемы сравнения токов

Иллюстрации

Показать всеРеферат

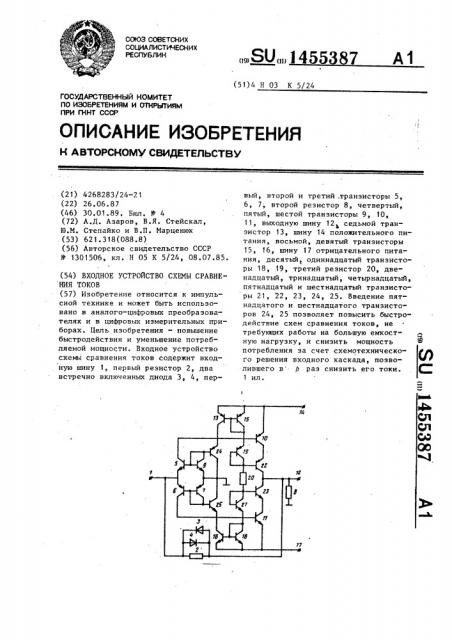

Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях и в цифровых измерительных приборах . Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности. Входное устройство схемь сравнения токов содержит входную шину 1, первый резистор 2, два встречно включенных диода 3, 4, первый , второй и третий .транзисторы 5, 6, 7; второй резистор 8, четвертый, пятый, шестой транзисторы 9, 10, 11, выходную шину 12 седьмой транзистор 13, шину 14 положительного питания , восьмой, девятый транзисторы 15, 16, шину 17 отрицательного питания , десятыйj одиннадцатый транзисторы 18, 19, третий резистор 20, двенадцатый , тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый транзисторы 21, 22, 23, 24, 25. Введение пятнадцатого и шестнадцатого транзисторов 24, 25 позволяет повысить быстродействие схем сравнения токов, не требукяцих работы на большую емкостную нагрузку, и снизить мощность потребления за счет схемотехнического решения входного каскада, позволившего В /5 раз снизить его токио 1 ил. с ф (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (111 (51)4 Н 03 К 5/24

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHO9IY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (2i) 4268283/24-21 (22) 26.06.87 (46) 30.01.89. Бюл. Ф 4 (72) А.Д. Азаров, В.Я. Стейскал, 10.М. Степайко и В.П. Марценюк (53) 621.318(088.8) (56) Авторское свидетельство СССР

1Ф 1301506, кл. Н 05 К 5/24, 08.07.85. (54) ВХОДНОЕ УСТРОЙСТВО СХЕМЫ СРАВНЕНИЯ ТОКОВ (57) Изобретение относится к импульсной технике и может быть использовано в аналого-цифровых преобразователях и в цифровых измерительных приборах. Цель изобретения — повышение быстродействия и уменьшение потребляемой мощности. Входное устройство схемы сравнения токов содержит входную шину 1, первый резистор 2, два встречно включенных диода 3, 4, первый, второй и третий, транзисторы 5, 6, 7, второй резистор 8, четвертый, пятый, шестой транзисторы 9, 10, 11, выходную шину 12 седьмой транзистор 13, шину 14 положительного питания, восьмой, девятый транзисторы

15, 16, шину 17 отрицательного питания, десятый, одиннадцатый транзисторы 18, 19, третий резистор 20, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый транзисторы 21, 22, 23, 24, 25. Введение пятнадцатого и шестнадцатого транзисторов 24, 25 позволяет повысить быстродействие схем сравнения токов, не требующих работы на большую емкостную нагрузку, и снизить мощность потребления за счет схемотехнического решения входного каскада, позволившего в р раз снизить его токи.

1 ил °

1455387

Изобретение относится к импульсной ехнике и может быть использовано в палого-цифровых преобразователях и цифровых измерительных приборах.

Целью изобретения является повыШение быстродействия и уменьшение потребляемой мощности.

На чертеже представлена принци1 иальная схема входного устройства хемы сравнения токов.

Входное устройство схемы сравения; токов содержит входную шину к которой подключены первые выводы! ервого резистора 2 и двух встречно ключенных, диодов 3, 4, эмиттер перoro 5 и эмиттер второго 6 транэисто" ов, база второго из которых соедиена с базой и коллектором третьего ранзистора 7, эмиттер которого соеинен с шиной нулевого потенциала, первым выводом второго резистора 8 с эмиттером четвертого транзистора 9, коллектор и база которого соеДинены между собой и с базой первого транзистора 5, коллектор которого соединен с базой пятого транзистора

10, а коллектор второго транзистора

6 соединен с базой шестого транзистоа 11, выходная шина 12 соединена с торыми выводами первого и второго езисторов 2, 8 и двух встречно вклюенных диодов 3, 4, эмиттер седьмого транзистора 13 соединен с шиной 14 оложительного питания и с эмиттером восьмого .транзистора 15, коллектор и база которого соединены между собой и с базой седьмого транзистора 13, эмиттер девятого транзистора 16 соединен с шиной 17 отрицательного пита-, „40 ния и с эмиттером десятого транзистора 18, коллектор и база которого соединены между собой и с базой девятого транзистора 16. Коллектор восьмого

45 транзистора 15 соединен с эмиттером одиннадцатого транзистора 19, база и коллектор которого соединены между собой и подключены через третий резистор 20 к коллектору и базе двенадцатого транзистора 21 и непосредствен50 но к базе тринадцатого транзистора 22, коллектором соединенного с коллектором четырнадцатого транзистора 23, при этом база пятнадцатого транзистора 24 соединена с коллектором четвер-55 того транзистора 9, а коллектор — с коллектором шестнадцатого транзистора 5

Устройство работает следующим образом.

При включении питания через третий резистор 20 и транзисторы 15, 21, !

8, 19, включенные в днодном режиме, протекает ток смещения 1 „,:

+ t5 19 2i 18

U zzur +U fzgy -|,U 63 +П 6 +U 6g +О 69)

СМ де П „„, и П„„, напряжения питания положительно". го и отрицательного источника питания соответственно; zs

Пбэ в U69 э

6у> 6Э вЂ” напряжение базаэмиттер транзисторов 15> 19> 21>

18;

К вЂ” значение резистора 20.

Считая, что U „ = Uzzè, H Vg всех транзисторов равны между собой, формулу можно переписать в следующем виде:

211 пит 4U Бз

«4Ъ» см R LD

Входное устройство необходимо реализовать на парах транзисторов, выполненных в интегральном исполнении. Это позволяет коэффициент отражения токовых,зеркал на транзисторах 13, 15, 16, 18, 5, 9, 6, 7 сделать практически равным единице. Следовательно, через транзисторы 13, 16, являющиеся источником и токоотводом тока соответственно, будет протекать ток, также равный I . Такой же ток будет про" текать через транзисторы 24, 25, включенные по схеме с общей базой.

Базовый ток этих транзисторов, в р раз меньший Т,„, протекает через транзисторы 9, 7, соединенные в диодном включении. Датчики токовых зеркал на трарзисторах 9, 5 и 7, 6 имеют коэффициент отражения, равный единице.

Следовательно, через входной каскад на транзисторах 5 и 6 будет протекать ток, равный I, /, который, в свою очередь, является базовым током транзисторов 10, 11,являющихся вторыми транзисторами интегральных пар, первыми транзисторами которых являются транзисторы 24, 25 соответственно.

3 14553

Значит, через транзисторы 10, 11 будет протекать ток, практически равный I . Транзисторы 22, 23 вклю- чены по- схеме с общей базой, и через них протекает ток транзисторов 10, 11, равный I „, При входном токе (BI „), равном нулю, в общем случае на выходе устройства будет протекать ток сдвига (I, ), определяемый формулой: т м I

I. = +» — 7 сд мин 1

1 + б

15 где p„ „ — минимальное значение коэффициента р транзисторов одной из проводимостей;

d p — относительный коэффициент рассогласования коэффици 20 ентов р транзисторов разной проводимости, равный

Рмакс РМ1(к

М » р / мьн

25 где р „ вЂ” максимальное значение коэффициента р транзисторов одной из проводимостей.

При равенстве значений коэффициенР 3 т.е ° (мин = Рмйкс 1 по лучим I = О.

Учитывая, что схема симметрична относительно шины нулевого потенци- 35 ала, рассмотрим работу только одной половины схемы, например нижней, при втекающем входном токе йТ „ 1 О.

g данном случае первый каскад на транзисторе 6, включенный по схеме 40 с общей базой, создает усиление по току, равное Ы . Вторым усилительным каскадом является схема с общим эмиттером на транзисторе 11 с коэффициентом усиления по току, равным

Третьим каскадом предлагаемого т„ устройства является схема с общей базой на транзисторе 23 с коэффициентом усиления по току, равным работающим на резистор 8, являющим- 50 ся нагрузкой.

Работа второй половины аналогична рассмотренной, только с противоположеными по знаку приращениями.

55 формула изобретения

Входное устройство схемы сравнения токов, содержащее три резистора, два диода, четырнадцать транзисторов, шину нулевого потенциала, шину положительного питания, шину отрицательного питания, выходную шину, входную шину, к которой подключены первые выводы первого резистора и двух встречно включенных диодов, эмиттер первого и эмиттер второго транзисторов, база второго из которых соединена с базой и коллектором третьего транзистора, эмиттер которого соединен с шиной нулевого потенциала, с первым выводом второго резистора и эмиттером четвертого транзистора, коллектор и база которого соединены между собой и базой первого .транзистора, коллектор которого соединен с базой пятого транзистора, а коллектор второго транзистора соединен с базой шестого транзистора, выходная шина соединена с вторыми выводами первого и второго резистора и двух встречно включенных диодов, эмиттер седьмого транзистора соединен с шиной положительного питания и эмиттером восьмого транзистора, коллектор и база которого соединены между собой и с базой седьмого транзистора, эмиттер девятого транзистора соединен с шиной отрицательного питания и эмиттером десятого транзистора, коллектор и база которого соединены между собой и с базой девятого транзистора, о т л и ч а—

I ю щ е е с я тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, в него введены пятнадцатый.и шестнадцатый транзисторы, коллекторы которых соединены между собой и с шиной нулевого потенциала, база пятнадцатого транзистора соединена с коллектором четвертого, а эмиттер — с коллектором седьмого транзистора, база шестнадцатого соединена с коллектором третьего транзистора, а эмиттер — с коллектором девятого транзистора, коллектор восьмого транзистора соединен с эмиттером одиннадцатого транзистора, база и коллектор которого соединены между собой, с базой тринадцатого транзистора и первым выводом третьего резистора, второй вывод которого соединен с базой четырнадцатого транзистора, с коллектором и базой двенадцатого транзистора, эмиттер которого соединен с коллектором десятого транзистора, эмиттер пятого транзистора

Составитель Н . Маркин

Техред М.Ходаиич: Корректор Н. Король

Редактор М. Циткина

Заказ 7459/57 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Цроизводственно-полиграфическое предприятие, r Ужгород, ул. Проектная, 4

5 1455387 6 соединен с шиной положительного пита- змиттер которого соединен с коллек ния, а коллектор с эмиттером тринад- тором шестого транзистора, эмиттер ,цатого транзистора, коллектор кото- которого соединен с шиной отрицательрого соединен с выходной шиной и кол ного питания. ,лектором четырнадцатого транзистора,